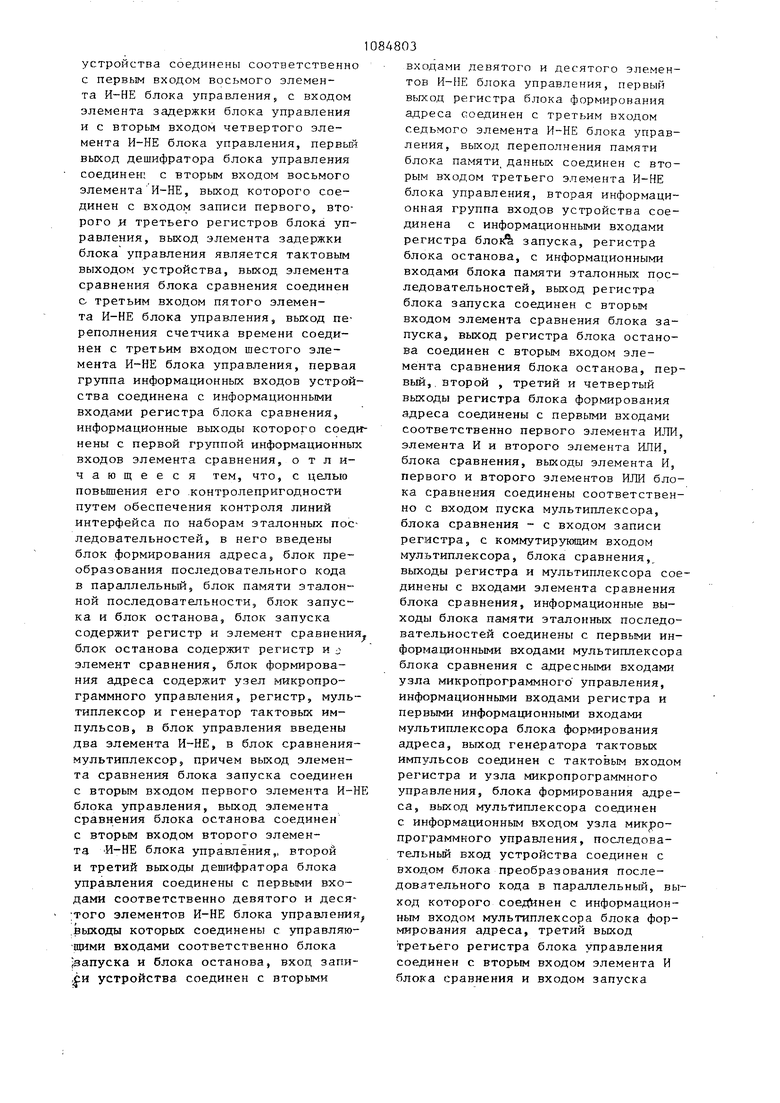

устройства соединены соответственно с первым входом восьмого элемента И-НЕ блока управления с входом элемента задержки блока управления и с вторым входом четвертого элемента И-НЕ блока управления, первый выход дешифратора блока управления соединен; с вторым входом восьмого элементаИ-НЕ, выход которого соединен с входом записи первого, второго 1 третьего регистров блока управления, выход элемента задержки блока управления является тактовым выходом устройства, выход элемента сравнения блока сравнения соединен о третьим входом пятого элемента И-НЕ блока управления, выход переполнения счетчика времени соединен с третьим входом шестого элемента И-НЕ блока управления, первая группа информационных входов устройства соединена с информационными входами регистра блока сравнения, информационные выходы которого соеди нены с первой группой информационных входов элемента сравнения, о т л ичающееся тем, что, с целью повышения его .контролепригодности путем обеспечения контроля линий интерфейса по наборам эталонных последовательностей, в него введены блок формирования адреса блок преобразования последовательного кода в параллельньш, блок памяти эталонной последовательности, блок запуска и блок останова, блок запуска содержит регистр и элемеят сравнения блок останова содержит регистр и ;; элемент сравнения, блок формирования адреса содержит узел микропрограммного управления, регистр, мультиплексор и генератор тактовых импульсов, в блок управления введены два элемента И-НЕ, в блок сравнениямультиплексор, причем выход элемента сравнения блока запуска соединен с вторым входом первого элемента И-Н блока управления, выход элемента сравнения блока останова соединен с вторым входом второго элемента И-НЕ блока управления,, второй и третий выходы дешифратора блока управления соединены с первыми входами соответственно девятого и десятого элементов И-НЕ блока управления .выходы которых соединены с управляющими входами соответственно блока запуска и блока останова, вход запи,си устройства соединен с вторыми

входами девятого и десятого элементов И-НЕ блока управления, первый вьгкод регистра блока формирования адреса соединен с третьим входом седьмого элемента И-НЕ блока управления, выход переполнения памяти блока памяти данных соединен с вторым входом третьего элемента И-НЕ блока управления, вторая информационная группа входов устройства соединена с информационными входами регистра блок% запуска, регистра блока останова, с информационными входами блока памяти эталонных последовательностей, выход регистра блока запуска соединен с вторым входом элемента сравнения блока запуска, выход регистра блока останова соединен с вторьм входом элемента сравнения блока останова, первый,, второй , третий и четвертый выходы регистра блока формирования адреса соединены с первыми входами соответственно первого элемента ИЛИ элемента И и второго элемента ИЛИ, блока сравнения, выходы элемента И, первого и второго элементов ИЛИ блока сравнения соединены соответственно с входом пуска мультиплексора, блока сравнения - с входом записи регистра, с коммутирующим входом мультиплексора, блока сравнения,, выходы регистра и мультиплексора содинены с входами элемента сравнения блока сравнения, информационные выходы блока памяти эталонных последовательностей соединены с первыми информационными входами мультиплексор блока сравнения с адресными входами узла микропрограммного управления, информационными входами регистра и nepJ3b MH информационными входами мультиплексора блока формирования адреса, выход генератора тактовых импульсов соединен с тактовым входом регистра и узла микропрограммного управления, блока формирования адреса, выхо.д мультиплексора соединен с информационным входом узла микропрограммного управления, последовательньй вход устройства соединен с входом блока преобразования последовательного кода в параллельный, выход которого соединен с информационным входом мультиплексора блока формирования адреса, третий выход

третьего регистра блока управления соед:инен с вторым входом элемента И блока сравнения и входом запуска

микропрограммного управления блока формирования адреса, информационный выход узла микропрограммного управления, блока формирования адреса соединен с адресным входом блока памяти эталонной последовательности.

выход элемента сравнения блока сравнения соединен с входом управления коммутацией мультиплексора блока формирования адреса,вход устройства соединен с вторым входом чтения блока памяти эталонных последовательностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| Устройство для контроля параллельных микропроцессорных интерфейсов | 1982 |

|

SU1040489A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И РЕГИСТРАЦШ АСИНХРОННЫХ СИГНАЛОВ ИНТЕРФЕЙСА, содержащее блок сравнения, блок памяти данных, счетчик времени и блок управления, причем первая группа информационных входов устройства соединена с первой группой информационных входов блока сравнения и блока памяти данных, выход которого является информационным выходом устройства, информационный выход счетчика времени соединен с второй группой информационных входов блока памяти данных, блок управления содержит первьй, второй и третий регистры, дешифратор, триггер, восемь элементов И-НЕ, три элемента ИЛИ-НЕ, одновибратор и элемент задержки, а блок сравнения содержит два элемента ИЛИ, элемент И, регистр и элемент сравнения, причем вторая группа информационных входов устройства соединена с информационными входами первого, второго и третьего регистров, блока управления, первый и второй выходы первого регистра соединены с первыми входами соответственно первого элемента 1|ЛИ-НЕ и первого элемента И-НЕ, выход которого соединен с первьм установочным входом триггера, первый, второй и третий выходы второго регистра соединены соответственно с первыми входами второго, третьего и четвертого элементов И-НЕ, выходы которых соединены соответственно с первьм, вторым и третьим входами второго элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с установочным входом первого регистра, вторым установочным входом триггера и является выходом сигнала прерывания устройства, первый, второй и третий с 9 выходы третьего регистра соединены с первыми входами соответственно пя(Л того, шестого и седьмого элементов И-НЕ, выходы которых соединены с соответственно с первым, вторым и третьим входами третьего элемента ИЛИ-НЕ, выходы пятого и шестого элементов И-НЕ и первый выход третьего регистра блока управления соединены соответственно с первьм входом первого элемента ИЖ блока сравнеСХ) ния, с входом эапуска счетчика вре42а мени и с первьм входом второго эле00 мента ИЛИ блока сравнения, выход О третьего элемента ИЛИ-НЕ блока управсо ления через одновибратор соединен с входом эаписи блока памяти данных, выход первого элемента ИЛИ-НЕ блока управления соединен с вторыми входами пятого, шестого и седьмого элементов И-НЕ, первый, второй и третий адресные входы устройства соединены соответственно с первым, вторым и третьим входами дешифратора, Яблока управления, входы записи запроса информации и окончания записи

Изобретение относится к вычислительной технике и может найти применение в многомашинных вычислительных комплексах, сетях электронновычислительных машин и отдельных ЭВМ для контроля различных интерфейсов, отдельных узлов и процедур обмена информацией в системах повышенной надежности.

Известно устройство для контроля и регистрации, содержащее коммутатор группу управляющих триггеров, информатор, дешифратор и комбинационную логику РЛ .

Недостаток устройства - невозможность контроля и регистрации в памяти состояния шин интерфейса в раличные моменты времени.

Наиболее близким по технической сущности к изобретению является уст ройство для контроля и регистрации асинхронных сигналов, содержащее блок сопряжения, блок сравнения, блок управления, блок памяти данных, таймер 2 .

Недостатками известного устройства являются невозможность оперативного контроля и анализа нарушений (сбойных ситуаций) последовательностей контролируемого интерфейса, а также невозможность работы с последовательными интерфейсами.

Целью изобретения является повышение контролепригодности устройства путем обеспечения контроля последовательностей кодов на интерфейсе по наборам эталонных последовательностей, а также работа с последовательными интерфейсами.

Поставленная цель достигается тем, что в устройство для контроля и регистрации асинхронных,сигналов, интерфейса, содержащее блок сравнения, блок памяти данных, счетчик времени и блок управления, причем первая группа информационных входов устройства соединена с первой группой информационных входов блока сравнени и блока памяти данных, выход которого является информационным выходом устройства, информационный выход счетчика времени соединен с второй группой информационных входов блока памяти данных,блок управления содержит первый, второй и третий регистры, дешифратор, триггер, восемь элементов И-НЕ, три элемента ИЛИ-НЕ, одновибратор и элемент задержки, а блок сравнения содержит два элемента ИЛИ, элемент И, регистр и элемент сравнения, причем вторая группа информационных входов устройства соединена с информационными входами первого, второго и третьего регистров, блока управления, первый и второй выходы пepвo o регистра соединены с первыми входами соответственно первого элемента ИЛИ-НЕ и первого элемента И-НЕ, выход которого соединен с первым установочным входом триггера, первый, второй и третий выходы второго регистра соединены соответственно с первыми входами второго, третьего и четвертого элементов И-НЕ, выходы которьк соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с установочньм входом первого регистра, вторым установочным входом триггера и является выходом сигнала прерывания устройства, первый, второй и третий выходы третьего регистра соединены с первыми входами соответствующего пятого, шестого и седьмого элементов И-НЕ, выходы которых соединены соответственно с первю, вторым и третьим входами третьего элемента ИЛИ-НЕ, выходы пятого и шестого элементов И-НЕ и первый выход треть го регистра блока управления соединены соответственно с первым входом первого элемента ИЛИ блока сравнени с входом запуска счетчика времени и с первым входом второго элемента ИЛИ блока сравнения, выход треть го элемента ИЛИ-НЕ блока управления через одновибратор соединен с вход записи блока памяти данных, выход первого элемента ИЛИ-НЕ блока упра ления соединен с вторыми входами пятого, шестого и седьмого элементов И-НЕ, первый, второй и третий адресные входы устройства соединен соответственно с первым, вторым и третьим входами дешифратора, блока управления, входы записи запроса информации и окончании записи устройства соединены соответственно с первым входом восьмого элемента Иблока управления, с входом элемент задержки блока управления и с вторы входом четвертого элемента И-НЕ бло ка управления, первый выход дешифратора блока управления соединен с вторым входом восьмого элемента И-Н выход которого соединен с входом за писи первого, второго и третьего регистров блока управления, выход элемента задержки блока управления является тактовым выходом устройства, выход элемента сравнения блока сравнения соединен с третьим входом пятого элемента И-НЕ блока управления, выход переполнения счетчика времени соединен с третьим входом шестого элемента И-НЕ блока управления, первая группа информационных входов устройства соединена с инфор мационными входами регистра блока сравнения, информационные выходы которого соединены с первой группой информационных входов элемента срав нения, введены блок формирования ад реса, блок преобразования последова тельного кода в параллельный, блок памяти эталонной последовательности блок запуска и блок останова, запуска содержит регистр и элемент сравнения, блок останова содержит регистр и элемент сравнения, блок формирования адреса содержит узел микропрограммного управления, регистр, мультиплексор и генератор тактовых импульсов, в блок управления введены два элемента И-НЕ, в блок сравнения - мультиплексор, причем выход элемента сравнения блока запуска соединен с вторым входом первого элемента И-НЕ блока управления, выход элемента сравнения блока останова соединен с вторым входом второго элемента И-НЕ блока управt ления, второй и третий выходы дешифратора блока управления соединены с первыми входами соответственно девятого и десятого элементов И-НЕ блока управлв5111Я, выходы которых соединены с управляющими входами соответственно блока запуска и блока останова, вход записи устройства соединен с вторыми входами девятого и десятого элементов И-НЕ блока управления, первьш выход регистра блока формирования адреса соединен с третьим входом седьмого элемента И-НЕ блока управления, выход переполнения памяти блока памяти данных соединен с вторым входом третьего элемента И-НЕ блока управления, вторая информационная группа входов устройства соединена с информационными входами регистра блока запуска, регистра блока останова, с информационными входами блока памяти эталонных последовательностей, выход регистра блока запуска соединен с вторьм входом элемента сравнения блока запуска, выход регистра блока останова соединен с вторым входом элемента сравнения блока останова, первьй, второй третий и четвертый выходы регистра блока формирования адреса соединены с первыми входами соответственно первого элемента ИЛИ, элемента И и второго элемента ИЛИ, блока сравнения, выходы элемента И, первого и второго элементов ИЛИ блока сравнения соединены соответственно с входом пуска мультиплексора, блока сравнения - с входом записи регистра, с коммутирующим входом мультиплексора, блока сравнения, выходы регистра и мультиплексора соединены с входами элемента сравнения блока сравнения, информационные выходы блока памяти эталонных последовательностей соединены с первыми информационными входами мультиплексора блока сравнения с адресными входами узла микропрограммного управления, информационными входами регистра и первыми информационными входами мультиплексора блока формирования адреса, выход генератора тактовых

J

импульсов соецилен с тактовым входом регистра и узла MUKponporpaNfMnoго управления, блока формнро1 ания адреса, выход мультиплексора соединен с информационным входом узла микропрограммного управления, последовательный вход устройства соединен с входом блока преобразования последовательного кода в параллельный, выход которого соединен с информационным входом мультиплексора блока формирования адреса, третий выход третьего регистра блока управления соединен с вторым входом элемента И блока сравнения и входом запуска узла микропрограммного управления блока формирования адреса, информационный выход узла микропрограммного управления, блока формирования адреса соединен с адресным входом блока памяти эталонной последовательности, выход элемента сравнения блока сравнения соединен с входом управления коммутацией мультиплексора блока формирования адреса, вход устройства соединен с вторым входом чтения блока памяти эталонных последовательностей.

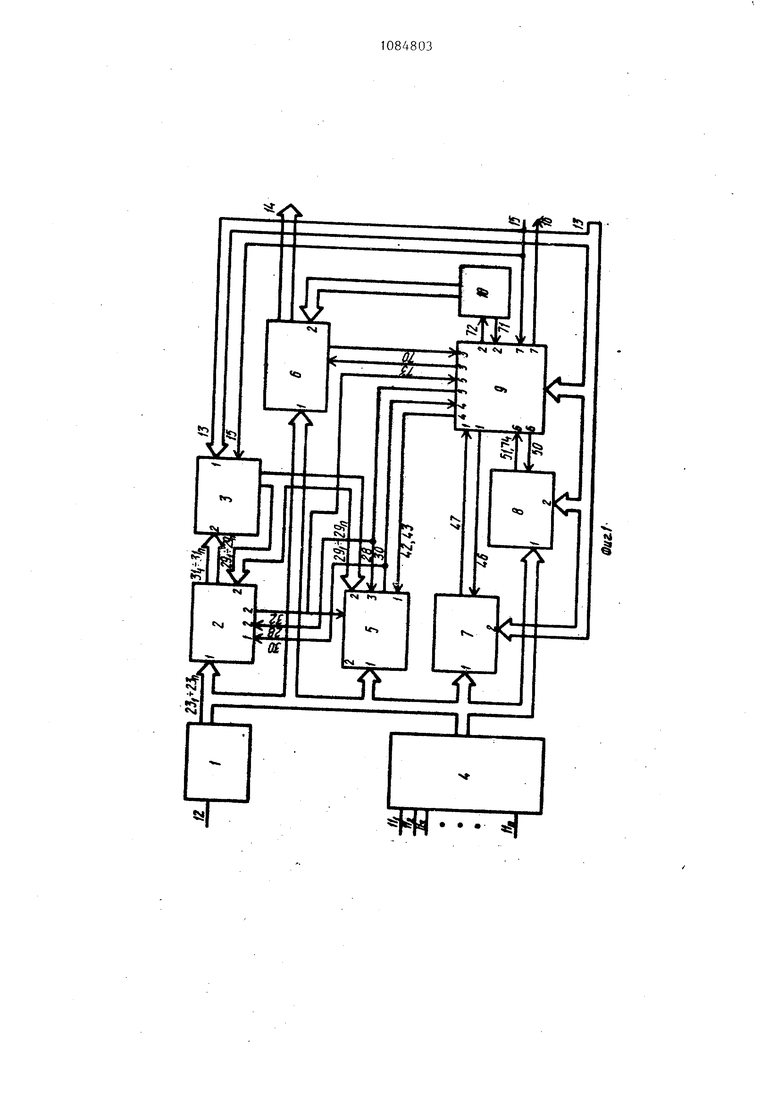

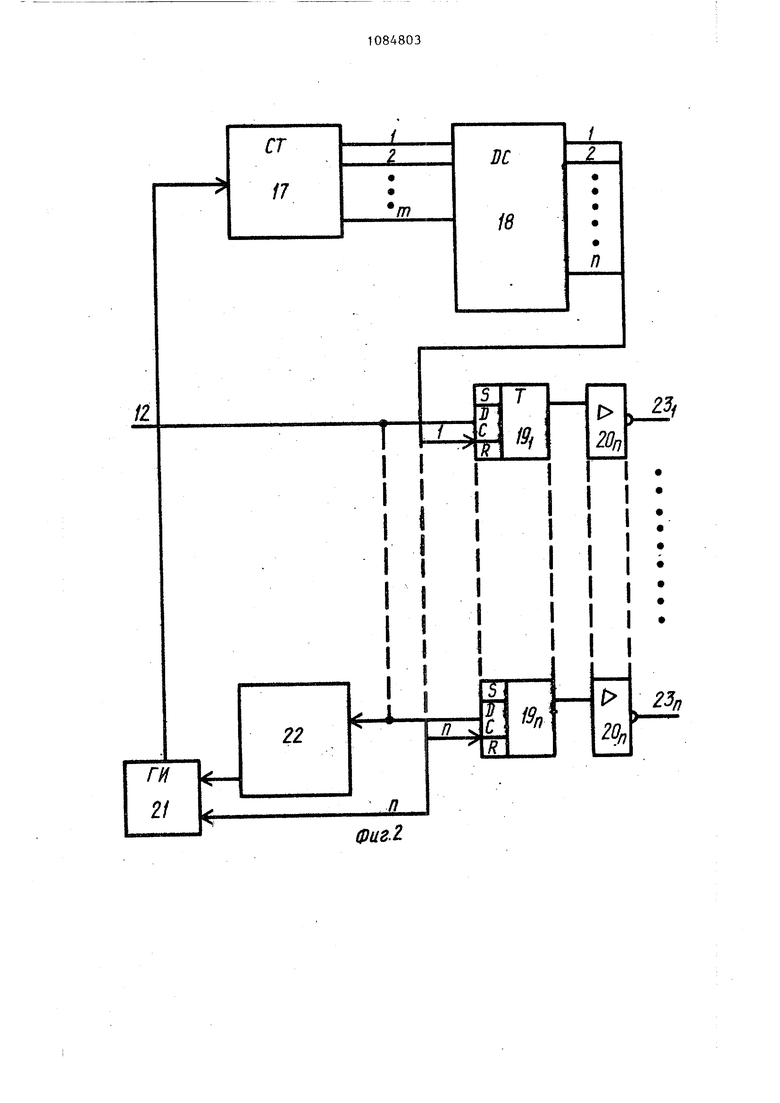

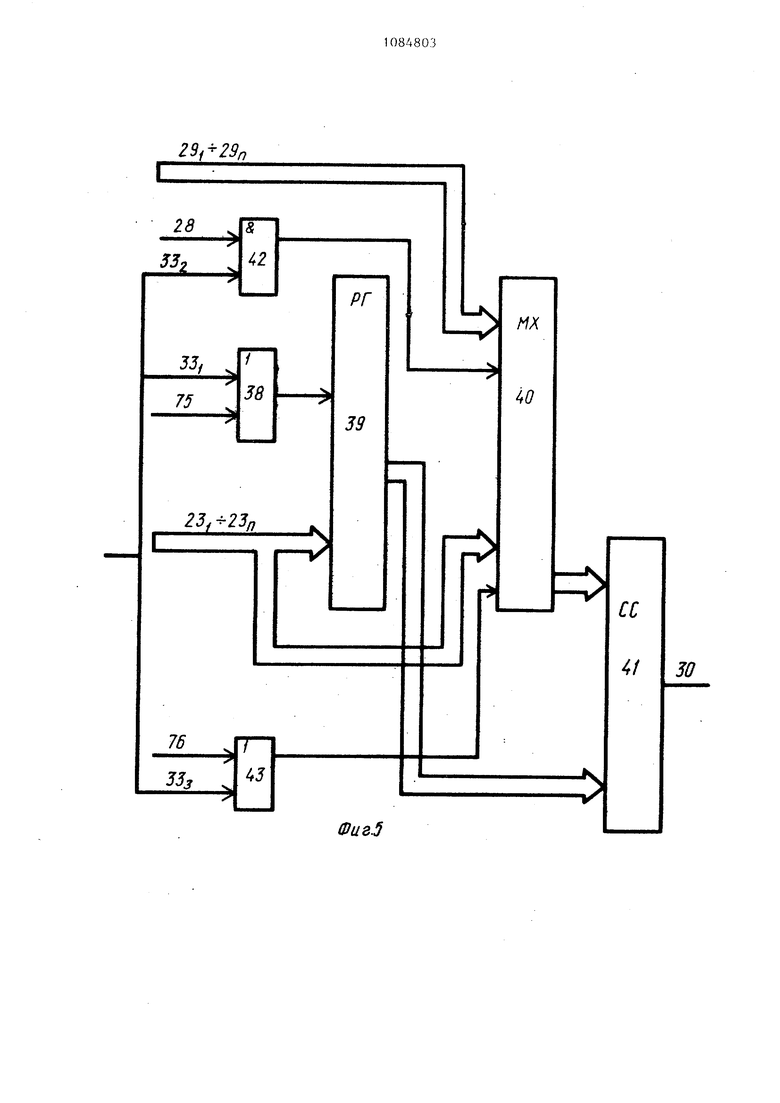

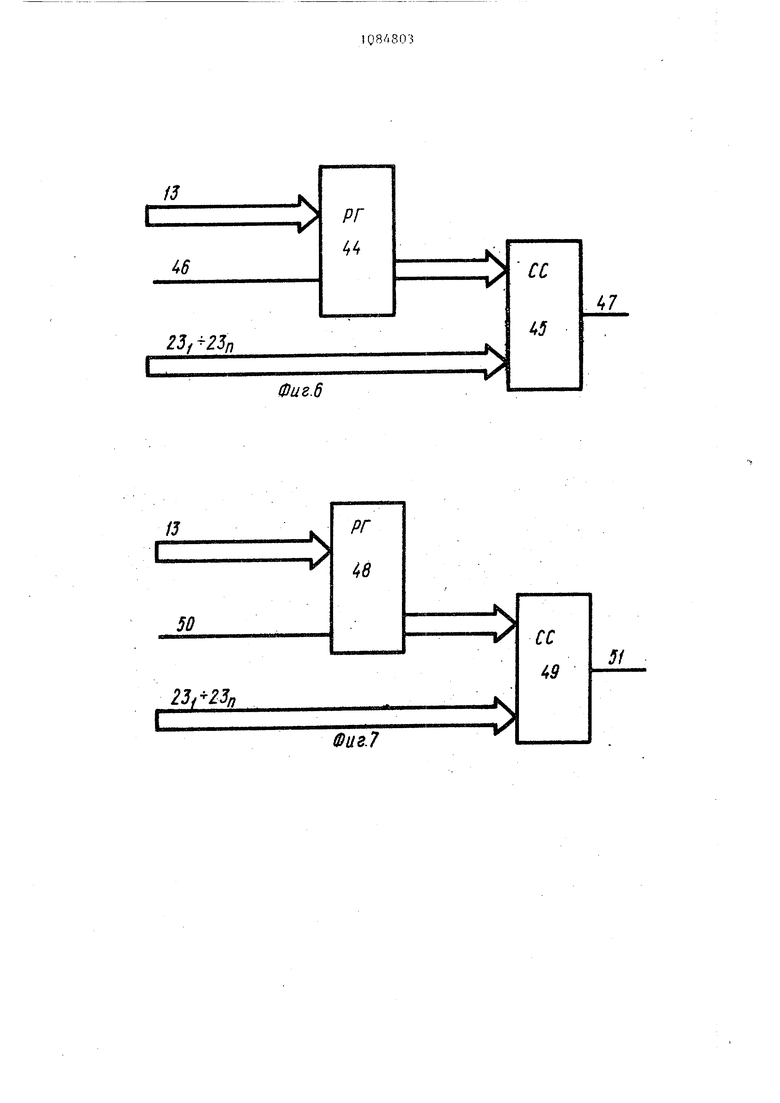

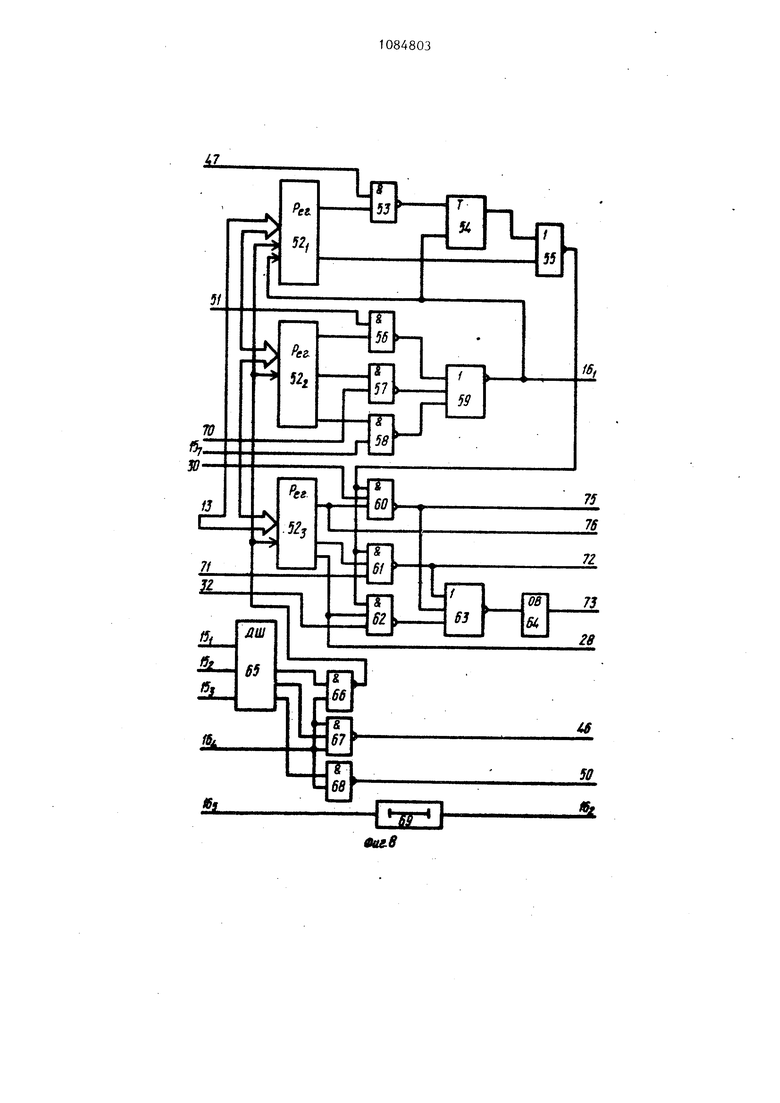

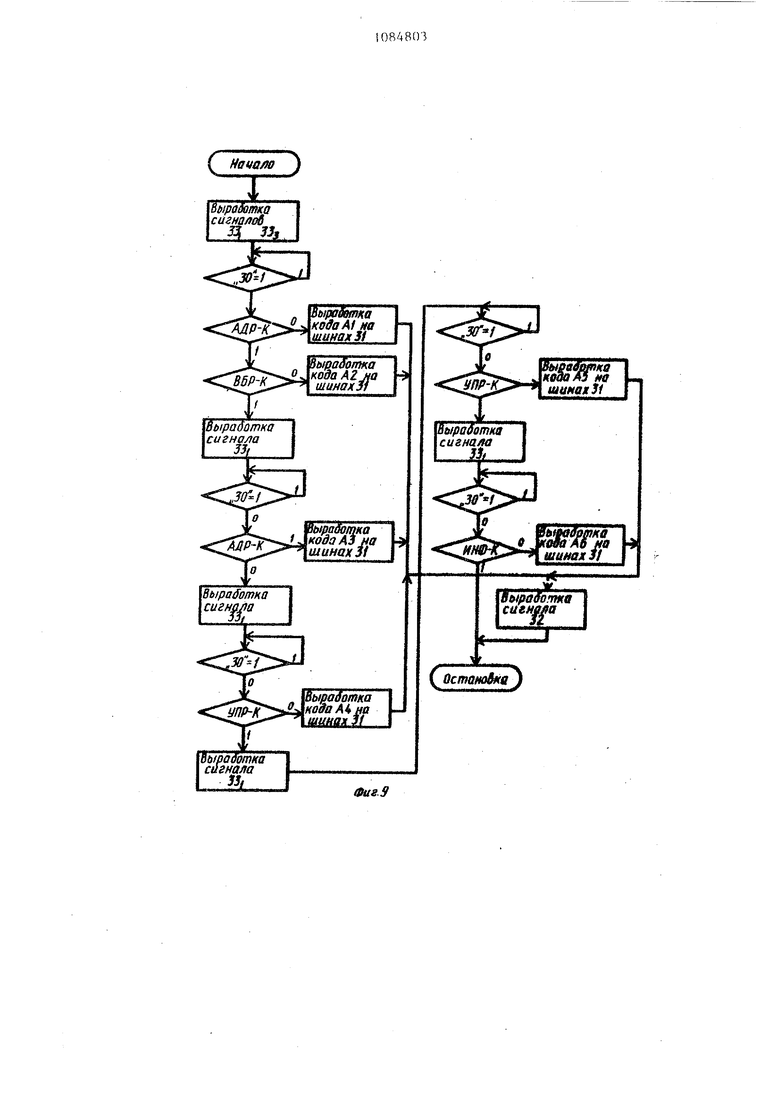

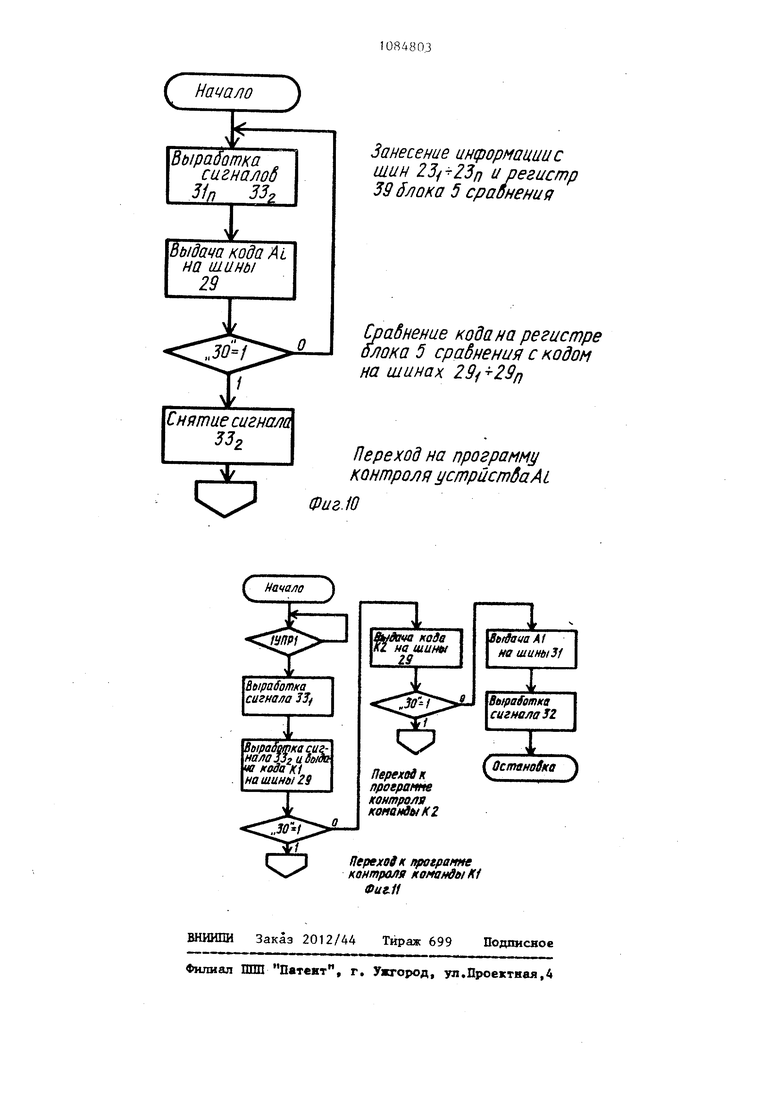

На фиг. 1 представлена структурная схема устройства для контроля и регистрации асинхронных сигналов интерфейса; на фиг. 2 -блока преобразования параллельного кода в последовательный на фиг. 3 - блок формирования адреса, на фиг. 4 - блок памяти эталонной последовательности на фиг. 5 - блок сравнения;на фиг.6блок запуска; на фиг. 7 - блок останова;, на фиг. 8 - блок управления; -на фиг. 9 - программа анализа oneраций ввода-вьгеода внешнего устройства;, на фиг. 10 - схема выборочной проверки операции ввода-вьшода внешнего устройства; на фиг. t1 - начало программы контроля интерфейса ИРПР.

Устройство содержит блок 1 преобразования параллельного кода в последовательный, блок 2 формирования адреса, блок 3 памяти эталонной последовательности, блок 4 сравнения, блок 5 памяти данных, блок 6 запуска, блок 7 останова, блок 8 управления, счетчик 9 времени, линии 10 lOjn и 11 контролируемьк интерфейсов, информационные линии 12 приема, информационные линии 13 ввщачи, управляющую линию 14 приема, управляющую линию 15 вьщач и.

Блок 1 преобрязонаиия пар;иыс-Л1 го кода в последовательный (фиг.2) предназначен для преобразования последовательных кодов в параллельные. Блок 1 преобразования параллельного кода в последовательный по входу связан с линией 11 контролируемого интерфейса, по выходу - с первым информационным входом блока 2 формирования адреса, первым информационным входом блока 5 памяти данных , первым информационным входом блока 4 сравнения, первым информационным входом блока 6 запуска, первым информационным входом блока 7 останова. В состав блока 1 преобразования параллельного кода в последовательный входят: счетчик 16, выходы которого 17j-l7f) соединены с входами дешифратора 18,D -триггеры 19yj + 9п логические элементы И-НЕ 20.-20, генератор 21 импульсов, выделитель 22 стартовой посыпки. По каждой стартовой посылке, вьщеляемой элементом 22, запускается тактовый генератор 21 импульсов. Импульсы модифицируют содержание счетчика 16, выходы 7|,-17|,д которого подаются на вход дешифратора 18, импульсы с выходом дешифратора 18 осуществляют последовательное занесение информации с линии 11 контролируемого интерфейса на триггеры 19.19jy, разворачивая таким образом последовательньй код в параллельный

Блок 2 формирования адреса (фиг.З обеспечивает взаимодействие блока 4 сравнения с блоком 3 памяти эталонной последовательности. По первому информационному входу блока 2 формирования адреса связан с выходом блока 1 преобразования параллельного кода в последовательный, по второму информационному входу - с блоком 3 памяти эталонной последовательности по информационному вькоду - с вторым информационным входом блока 3 памяти

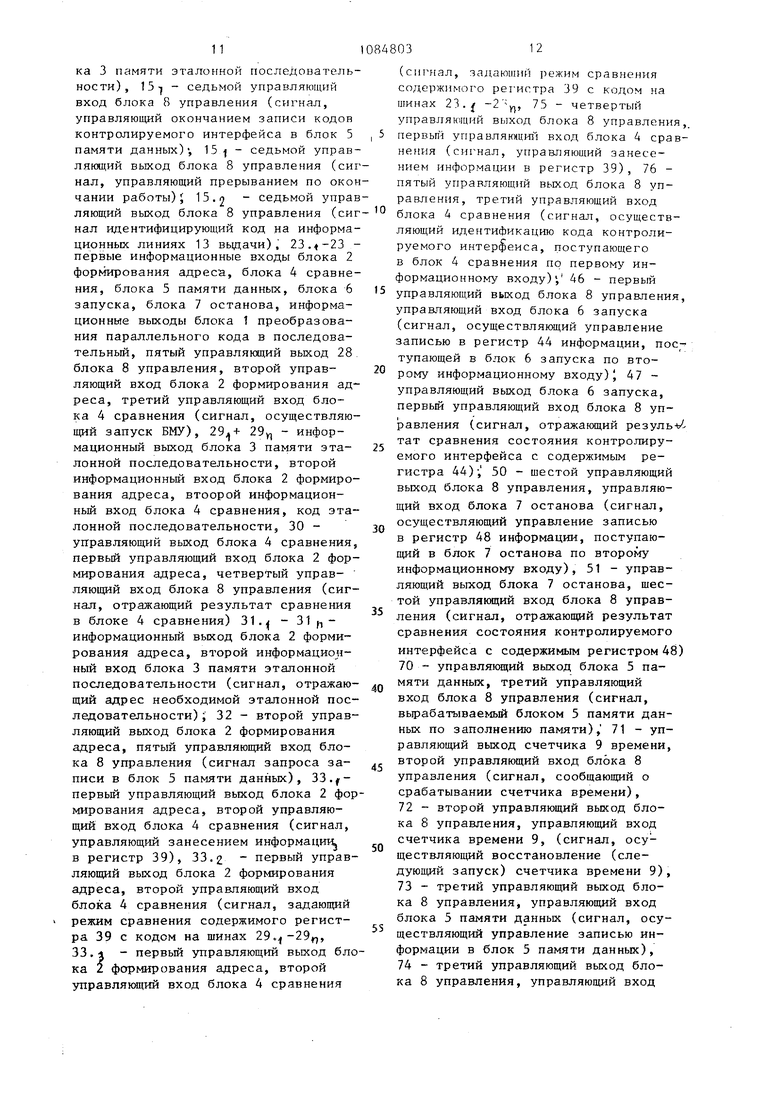

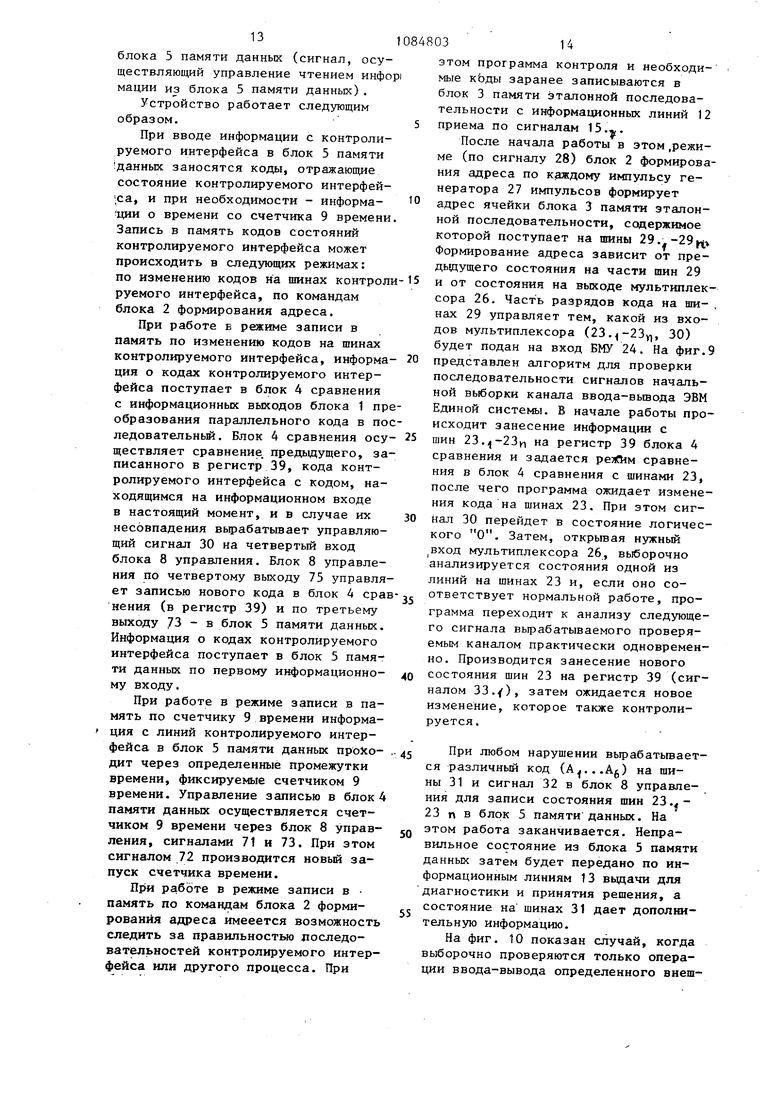

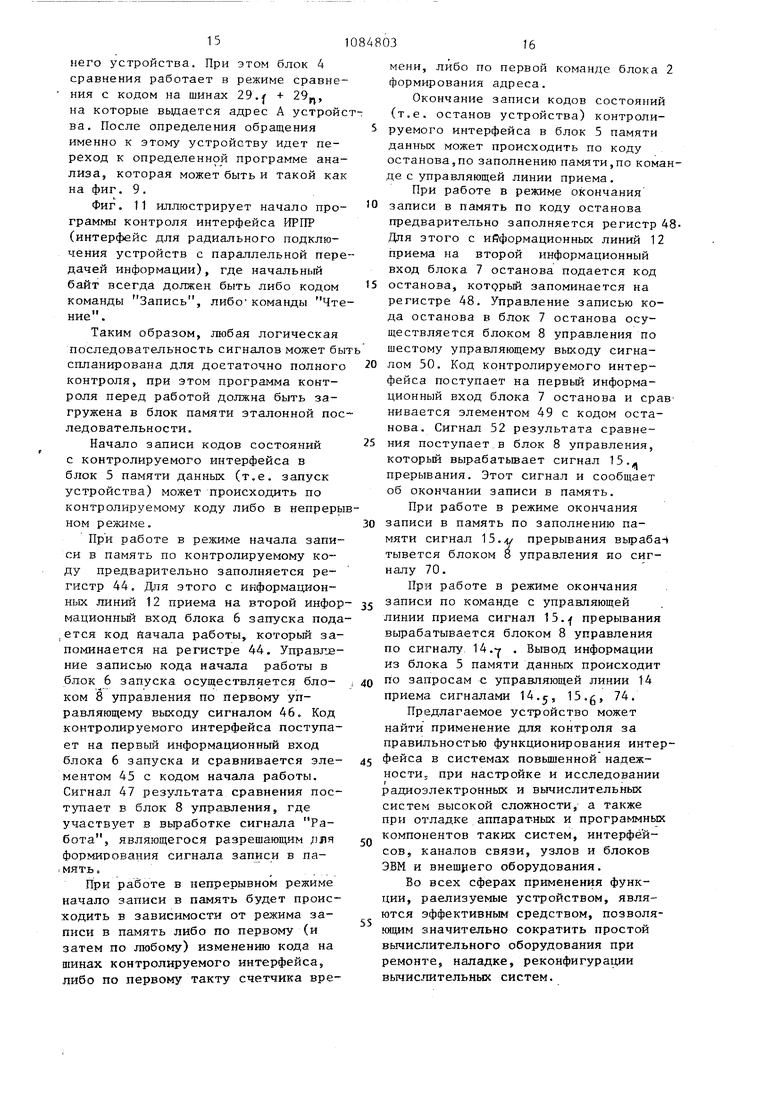

эталонной последовательности, по первому управляющему выходу - с вторым управляющим входом блока 4 сравнения, по второму управляющему вькоду - с пятым управляющим входом блока 8 управления, по первому управляющему входу - с блоком 4 сравнения, по второму управляющему входус пятым управляющим выходом блока 8 управления. В состав блока 2 формирования адреса входят группа информационньсх входов , узел 24 микропрограммного управления, регистр 25, мультиплексор 26, генератор тактовых импульсов 27. Узел 24 микропрограммного управления служит для формирования адресов блока 3 па мяти эталонной последовательности (под управлением управляющего вход-а 28 и в зависимости от кода на. шинах 29j -29г( и выхода мультиплексора 26) по каждому такту генератора 27. По шинам по каждом такту Поступает код эталонной после довательности, считанный по адресу, вьфаботанному узлом 24. Часть этого кода поступает на мультиплексор входов 23,-23 и коммутирует один из .или 30 на его выход. Выход мультиплексора 26 вместе с другой частью на шинах 291-29j используется для формирования адреса следующей ячейки блока 3 памяти эталонной последовательности на группе выходов 31. Два разряда кода на шинах 29уу заносятся на регистр 25 для выработ ки сигналов 32 и 33. Блок 3 памяти эталонной последовательности (фиг. 4) предназначен для хранения и вьщачи информации, поступающей с информационных линий 12 По первому информационному входу он связан с информационными линиями 12 приема, по второму инфор мационному входу - с информационным выходом блока 2 формирования адреса, по информационному выходу - с вторым информационным входом блока формирования адреса и вторым информационным входом блока 4 сравнени, по управляющему входу - с управляющей линией 14 приема. В состав блока 3 памяти эталонной последователь ности входят счетчик 34, которьй считывает адреса записи в память, элемент И-НЕ 35, мультиплексор 36, через который проходят адреса записи и чтения и блок 37 памяти. Блок 4 сравнения (фиг. 5) предназначен для хранения кода, отражаю щего предыдущее состояние контролируемого интерфейса, и сравнения его эталонйой последовател ности с кодом, находящимся на контролируемом интерфейсе в данньй момент времени. Блок 4 сравнения по первому информационному входу связан с выходом блока 1 преобразования параллельного кода в последовательный, по второму информационному входу - с выходом блока 3 памяти 38 эталонной последовательности, по управляющему выходу - с четвертым управляющим входом блока 8 управления, по первому управляющему входу - с четвертым управляющим выходом блока 8 управления, по второму управляющему входу - с первым управляющим выходом блока 2 формирования адреса, по третьему управляющему входу - с пятым управляющим выходом блока 8 управления. Б состав блока 4 сравнения логические первый элемент ИЛИ 38, регистр 39, в котором хранится код предыдущего состояния контролируемого интерфейса, мультиплексор 40, через который проходят либо код контролируемого интерфейса, либо код эталонной последовательности на элемент 41 сравнения, элемент И 42 и второй элемент ИЛИ 43. Блок 5 памяти данных по первому информационному входу связан с выходом блока 1 преобразования параллельного кода в последовательный, по второму входу - со счетчиком времени 9, по информационному выходу с информационными линиями 13 вьщачи, по управляющим входу и выходу с блоком 8 управления. 15лок 6 запуска (фиг. 6) предназначен для хранения некоторого кода и сравнения его с кодами, поступающими с контролируемого интерфейса с целью опознания события. Блок 6 запуска по первому информационному входу связан с выходом блока 1 пре,образования параллельного кода в последовательньй, по второму информационному входу - с информационными линиями 12 приема, по управляющему входу и выходу - с блоком 8 управления. В состав блока 6 запуска входят регистр 44, в котором хранится предварительно записанный с информационных линий 12 приема кода, элемент 45 сравнения, которьй производит сравнение состояния контролируемого интерфейса, поступающего на шины У) с содержанием регистра 44. На фиг. 6 также обозначеш.1 управляющий вход 46 регистра 44 и выход 47 блока 6 запуска. Блок 7 останова (фиг. 7) предназначен для хранения некоторого кода и сравнения его с кодами, поступающими с контролируемого интерфейса, с целью опознания события. Блок 7 останова по первому информационному

9108480310

входу связан с выходом блока 1 пре- сигнал Работа, поступающий на вхообразования параллельного кода в пос- ды элементов И-НЕ 60-62. Эти элеледовательный, по второму информади- менты через элемент ИЛИ-НЕ 63 и одонному входу - с информационными ли- ,новибратор 64 вырабатывают на выхониями 12 приема, по управляющим входу и выходу - с блоком 8 управления. В состав блока 7 останова входят регистр 48, в котором хранит ся предварительно записанньй с информационных линий 12 приема код, элемент 49 сравнения, который произ водит сравнение состояния контролируемого интерфейса, поступающего на шины с содержимым регистра 48, вход 50 и вь1ход 51. Блок 8 управления (фиг. 8) обеспечивает взаимодействие блока 2 формирования адреса, блока 4 сравнения, блока 5 памяти данных, блока 6 запуска, блока 7 останова, счетчика 9 времени. Блок 8 управления по первым входу и выходу связан с блоком 6 запуска, по вторым входу и выходу - со счетчиком 9 времени, по третьим входу и выходу - с блоком 5 памяти данных, по четвертым входу и выходу - с блоком 4 сравнения, по пятому выходу - с блоком 2 формирования адреса и блоков 4 срав нения, по пятому входу - с блоком 2 формирования адреса, по шестому входу и выходу - с блоком 7 останова, по седьмому входу и выходу - с управлякицими линиями 14 приема и 15 вьдачи. В состав блока 8 управления входят регистры , элемент И-НЕ 33, триггер 54, элемент ИЛИ-НЕ 55, элементы И-НЕ 56-58 элемент ИПИ-НЕ 59, элементы И-НЕ 60 62, элемент ИЛИ-НЕ 63, одновибратор 64, дешифратор 65, элементы И-НЕ 66-68, элемент 69 задержки. Сигнал на входе 70 идентифицирует заполнение памяти, сигнал на входе 71 указывает на срабатывание сче чика 9, на выходе 72 - на восстанов ление или следующий запуск счетчика времени 9. Регистр 52.1 служит для фиксирования режима начала работы. Первый выход этого регистра, иденти фицирующий начало работы по контрол руемому коду, совместно с сигналом результата сравнения устанавливает через элемент И-НЕ схемы 53 триггер выход .этого триггера совместно с вторым вькодом регистра 54, идентифицирующим непрерывный режим работы через элемент ИЛИ-НЕ, вырабатывает де 73 сигнал записи в память. В выр.аботке этого сигнала участвуют также первьй выход регистра 52.3, идентифицирующий режим записи в память по изменению кодов на шинах контролируемого интерфейса, второй выход регистра 52,3, идентифицирующий режим записи в память по таймеру,третий выход регистра 52.3, идентифицирующий режим записи в память по командам задатчика, сигнала 30 результата сравнения, 32 - управления записью задатчиком 2 последовательностей 71, сообщающий о срабатывании счетчика 9 времени. Кроме того, элемент И-НЕ 60 вырабатывает сигнал 42 записи в блок 4 сравнения, а элемент И-НЕ 61 - сигнал 72 восстановления или следующего запуска счетчика 9 времени. Три выхода регистра 52.2, идентифицирующие режимы останова, совместно с сигналами 51 результата сравнения, 70 заполнения памяти, окончания записи через элементы И-НЕ 56-59 вырабатьшают сигнал 15/ прерывания. Сигнал 15,), кроме того, сбрасывает регистр 52.I и триггер 54. Сигналы записи в регистры 52 -52, 44 и 48 вырабатываются дешифратором 65 и элементами И-НЕ 66-68. Выход 74 блока управления управляет чтением информации из блока 5. Счетчик 9 времени предназначен для фиксации временных интервалов. По информационному выходу он связан с блоком 5 памяти данных, по управляющим входу и выходу - с блоком 8 управления. Для облегчения понимания работы устройства на фиг. 2-8 показаны следующие сигналы: 15 -15-1 - седьмой управляющий вход блока 8 управления (сигналы адресов регистров 44, 48, 52 -52-j, 15 - седьмой управляющий вход блока 8 управления (сигнал, управляющий записью информации в регистры 44, 48 и 52), 16.у- седьмой управляющий вход блока 8 управления (сигнал, управляющий запросом информации из памяти), 15. - управляющий вход блока 3 памяти эталонный последовательности (сигнал, управляющий чтением из блока 3 памяти эталонной последователь ности), 15-1 - седьмой управляющий вход блока 8 управления (сигнал, управляющий окончанием записи кодов контролируемого интерфейса в блок 5 памяти данных), 15 - седьмой управ ляющий выход блока 8 управления (си нал, управляющий прерыванием по око чании работы)5 15.2 - седьмой упра ляющий выход блока 8 управления (си нал идентифицирующий код на информа ционных линиях 13 вьщачи), 23.-23 первые информационные входы блока 2 формирования адреса, блока 4 сравне ния, блока 5 памяти данных, блока 6 запуска, блока 7 останова, информационные выходы блока 1 преобразования параллельного кода в последовательный, пятый управлякхций выход 28 блока 8 управления, второй управляющий вход блока 2 формирования адреса, третий управляющий вход блока 4 сравнения (сигнал, осуществляющий запуск ЕМУ), 29у, - информационный выход блока 3 памяти эталонной последовательности, второй информационньш вход блока 2 формирования адреса, втоорой информационный вход блока 4 сравнения, код эталонной последовательности, 30 управляющий выход блока 4 сравнения первый управляющий вход блока 2 формирования адреса, четвертый управляющий вход блока 8 управления (сигнал, отражающий результат сравнения в блоке 4 сравнения) 31., - 31 f,информационный выход блока 2 формирования адреса, второй информационный вход блока 3 памяти эталонной последовательности (сигнал, отражающий адрес необходимой эталонной последовательности) J 32 - второй управляющий выход блока 2 формирования адреса, пятый управляющий вход блока 8 управления (сигнал запроса записи в блок 5 памяти данных), 33.первьй управляющий выход блока 2 фор мирования адреса, второй управляющий вход блока 4 сравнения (сигнал, управляющий занесением информацир в регистр 39), 33.2 первый управляющий выход блока 2 формирования адреса, второй управляющий вход блока 4 сравнения (сигнал, задающий режим сравнения содержимого регистра 39 с кодом на шинах 29.-29, 33.1 - первый управляющий выход бло ка 2 формирования адреса, второй управлякяций вход блока 4 сравнения (сигнал, задающий режим сравнения содержимого регистра 39 с кодом на шинах 23. f , 75 - четвертый управляющий выход блока 8 управления, первый управляющий вход блока 4 сравнения (сигнал, управляющий занесением информации в регистр 39), 76 пятый управляющий выход блока 8 управления, третий управляющий вход блока 4 сравнения (сигнал, осуществляющий идентификацию кода контролируемого интерфейса, поступающего в блок 4 сравнения по первому информационному входу), 46 - первый управляющий выход блока 8 управления, управляющий вход блока 6 запуска (сигнал, осуществляющий управление записью в регистр 44 информации, пос тупающей в блок 6 запуска по второму информационному входу)J 47 управляющий выход блока 6 запуска, первый управляющий вход блока 8 управления (сигнал, отражающий резулы/ тат сравнения состояния контролируемого интерфейса с содержимьм регистра 44); 50 - шестой управляющий выход блока 8 управления, управляющий вход блока 7 останова (сигнал, осуществляющий управление записью в регистр 48 информации, поступающий в блок 7 останова по второму информационному входу), 51 - управляющий вьпсод блока 7 останова, шестой управляющий вход блока 8 управления (сигнал, отражаюпщй результат сравнения состояния контролируемого интерфейса с содержимым регистром 48) 70 - управляющий выход блока 5 памяти данных, третий управляющий вход блока 8 управления (сигнал, вырабатываемый блоком 5 памяти данных по заполнению памяти), 71 - управляющий выход счетчика 9 времени, второй управляющий вход блока 8 управления (сигнал, сообщающий о срабатывании счетчика времени), 72- второй управляющий выход блока 8 управления, управляющий вход счетчика времени 9, (сигнал, осуществляющий восстановление (следующий запуск) счетчика времени 9), 73- третий управляюш:ий выход блока 8 управления, управляющий вход блока 5 памяти данных (сигнал, осуществляющий управление записью информации в блок 5 памяти данных), 74- третий управляющий выход блока 8 управления, управляющий вход блока 5 памяти данных (сигнал, осуществляющий управление чтением инфо мации из блока 5 памяти данных). Устройство работает следующим образом. При вводе информации с контролируемого интерфейса в блок 5 памяти данных заносятся коды, отражающие состояние контролируемого интерфей,са, и при необходимости - информа41ИИ о времени со счетчика 9 времени Запись в память кодов состояний контролируемого интерфейса может происходить в следующих режимах: по изменению кодов на шинах контрол руемого интерфейса, по командам блока 2 формирования адреса. При работе Е режиме записи в память по изменению кодов на шинах контролируемого интерфейса, информа ция о кодах контролируемого интерфейса поступает в блок 4 сравнения с информационных выходов блока 1 пр образования параллельного кода в по ледовательньй. Блок 4 сравнения осу ществляет сравнение, предыдущего, за писанного в регистр 39, кода контролируемого интерфейса с кодом, находящимся на информационном входе в настоящий момент, и в случае их несовпадения вырабатывает управляющий сигнал 30 на четвертый вход блока 8 управления. Блок 8 управления по четвертому выходу 75 управля ет записью нового кода в блок 4 сра нения (в регистр 39) и по третьему выходу ,73 в блок 5 памяти данных Информация о кодах контролируемого интерфейса поступает в блок 5 памяти данных по первому информационному входу. При работе в режиме записи в память по счетчику 9 времени информа ция с линий контролируемого интерфейса в блок 5 памяти данных проходит через определенные промежутки времени, фиксируемые счетчиком 9 времени. Управление записью в блок памяти данных осуществляется счетчиком 9 времени через блок 8 управления, сигналами 71 и 73. При этом сигналом 72 производится новый запуск счетчика времени. При работе в режиме записи в память по командам блока 2 формирования адреса имееется возможность следить за правильностыо лоследовательностей контролируемого интерфейса или другого процесса. При этом программа контроля и необходимые кЬды заранее записываются в блок 3 памяти эталонной последовательности с информационных линий 12 приема по сигналам 15.. После начала работы в этом .режиме (по сигналу 28) блок 2 формирования адреса по каждому импульсу генератора 27 импульсов формирует адрес ячейки блока 3 памяти эталонной последовательности, содержимое которой поступает на шины 29.--29 Формирование адреса зависит от предьщущего состояния на части шин 29 и от состояния на выходе мультиплексора 26. Часть разрядов кода на ши- , нах 29 управляет тем, какой из входов мультиплексора (23.-23у, 30) будет подан на вход БМУ 24. На фиг.9 представлен алгоритм для проверки последовательности сигналов начальной выборки канала ввода-вьшода ЭВМ Единой системы. В начале работы происходит занесение информации с шин 23.-23и на регистр 39 блока 4 сравнения и задается реяСйм сравнения в блок 4 сравнения с шинами 23, после чего программа ожидает изменения кода на шинах 23. При этом сигнал 30 перейдет в состояние логического О. Затем, открьгеая нужньй вход мультиплексора 26, выборочно анализируется состояния одной из линий на шинах 23 и, если оно соответствует нормальной работе, программа переходит к анализу следующего сигнала вырабатываемого проверяемым каналом практически одновременно. Производится занесение нового состояния шин 23 на регистр 39 (сигналом 33.), затем ожидается новое изменение, которое также контролируется. При любом нарушении вьфабатьгеается различный код (A..,Ag) на шины 31 и сигнал 32 в блок 8 управления для записи состояния шин 23 . 23 п в блок 5 памяти данных. На этом работа заканчивается. Неправильное состояние из блока 5 памяти данных затем будет передано по информационным линиям 13 вьщачи для диагностики и принятия решения, а состояние на шинах 31 дает дополнительную информацию. На фиг. 10 показан случай, когда выборочно проверяются только операции ввода-вывода определенного внешнего устройства. При этом блок 4 сравнения работает в режиме сравне ния с кодом на шинах 29. + 29, на которые выдается адрес А устрой ва. После определения обращения именно к этокгу устройству идет переход к определенной программе ана лиза, которая может быть и такой ка на фиг. 9. Фиг. 11 иллюстрирует начало про граммы контроля интерфейса ИРПР (интерфейс для радиального подключения устройств с параллельной пер дачей информации), где начальный байт всегда должен быть либо кодом команды Запись, либокоманды Чт ние. Таким образом, любая логическая последовательность сигналов может бы спланирована для достаточно полног контроля, при этом программа контроля перед работой должна быть загружена в блок памяти эталонной пос ледовательности. Начало записи кодов состояний с контролируемого интерфейса в блок 5 памяти данных (т.е. запуск устройства) может происходить по контролируемому коду либо в непреры ном режиме. При работе в режиме начала записи в память по контролируемому коду предварительно заполняется регистр 44. Для зтого с информационных линий 12 приема на второй инфор мационньй вход блока 6 запуска пода ется код йачала работы, который запоминается на регистре 44. Управление записью кода начала работы в блок 6 запуска осуществляется блоком 8 управления по первому управляющему выходу сигналом 46. Код контролируемого интерфейса поступает на первый информационный вход блока 6 запуска и сравнивается элементом 45 с кодом начала работы. Сигнал 47 результата сравнения поступает в блок 8 управления, где участвует в выработке сигнала Работа, являющегося разрешающим ляч формирования сигнала записи в паПри работе в непрерывном режиме начало записи в память будет происходить в зависимости от режима записи в память либо по первому (и затем по любому) изменению кода на шинах контролируемого интерфейса, либо по первому такту счетчика времени, либо по первой команде блока 2 формирования адреса. Окончание записи кодов состояний (т.е. останов устройства) контролируемого интерфейса в блок 5 памяти данных может происходить по коду останова,по заполнению памяти,по команде с управляющей линии приема. При работе в режиме окончания записи в память по коду останова предварительно заполняется регистр 48Для этого с информационных линий 12 приема на второй информационный вход блока 7 останова подается код останова, котдрьй запоминается на регистре 48. Управление записью кода останова в блок 7 останова осуществляется блоком 8 управления по шестому управляющему выходу сигналом 50. Код контролируемого интерфейса поступает на первьй информационный вход блока 7 останова и сравнивается элементом 49 с кодом останова. Сигнал 52 результата сравнения поступает в блок 8 управления, который вырабатьтает сигнал 15. прерывания. Этот сигнал и сообщает об окончании записи в память. При работе в режиме окончания записи в память по заполнению памяти сигнал 15.у прерывания вьфаба-t тывется блоком 8 управления ио сигналу 70. При работе в режиме окончания записи по команде с управляющей линии приема сигнал 15.f прерывания вырабатывается блоком 8 управления по сигналу 14. . Вывод информации из блока 5 памяти данных происходит по запросам с управляющей линии 14 приема сигналами 14., 15.g, 74. Предлагаемое устройство может найти применение для контроля за правильностью функционирования интерфейса в системах повышенной надежности,, при настройке и исследовании радиоэлектронных и вычислительных систем высокой сложности, а также при отладке аппаратных и программных компонентов таких систем, интерфейсов, каналов связи, узлов и блоков ЭВМ и внешрего оборудования. Во всех сферах применения функции, раелизуемые устройством, являются эффективным средством, позволяющим значительно сократить простой вычислительного оборудования при ремонте, наладке, реконфигурагщи вычистштельных систем.

Фиг.3

3ir:3iff

31гЗ{„

8 35

5б

Памяти

13

Фаг.4

37

29г 19п

г9г29п

28

S 42

33,

51

i

38

75

MX

0

3,23п

;

ее м

30

76 33s

4J

Фиг.5

Hova/ю )

-т

выработка сигнал Ц ЗЗз

Выработка сигнала Л

Выработка сигнала

9(0арша KtaaASj/o шинах 31

Л

вырввоткв cutMfa

J

QcmaHO&f(a

огиравтка сигнала

JJi

Фиг У

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВА ДЛЯ ПРИЕМА РЕЧИ, ПЕРЕДАННОЙ ПО РАДИОТЕЛЕФОНУ | 1924 |

|

SU1060A1 |

| Под ред | |||

| A.M.Кариенова, М | |||

| Статистика, 1973, с.207-210 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 754424, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-07—Публикация

1982-10-13—Подача