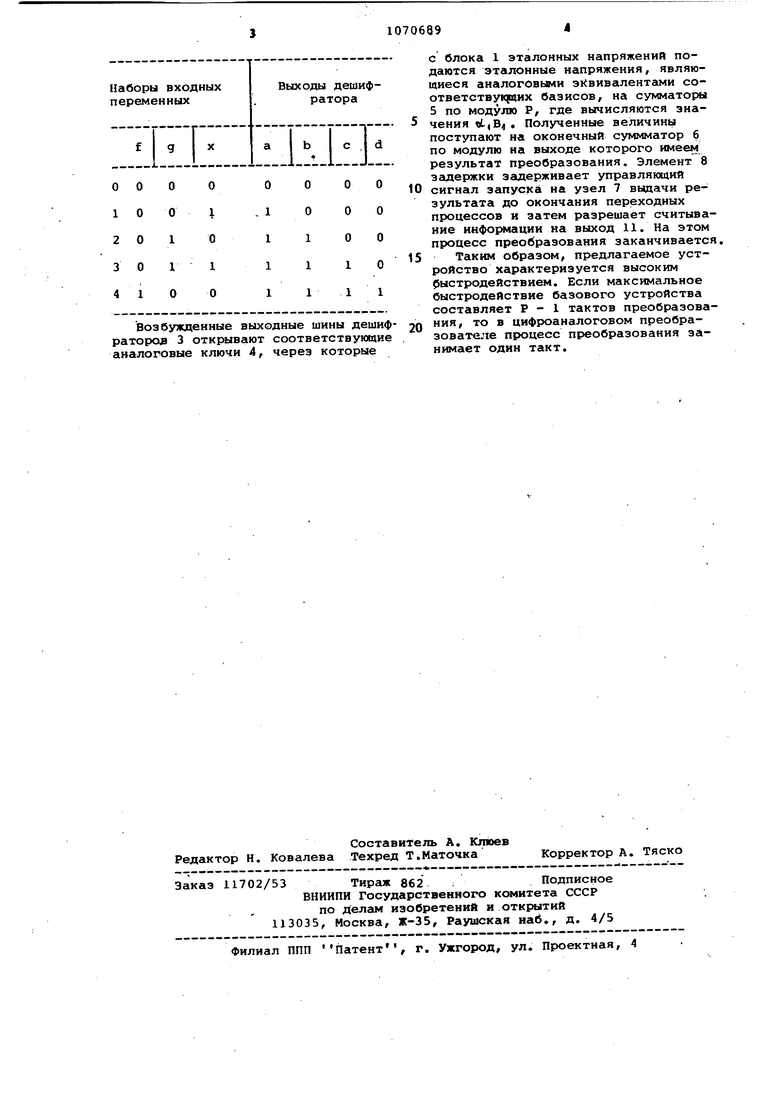

Изобретение относится к вычислительной технике и предназначено для преобразования кода системы остаточ ных классов в напряжение. Известно устройство для преобразования кода системы остаточных классов в позиционный код, содержащее блок модульных накапливающих сумматоров, блок контроля обнуления управляющий блок и позиционный сумматор 5 . Недостатками данного устройства являются низкое быстродействие, а также невозможность непосредственного преобразования кода системы остаточных классов в аналоговую величину. Наиболее близким к предлагаемому является цифроаналоговый преобразователь, содержащий входной регистр,, блоки счетчиков, элементы сравнения элемент И, блоки преобразования линейно изменяющегося напряжения, генераторы линейно изменяющегося напряжения, блок эталонных напряжений преобразователь код-напряжение, сумматор напряжений, узел выдачи резуль тата, причем выходы генераторов линейно изменяющегося напряжения через блоки преобразования линейно изменяющегося напряжения и блоки счетчиков подключены к первым входам соответствующих элементов сравнения вторые входы которых соединены с соответствующими выходами входного регистра, выходы элементов сравнения соединены с соответствующими входами элемента И, выход которого подключен к входам генераторов линейно изменяющегося напряжения, первому входу преобразователя код-напряжение и к управляющему входу узла выдачи результата, информационный вход которого соединен с выходом сумматора напряжений, входы которого соединены соответственно с выходами преобразователя код-напряжение и блока эталонных напряжений, вход которого соединен с выходом генератора линейно, изменяющегося напряжения, выхоД счетчика по наименьшему основанию соединен с вторым входом .преобразователя код-напряжение, выход узла выдачи результата является выходом цифроаналогового преобразователяt2j. Недостатком известного устройства является низкое быстродействие, которое определяется числом тактов, равным величине преобразуемого кода Цель изобретения - повышение быст родействия. Поставленная цель достигается тем что цифроаналоговый преобразователь содержащий входной регистрj блок эталонных напряжений, оконечный сумматор по модулю и узел выдачи результата, причем выход оконечного сумматора по модулю соединен с информационным входом узла выдачи результата, выход которого является выходом цифроаналогового преобразователя, содержит п дешифраторов,h групп аналоговых ключей, п сумматоров по модулю и элемент задержки, причем выходы входного регистра подключены к входам соответствующих дешифраторов, выходы которых подключены соответственно к управляющим входам аналоговых ключей соответствующих групп, информационные входы которых соединены с соответствующими выходами блока эталонных напряжений, выходы аналоговых ключей каждой из групп подключены соответственно к входам соответствующего сумматора по модулю, выход которого соединен с соответствующим входом оконечного сумматора по модулю, управляющий вход узла выдачи результата соединен с выходом элемента задержки, вход которого соединен с управляющим входом входного регистра и Является входом запуска цифроаналогового преобразователя. На чертеже приведена схема цифроаналогового преобразователя. Цифроаналоговый преобразователь содержит блок 1 эталонных напряжений, входной регистр 2, дешифраторы 3, группы 4 аналоговых ключей, сумматоры 5 по модулю, оконечный сумматор 6 IJO модулю, узел 7 выдачи результата, элемент 8 задержки, вход запуска цифроаналоговлго преобразователя 9, входную шину 10, выход цифроаналогового преобразователя 11, Из теории чисел известно, что если число А представлено в системе остаточных классов с основаниями PI, Р2.,,.,., ,Pti, остатками ot ,о1г,... , , то оно может быть найдено как , Р,,+ + ijbi+.,. + cLj, „ ., J, Выбираем коэффициенты ортогонального базиса BX vP- Ре Яv- . -Pr, / причем r, такое, что (В)пух1 Pi l. В цифроаналоговом преобразователе используется принцип преобразования, описываемый данными выражениЦифроаналоговый преобразователь работает следующим образом. Пусть на шинах 10 выставлены позиционные (например, двоичные) коды остатков преобразуемого числа. С приходом по входу 9 разрешающего сигнала остатки переписываются во входной регистр 2 и поступают на входы дешифраторов 3, которые преобразуют позиционные коды остатков в количество возбужденных выходных шин, равное величине остатка. Таблица истинности деиифратора для основания Р « 5 и двоичного кода на входе представлена в таблице.

Возбужденные выходные шины дешифратороз 3 открывают соответствующие аналоговые ключн 4, через которые

с блока 1 эталонных напряженнй подаются эталонные напряжения, являющиеся аналоговьми эквивалентами соответствукуцих базисов, на сумматоры 5 по модулю Р, где вычисляются значения Ъц . Полученные величины поступают на оконечный суммматор б по модулю на выходе которого имеем результат преобразования. Элемент 8 задержки задерживает управляющий

0 сигнал запуска на узел 7 результата до окончания переходных процессов и затем разрешает считывание информации на выход 11. На этом процесс преобразования заканчивается.

5

Таким образом, предлагаемое устройство характеризуется высоким быстродействием. Если максимальное быстродействие базового устройства составляет Р - 1 тактов преобразования, то в цифроаналоговом преобра0зователе процесс преобразования занимает один такт.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1983 |

|

SU1175034A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1989 |

|

SU1742997A1 |

| Непозиционный цифроаналоговый преобразователь | 1983 |

|

SU1173558A1 |

| Многоканальный преобразователь кода в напряжение | 1985 |

|

SU1279071A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Сумматор по модулю | 1982 |

|

SU1134939A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ содержащий входной регистр, блок эталонных напряжений, оконечный сумматор по модулю и узел выдачи результата, причем выход оконечного сумматора по модулю соединен с информационным входом узла выдачи результата, выход которого является вьосодом цифроаналогового преобразователя, отличающийс я тем, что, с целью повышения быстродействия, он содержит л дешифраторов, tS Я-i .групп аналоговых ключей, ti сумматоров по модулю и элемент задержки, причем выходц: входного регистра подключены к входам соответствующих дешифраторов, выходы которых подключены соответственно к управляющим входам аналоговых ключей соответст-. вующих групп, информационные входы котоЕ ис соединены с сос тветствуквдими выходами блока эталонных напряжений, выходы аналоговых ключей каждой из групп подключены соответственно к входам соответствующего сумматора ПС модулю, выход которого соединен с соответствующим входом оконечного сумматора по модулю, управляющий вход узла выдачи результата соединен с выходом элемента згщержки, W вход которого соединен с управляющим входом входного регистра и является входом запуска цифроаналогового преобразователя, о:) 00 со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь кода числа из системы остаточных классов в позиционный код | 1974 |

|

SU554536A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР , И 282767, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-01-30—Публикация

1982-11-09—Подача