З.п-1

9,1

2

ю ю

Ч) 4

Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных устройств, функционирующих в системе остаточных классов (СОК) с различными оконечными устройствами, требующими аналогового вывода, а также в технике связи при использовании кодов СОК в цифровой телефонии.

Цель изобретения - повышение быстродействия и упрощение преобразователя.

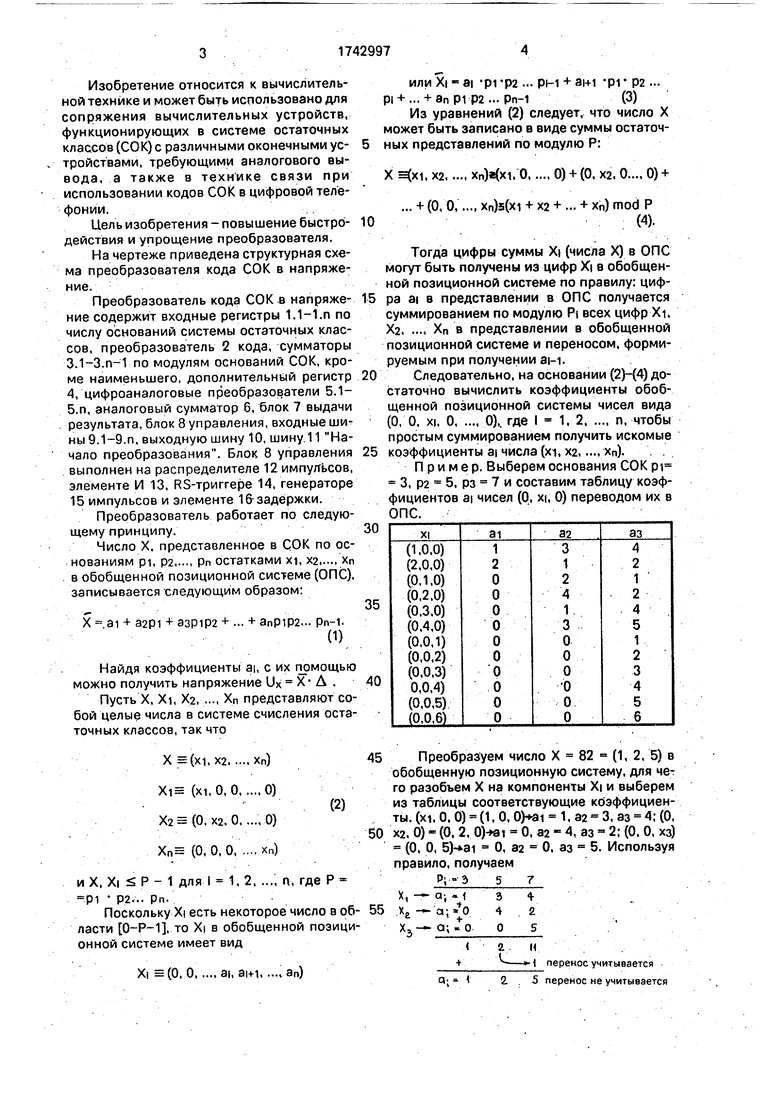

На чертеже приведена структурная схема преобразователя кода СОК в напряжение.

Преобразователь кода СОК в напряжение содержит входные регистры 1.1-1.П по числу оснований системы остаточных классов, преобразователь 2 кода, сумматоры ЗЛ-З.п-1 по модулям оснований СОК, кроме наименьшего, дополнительный регистр 4, цифроаналоговые преобразователи 5.1- 5.п, аналоговый сумматор 6, блок 7 выдачи результата, блок 8 управления, входные шины 9.1-9.п, выходную шину 10, шину 11 Начало преобразования. Блок 8 управления выполнен на распределителе 12 импульсов, элементе И 13, RS-триггере 14, генераторе 15 импульсов и элементе 1& задержки.

Преобразователь работает по следующему принципу.

Число X, представленное в СОК по основаниям pi, paРп остатками xi, X2хп

в обобщенной позиционной системе (ОПС), записывается следующим образом:

X ai + Э2р1 + эзр1р2 + ... + anpip2... рп-1.

(1)

Найдя коэффициенты ai, с их помощью можно получить напряжение Ux Х- А ,

Пусть X, Xi, Ха, .... Хп представляют собой целые числа в системе счисления остаточных классов, так что

X (Х1,Х2Хп)

.0) .0)

Хп)

(2)

и X, Х| Ј Р - 1 для t 1, 2п, где Р

Р1 Р2... Рп.

Поскольку Xi есть некоторое число в об- ласти О-Р-1, то Xi в обобщенной позиционной системе имеет вид

Xi (0, 0ai, ан-1ап)

ИЛИ Х| - 8| Р1 ф2 ... РМ + 31-М Р1 Р2 ...

pi +... + an pi P2 ... Рп-1(3)

Из уравнений (2) следует, что число X может быть записано в виде суммы остаточ- ных представлений по модулю Р:

X , Х2Хп)ф1, 00) + (О, Х2. 0..., 0) +

... + (0, 0xn)s(xi + Х2 + ... + хп) mod P

(4).

Тогда цифры суммы Xi (числа X) в ОПС могут быть получены из цифр Xi в обобщенной позиционной системе по правилу: цифpa ai в представлении в ОПС получается суммированием по модулю PI всех цифр XL

Ха Хп в представлении в обобщенной

позиционной системе и переносом, формируемым при получении ам.

Следовательно, на основании (2)-{4) А° статочно вычислить коэффициенты обобщенной позиционной системы чисел вида

(О, 0, xi, 0 0), где I 1, 2 п, чтобы

простым суммированием получить искомые

коэффициенты ai числа (xi, X2хп).

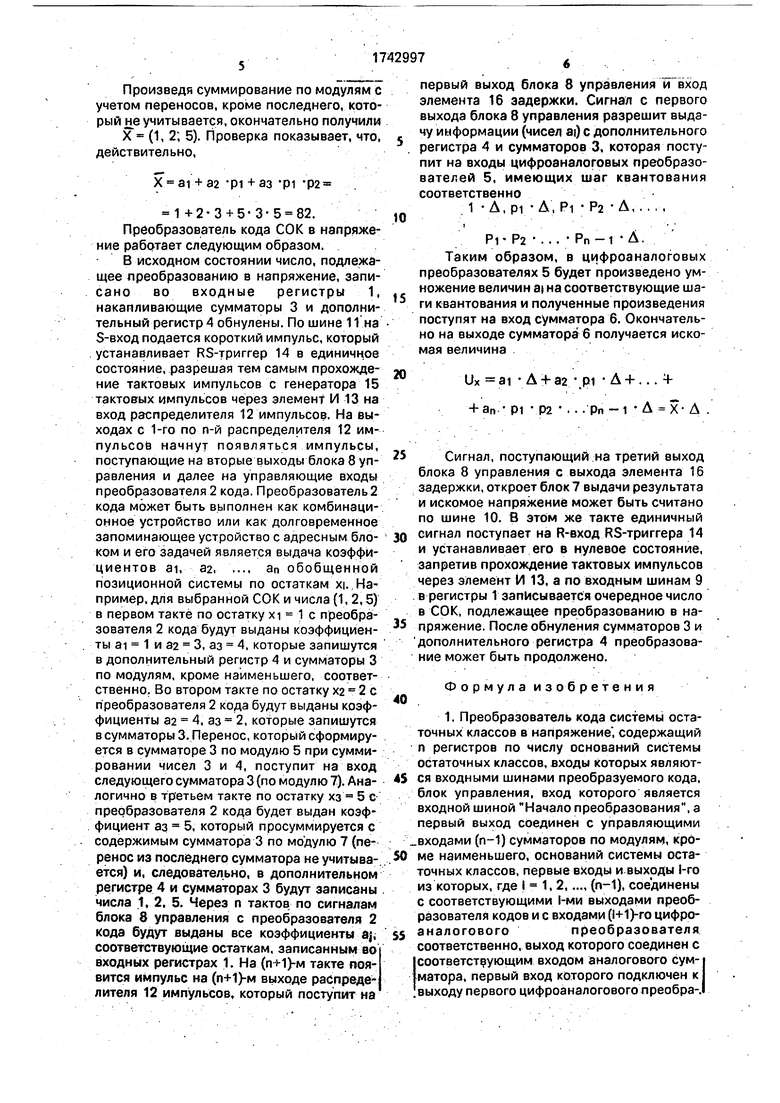

Пример. Выберем основания СОК pi 3, р2 5, рз 7 и составим таблицу коэффициентов ai чисел (0, xi, 0) переводом их в ОПС.

Преобразуем число X 82 (1, 2, 5) в обобщенную позиционную систему, для чего разобьем X на компоненты Xi и выберем из таблицы соответствующие коэффициенты, (xi. 0. 0) (1, 0, 1, 32 3, аз 4; (О, Х2, 0) - (0, 2, 0)-«и - 0, а2 - 4, аз - 2; (О, О, хз) (0, 0, 5) О, 32 0, аз 5. Используя правило, получаем

перенос учитывается 5 перенос не учитывается

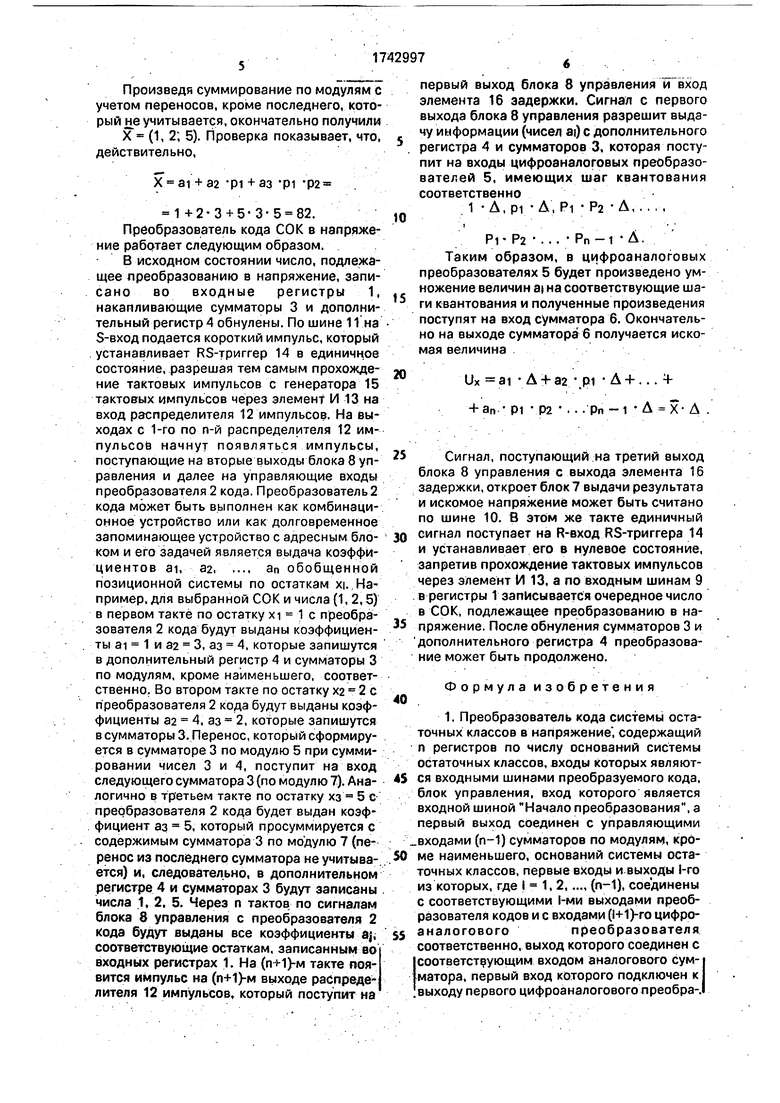

Произведя суммирование по модулям с учетом переносов, кроме последнего, который не учитывается, окончательно получили

X (1, 2; 5). Проверка показывает, что, действительно,

X ai + аз Pi + аз pi ф2

1 + 2-3 + 5-3-5 82.

Преобразователь кода СОК в напряжение работает следующим образом.

В исходном состоянии число, подлежащее преобразованию в напряжение, записано во входные регистры 1, накапливающие сумматоры 3 и дополнительный регистр 4 обнулены. По шине 11 на S-вход подается короткий импульс, который устанавливает RS-триггер 14 в единичное состояние, разрешая тем самым прохождение тактовых импульсов с генератора 15 тактовых импульсов через элемент И 13 на вход распределителя 12 импульсов. На выходах с 1-го по n-й распределителя 12 импульсов начнут появляться импульсы, поступающие на вторые выходы блока 8 управления и далее на управляющие входы преобразовзтеля 2 кода. Преобразователь2 кода может быть выполнен как комбинационное устройство или как долговременное запоминающее устройство с адресным блоком и его задачей является выдача коэффициентов ai, 32 ап обобщенной

позиционной системы по остаткам xi. Например, для выбранной СОК и числа (1, 2,5) в первом такте по остатку xi 1 с преобразователя 2 кода будут выданы коэффициенты ai 1 и 32 3, аз 4, которые запишутся в дополнительный регистр 4 и сумматоры 3 по модулям, кроме наименьшего, соответственно. Во втором такте по остатку Х2 2 с преобразователя 2 кода будут выданы коэффициенты 32 4. аз 2, которые запишутся в сумматоры 3. Перенос, который сформируется в сумматоре 3 по модулю 5 при суммировании чисел 3 и 4, поступит на вход следующего сумматора 3 (по модулю 7). Аналогично в третьем такте по остатку хз 5 с преобразователя 2 кода будет выдан коэффициент аз 5, который просуммируется с содержимым сумматора 3 по модулю 7 (перенос из последнего сумматора не учитывается) и, следовательно, в дополнительном регистре 4 и сумматорах 3 будут записаны числа 1, 2, 5. Через п тзктов по сигналам блока 8 управления с преобразователя 2 кода будут выданы все коэффициенты aj, соответствующие остаткам, записанным во входных регистрах 1. На (пН)-м такте появится импульс на (п+1)-м выходе распределителя 12 импульсов, который поступит на

5

первый выход блока 8 управления и вход элемента 16 задержки. Сигнал с первого выхода блока 8 управления разрешит выдачу информации (чисел ai) с дополнительного регистра 4 и сумматоров 3, которая поступит на входы цифроаналоговых преобразователей 5, имеющих шаг квантования соответственно

1 Д.Р1 A, Pi Р2 А

t

Pi- Pz ... Pn-i Д. Таким образом, в цифроаналоговых преобразователях 5 будет произведено умножение величин ai на соответствующие шаги квантования и полученные произведения поступят на вход сумматора 6. Окончательно на выходе сумматора 6 получается искомая величина

Ux ai A-f 32 pi

+ an pi P2

Pn

Д + ...4- -i -A X- A

5

0

5

0

5

O

5

Сигнал, поступающий на третий выход блока 8 управления с выхода элемента 16 задержки, откроет блок 7 выдачи результата и искомое напряжение может быть считано по шине 10. В этом же такте единичный сигнал поступает на R-вход RS-триггера 14 и устанавливает его в нулевое состояние, запретив прохождение тактовых импульсов через элемент И 13, а по входным шинам 9 в регистры 1 записывается очередное число в СОК, подлежащее преобразованию в напряжение. После обнуления сумматоров 3 и дополнительного регистра 4 преобразование может быть продолжено.

Формула изобретения

1. Преобрззовэтель кода системы остаточных классов в напряжение , содержащий п регистров по числу оснований системы остаточных классов, входы которых являются входными шинами преобрэзуемого кода, блок управления, вход которого является входной шиной Начало преобразования, а первый выход соединен с управляющими .входами (п-1) сумматоров по модулям, кроме наименьшего, оснований системы остаточных классов, первые входы и выходы 1-го

из которых, где I 1, 2(п-1), соединены

с соответствующими l-ми выходами преобразователя кодов и с входами (+1)-го цифро- аналоговогопреобразователя

соответственно, выход которого соединен с (соответствующим входом аналогового сум- j матора, первый вход которого подключен к I выходу первого цифроаналогового преобра-.l

зователя, а выход соединен с входом блока1 л выдачи результата, выход которого является выходной шиной, отличающийся тем,. что, с целью повышения быстродействия и,-/ упрощения преобразователя, в него введен дополнительный регистр, входы и выходы которого соединены с соответствующими дополнительными выходами преобразователя кодов и с входами первого цифроана- логового преобразователя соответственно, а вход управления соединен с первым выходом блока управления, второй выход которого подключен к управляющему входу блока выдачи результата, а группа выходов соединена с соответствующими управляющими входами преобразователя кодов, информационные входы которого соединены с выходами соответствующего регистра, вы10

15

основания системы остаточных кла |кроме (п-1)-го, соединен с вторым вх (1+1)-го сумматора по модулю основан стемы остаточных классов.

2. Преобразователь по п. 1, о т л и щийся тем, что блок управления вып в виде распределителя импульсов, RS гера. элемента И, элемента задержки нератора импульсов, выход кото соединен с первым входом элемента И рой вход и выход которого соединены ветственно с выходом RS Tpnrrepa и вх распределителя импульсов, п выходов рого являются группой выходов блока, й выход является первым выходом бл соединен с входом элемента задерж R-входом RS-триггера, S-вход которо ляется входом блока, выход элемента з

ОтлиДО 1 vr w ff4f w -/-- - - ii i/ITIC BAw/ twlTl «W/L% w 1

ходы переноса l-ro сумматора по модулю жки является вторым выходом блока.

20 т

0

5

основания системы остаточных классов, |кроме (п-1)-го, соединен с вторым входом (1+1)-го сумматора по модулю основания системы остаточных классов.

2. Преобразователь по п. 1, о т л и ч а ю- щийся тем, что блок управления выполнен в виде распределителя импульсов, RS-триг- гера. элемента И, элемента задержки и генератора импульсов, выход которого соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом RS Tpnrrepa и входом распределителя импульсов, п выходов которого являются группой выходов блока, (п+1)- й выход является первым выходом блока и соединен с входом элемента задержки и R-входом RS-триггера, S-вход которого является входом блока, выход элемента задер/ITIC BAw/ twlTl «W/L% w 1

жки является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1983 |

|

SU1175034A1 |

| Устройство для преобразования чисел в системе СОК | 1990 |

|

SU1785080A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1989 |

|

SU1698991A1 |

| Преобразователь полиадического кодаВ КОд СиСТЕМы ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU809154A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1986 |

|

SU1372620A1 |

| НЕЙРОННАЯ СЕТЬ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2008 |

|

RU2400813C2 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных устройств, функционирующих в системе остаточных классов с различными оконечными аналоговыми устройствами. Цель изобретения - по 9.л вышение быстродействия и упрощение преобразователя. Преобразователь кода системы остаточных классов в напряжение содержит п регистров 1.1-l.n, преобразователь 2 кода, (п-1) сумматоро в 3.1-З.П-1 по модулям оснований системы остаточных классов, дополнительный регистр 4, п циф- роаналоговых преобразователей 5.1-Б.п, аналоговый сумматор 6. блок 7 выдачи результата, блок 8 управления, входную информационную шину 9, выходную шину 10 и шину 11 Начало преобразования. Положительный эффект обеспечивается за счет усовершенствования алгоритма преобразования кода системы остаточных классов в двоичный код. 1 з.п. ф-лы, 1 ил., 1 табл. V и

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ;: •:Г.'>&пч->&зн^Я• • •*>&•<» ^* •••••«•••f-*F<,|A ;!!•> v>&<<iib I .nriVi ;1-.'Кй]1! | 0 |

|

SU282767A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1983 |

|

SU1175034A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-23—Публикация

1989-12-11—Подача