управления вьтолнен на генераторе тактовых импульсов,элементе И,К8триггере,элементе задержки,вход которого является первым входом блока управления,выход подключен к S-входу К5-триггера,К-вход которого явл ется вторым входом блока управления выход является первым выходом блока управления и подключен к первому входу элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход является вторым выходом блока управле ния. 3. Преобразователь по п. 1, отличающийся тем, что блок сборки сигналов сравнения выполнен на (п- 2) элементах И, первые входы которых и второй вход первого элемента И являются входами блока сборки сигналов сравнения, каждый прямой выход (п- 3) элементов И, начиная с первого, подключен к второму входу последующего элемента И, прямой выход (и- 2) элемента И является первым выходом блока сборки сигналов сравнения, а инверсные выходы элементов И являются вторыми выходами блока сборки сигналов сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1986 |

|

SU1372620A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1983 |

|

SU1181140A1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Устройство для преобразования напряжения в код системы остаточных классов | 1981 |

|

SU1029410A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1986 |

|

SU1368989A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

1. ПРЕОБРАЗОВАТЕЛЬ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ в НАПРЯЖЕНИЕ, содержащий п регистров, по числу оснований системы остаточных классов, входы которых являются входными шинами преобразователя, выходы ( л -1) регистров подключены к соотвествующим первым входам (п.-1) блоков сравнения, прямые выходы которых подключены к входам блока сборки сигналов сравнения, первый выход которого подключен к управляющему входу блока вьодачи напряжения, выход которого является выходной шиной преобразователя, вход подключен к выходу блока суммирования напряжений, первый вход которого подключен к выходу первого цифро-аналогового преобразователя, отличающий- с я тем, что, с целью повьш1ения быстродействия, в него введены (а -1) сумматоров по модулям оснований системы остаточных классов, кроме наименьшего, первый и второй преобразователи кода, (-1) элементов И, (п-1) счетчиков, (и.-1) цифро-аналоговых преобразователей, блок ключей, блок управления, первый вход которого объединен с управляющем входом блока ключей и является шиной начала преобразования, второй вход подключен к первому выходу блока сборки сигналов сравнения, группа вторых выходов которого и инверсный выход первого блока сравнения подключены к соответствующим первым входам первого преобразователя кодов, вторые входы которого подключены к соответствующим прямым выходам блоков сравнения, третий вход подключен к первому выходу блока управления, а выходы - к соответствующим первым входам второго преобразователя кодов и первым входам соответствую1хих (т--) элементов И, . .вторые входы которых объединены с управляющими входами сумматоров по модулям и подключены к второму выходу блока управления, выходы подключены к входам (п.-1) счетчиков, выходы которых подключены к соответству ющим входам соответствующих (п-1) цифрраналоговых преобразователей, выходы которых подключены к соответствующим (п-1) входам блока суммирования напряжений, при этом высд ходы первого регистра подключены к соответствующим входам первого цифро аналогового преобразователя и к соответствующим входам блока ключей, выходы которого подключены к соответст вующим вторым входам второго преобразователя кода,выходыкоторого подключены к соответствующим информационным входам сумматоров по модулям,выходыкоторых подключены к соответствующим вторым входам соответствующих блоков сравнения. 2. Преобразователь по п. 1, отличающийся тем, что блок

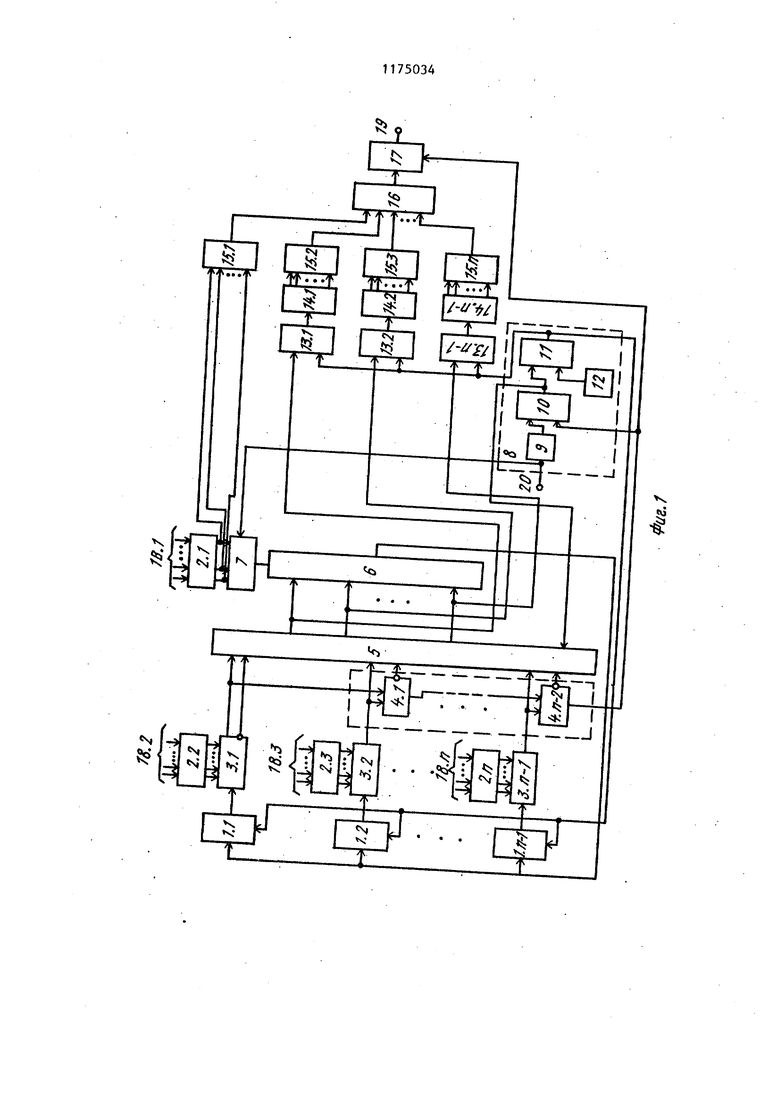

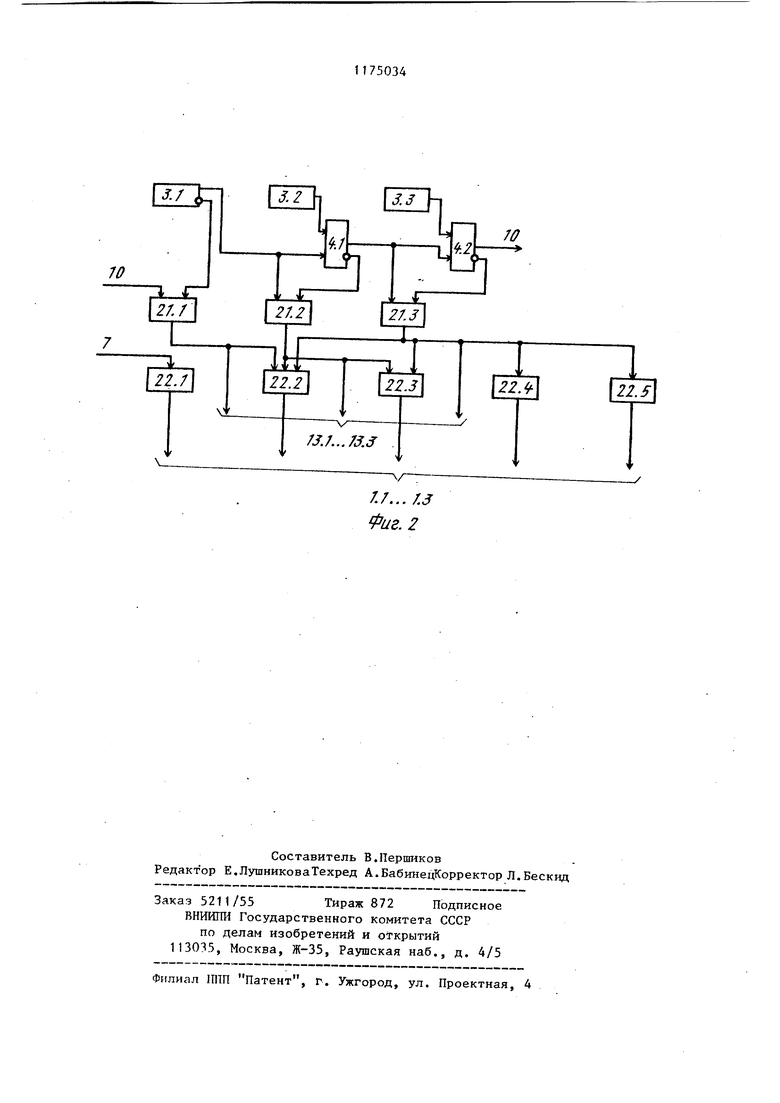

Изобретение относится к вычислительной технике и может быть исполь зовано для сопряжения вычислительны устройств, функционирующих в систем остаточных классов (СОК) с различны ми оконечными устройствами, требую дими аналогового вывода, а также в технике связи при использовании .кодов СОК в цифровой телефонии. Цель изобретения - повьпление быс родействия преобразования. На фиг. приведена структурная схема преобразователя кода СОК в напряжение; на фиг. 2 - пример реализации первого и второго преобра. зователей кода для основания СОК 2, 5, 7. Преобразователь кода СОК в напря жение содержит сумматоры 1.1 - 1 fi по модулям СОК кроме наименьшего, регистры 2.1 - 2.П, блоки 3.1 3,л-1 сравнения, блок сборки сигналов сравнения, который выполнен на элементах И 4.1 - 4 п-2первый и второ преобразователи 5 и 6 кодов, блок 7 ключей, блок 8 управления, которьш вьтолнен на элементе 9 задержки, RS - триггере 10, элементе И 11, генераторе 12 тактовых импульсов, элементы И 13.1 - 13.П-1, счетчики 14.1 - 14ц-), цифро-аналоговые преобразователи (ЦАП) 15.1 - 15п, блок 16суьтмирования напряжений, блок 17выдачи напряжения, входные шины 18.1 - 18п, выходную шину 19, гаину 20 начала преобразования. Первый и второй преобразователи 5 и 6 кодов могут быть вьтолнены, например, как показано на фиг. 2, для СОК с основанием 2, 3, 5, 7 на элементах И 21.1 - 21.3 и элементах Ш1И 22.1 - 22.5 соответственно. Преобразователь работает по следующему принципу. Число А, представленное в СОК по основаниям Р , Р , . ., Pf ocTaTками, dL ,(1 .. . в обобщенной позиционной системе (ОПС), записывается следующим образом: . . ..+ а ,... Нахождение коэффициентов а, и с их помощью напряжения U)(A-A, является конечной задачей преобразования. Очевидно, что о1 , /А/р /А/р /a +ajpi/ р., ; PI+ PiPz +а„ .,Ptx-i / РП Другими словами для отыскания коэффициента а ; необходимо к а прибавлять величину р до тех пор, пока cA.j не станет равным и, следовательно, . Аналогично /а,+ j t jL , У 0-3

Таким образом можно найти все коэффициенты а, а затем, умножив , на соответствующие веса, найти значение А. Для умножения в аналоговом виде можно использовать цифро-аналоговые преобразователи, у которых шаг квантования равен соответственно

Тогда-

JJ а,- , u-ja,p Pj ... + а ...р„., й A-U, т.е. задача преобразования решена.

Преобразователь кода СОК в напряжение работаетСледующим образом.

В исходном состоянии все сумматоры 1.1 -1in-i; по модулям, счетчики 1А.1 - 14... .блок 16 и RS - триггер 10 обнулены. По входным шинам 18 подаются остатки и,, OCf, и записываются в регистры 2.1 -2.п. ЦАП 15.1 имеет шаг квантования l-.

По шине 20 подается короткий импульс, который открывает блок 7 ключей и код ot) , пройдя второй преобразователь 6 кода записывается в сумматоры 1.2-1.П по модулям. Элемент 9 задержки выполнен таким образом, что длительность задержки сигнала в нем больше длительности запускающего импульса. Таким образом, RS - триггер 10 перейдет в единичное состояние после того, как блок 7 ключей закроется. Единичньш потенциал с прямого выхода RS - триггера 10 подается на второй вход элемента И 21.1 , на первый вход которого подается .единичный потенциал с инверсного выхода блока 3.1 сравнения. Под действием сигнала с элемента 21.1 во втором преобразователе 6 кода формируется код величины Р,,. Одновременно единичный потенциал с элемента И 21. 1 подается на первый вход элемента И 13.1 и тем самым разрешает прохождение тактовых импульсов с блока 8 управления.- Под действием каждого тактового импульса во все сумматоры 1.1 - 1 п-1 прибавляется веа Счетчик 14.1

личина

одно1временно увеличивает свое состояние

на 1. В тот момент, когда . станет равным ix, т.е. выполнится равенство

+ JPf/pt 2 J счетчике 14f будет находится величина а„, которая, пройдя процесс цифро-аналогового преобразователя в - ЦАПе 15.2, имеющем шаг квантования р , запишется в блок 16 в виде величины аяр, & и сложится с а, д. При совпадении кодов ос 2 и содержимого сумматора 1{ по модулю на прямом выходе блока 3.1 появится единичный потециал, а на инверсном-нулевой. В результате этого с выхода элемента И 21.1 . единичный потенциал изчезнет, а появится на выходе элемента И 21.2 на один вход которого подается единичный потенциал с прямого выхода блока 3.1, а на другой - единичный потенциал с инверсного выхода элемента И 4.1,.так как с блока 3.2 снимается нулевой потенциал. Прохождения импульсов разрешается теперь на счетчик 14.2, а сумматоры 1,2 1,1(1-1 за каждьй такт добавляется величина Р,, Р ,код которой сформирован теперь на выходе второго преобразователя 6 кода.Когда of.,-станет равнымixf, вновь произойдёт переключение выхода следующего элемента И.. первого преобразователя 5 кода, а в блок 16 прибавится величина а,р р д. Далее процесс будет продо.пжаться до тех пор, пока на выходе элемента И 4.,п-2 не появится единичный потенциал. К этому времени в блоке 16 будет находится величина

Ux Л (а,+ а р+ .. .+а р р ...,

) АА

P:h.

:h-1

Единичный потенциал на выходе элемента И 4.,Г|-2 переведет RS - триггер Ю в нулевое состояние, что зап.ретит выдачу тактовых импульсов с блока 8 управления и откроет блок 17 выдачи напряжения, Результат преобразования будет считан по шине 19.

ч/ ; Z/.../J

Фиг. 2

| Устройство для сопряжения | 1981 |

|

SU991407A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ;: •:Г.'>&пч->&зн^Я• • •*>&•<» ^* •••••«•••f-*F<,|A ;!!•> v>&<<iib I .nriVi ;1-.'Кй]1! | 0 |

|

SU282767A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-23—Публикация

1983-05-27—Подача