Изобретение относится к -технике связи и может быть .использовано в системах передачи данных и телеметрии. ,

Известно устройство для формирования сигналов с амплитудно-фазовой модул)1цией, содержащее кодер, выход которого подключен к входу. Цифрового трансвсрсильного фильтра, выходы которого через соответствующие фильтры нижних частот соединены с входг1ми модуляторов, выходы которых подключены к входам суиалатора, выхо4 которого соединен с входом выходного Лильтра нижних частот fll.

Недостатком данного устройства является низкая точность формирования. ...,

Наиболее близким техническим решением к изобретению являетсй

устройство, содержащее источник данных, выход которого соединен с входами первой и второй линий задержки, первый и второй блоки памяти, выходы которых подключены к первым входам соответственно первого и второго перемножителей, выходы которых соединены с входами сумматора, выход которого через цифроаналоговый преобразователь подключен к входам фильтра нижних час- с тот. 121.,

Однако известное устройство обладает низкой точностьюформирования сигналов.

Цель изобретения - повышение , точности формирования.

Для достижения указанной цели в устрой Ство для цифрового формирования сигналов с амплитудно-фазо- . воймодуляцией, содержащее источник данных, выход которого соединен с входами первой и второй линий задержки, первый и второй блоки памяти, выходы которых подключены к первым входам соответственно первого и второго перемножителей, выходы которых соединены с входами .сумматора, выход которого через цйЛроаналоговый преобразователь подключен к входам фильтра нижних частот, введены два дополнительных блока. Пс1мяти и первый и второй дешифраторы,, выходы которых подключены к первым входам соответствен-: но первого и второго дополнительных блоков памяти, выходы которых . соединены с вторымивходами соответственно первого и второго перёмножителей,. причем выходы первой и второй линий задержки подключены . к входам соот ветственно первого и второго дешифраторов, а вторые входы первого и- второго дополнительных едоков памяти и входы первого и второго блоков памяти являются моду.ляционными входами устройства.

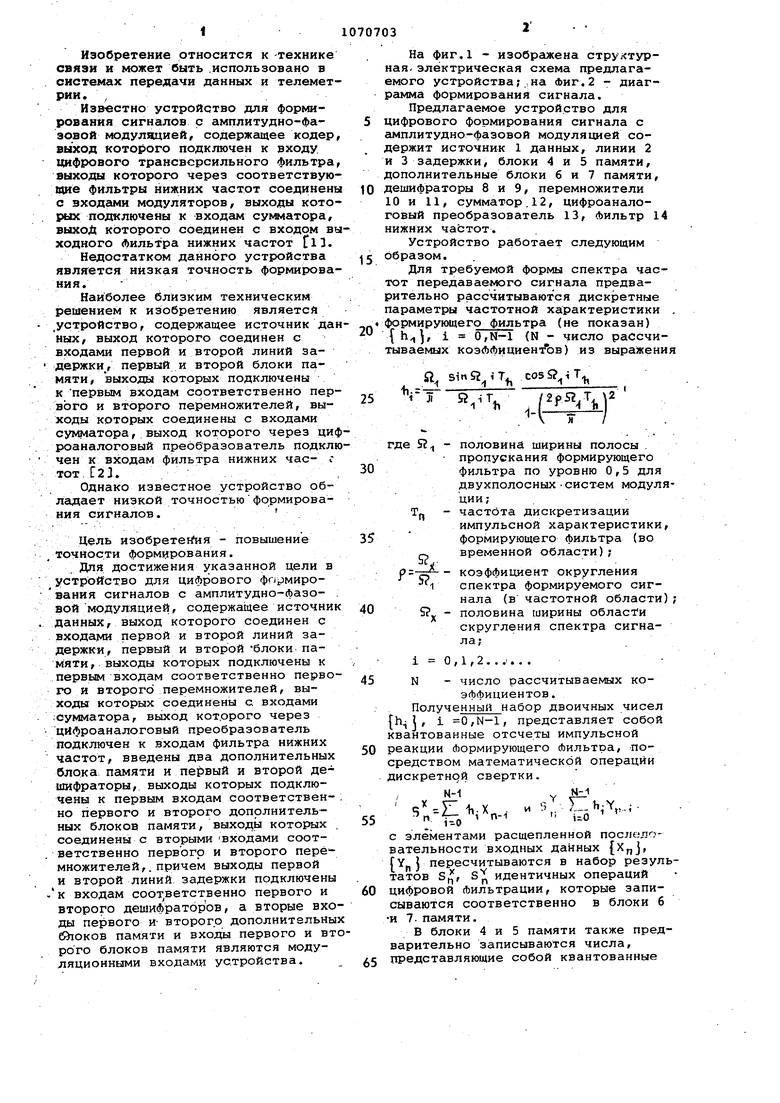

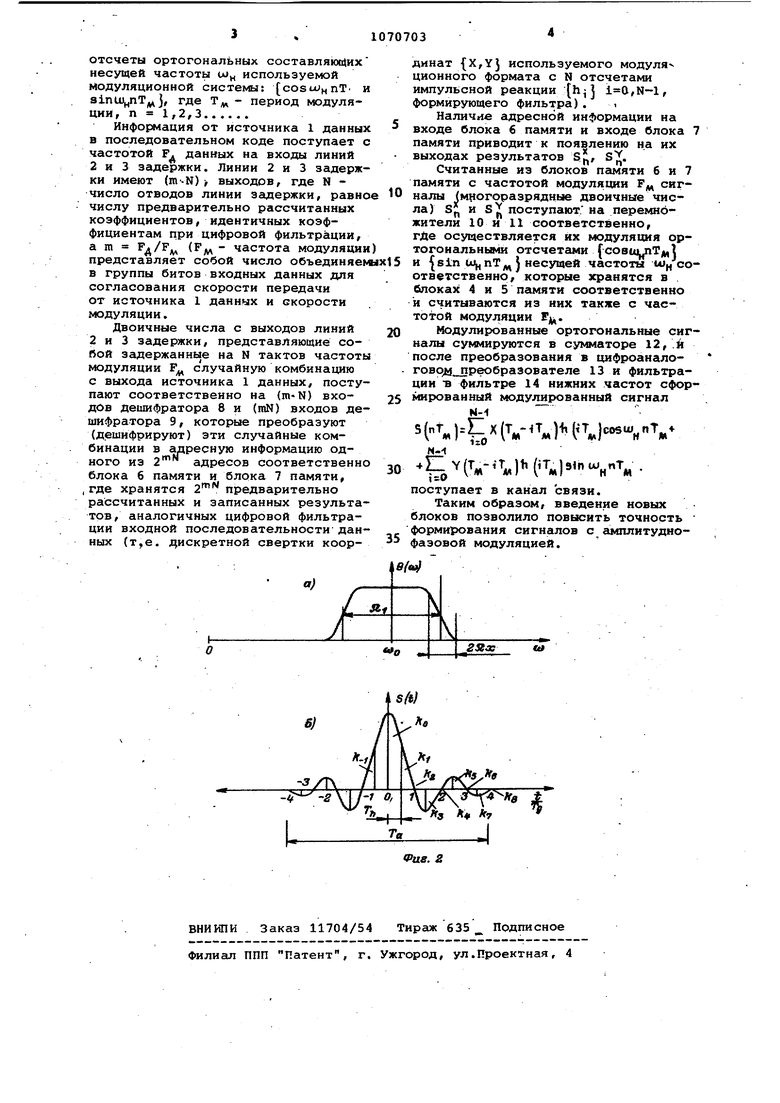

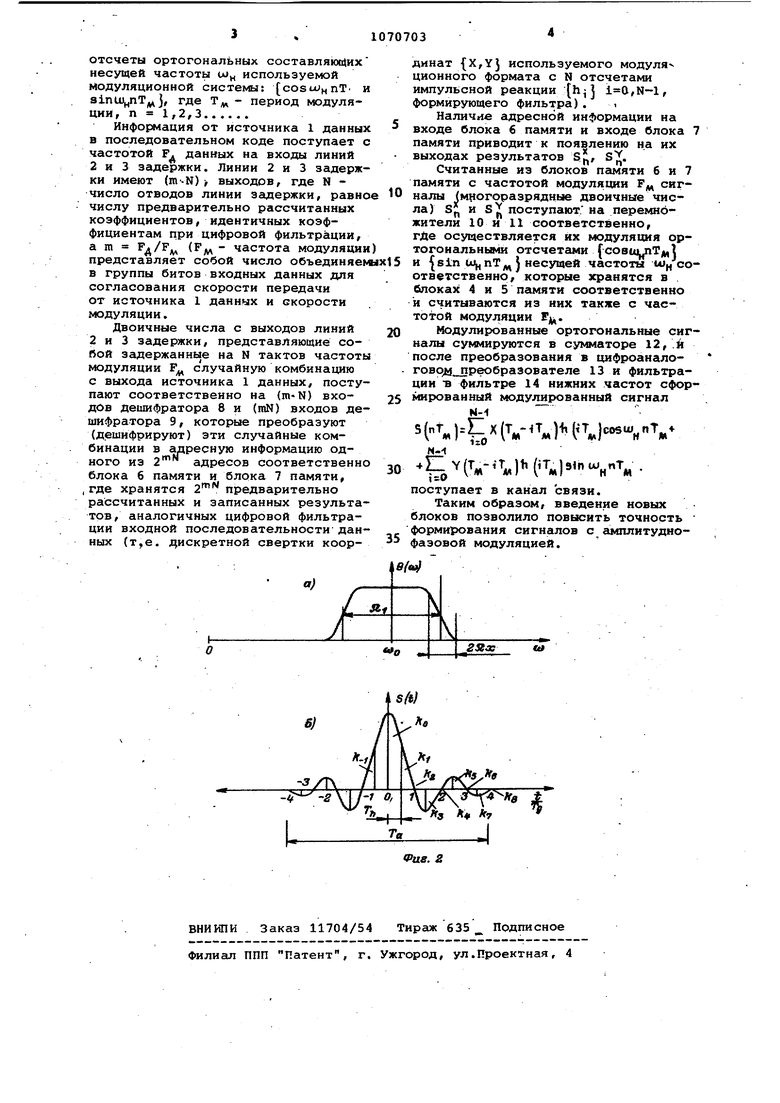

На фиг.1 - изображена стру.чтурная-электрическая схема предлагаемого устройства; на Фиг.2 - диаграмма формирования сигнала.

Предлагаемое устройство для 5 цифрового формирования сигнала с ё1мплитудно-фазовой модуляцией содержит источник 1 данных, линии 2 и 3 задержки, блоки 4 и 5 памяти, дополнительные блоки 6 и 7 памяти, 0 дешифраторы 8 и 9, перемножители 10 и 11, сумматор.12, цифроаналоговый преобразователь 13, сЬильтр 14 нижних частот.

Устройство работает следующим 5 образом.

Для требуемой формы спектра частот передавaei Dго сигнала предварительно рассчитываются дискретные параметры частотной характеристики . , 1ррмирующего фильтра (не показан) {h,, i 0, (N - число рассчитываемых коэЛЛициен-Лв) из выражения

fb. .

Ji S 1-Т,

4)

где S - половина ширины полосы . пропускания формирующего фильтра по уровню 0,5 для двухполосных-систем модуляции;Т - частота дискретизации

импульсной характеристики, формирующего фильтра (во -, временной области) ;

коэффициент округления спектра формируемого сигнала (в частотной области); х половина ширины области

скругления спектра сигнала;i 0,1,2,

N - число рассчитываемых коэффициентов.

Полученный набор двоичных чисел

tNj , i 0,N-1, представляет собой квантованные отсчеты импульсной 0 реакции Формирующего сЬильтра, лосредством математической операции дискретной свертки.

,

N-1

.Y

, и5„ элементами расщепленной последовательности входных данных YI, j пересчитываются в набор результатов S, S идентичных операций

0 цифровой Фильтрации, которые записываются соответственно в блоки б и 7. памяти.

В блоки 4 и 5 памяти также предварительно записываются числа,

5 представляющие собой квантованные отсчеты ортогональных составляющих несущей частоты ы„ используемой модуляционной системы: . sinuj T j, где Т - период модуляции ,п 1,2,3 ИнфОЕмация от источника 1 данны в последовательном коде поступает частотой Рд данных на входы линий 2 и 3 задержки. Линии 2 и 3 задерж ки имеют (mvN), выходов, где N число отводов линии задержки, равн числу предварительно рассчитанных коэффициентов, идентичных коэффициентам при цифровой фильтрации, а m Рд/Fj РМ частота модуляци представляет собой число объединяе в группы битов входных данных для согласования скорости передачи от источника 1 данных и скорости модуляции. Двоичные числа с выходов линий 2 и 3 задержки, представляющие собой задержанные на N тактов частот модуляции FU случайную комбинацию с выхода источника 1 данных, посту пают соответственно на (m-N) входов дешифратора 8 и (mN) входов де шифратора 9, которые преобразуют (дешифрируют) эти случайные комбинации в адресную информацию одного из 2 адресов соответственно блока б памяти и блока 7 памяти, , где хранятся предварительно рассчитанных и записанных результатов, аналогичных цифровой фильтрации входной последовательности данных (т,е. дискретной свертки коор«)

гяж ы динат {X,YJ используемого модуля ционного формата с N отсчетами импульсной реакции ,N-1, формирующего фильтра). Наличие адресной информации на входе блока 6 памяти и входе блока 7 памяти приводит к появлению на их выходах результатов S Считаниые из блоков памяти б и 7 памяти с частотой модуляции Рд сигналы (многоразрядиые двоичные числа) 8„ и S поступают. на перемножители 10 и 11 соответственно, где осуществляется их модуляция ортогональными отсчетсши (совиигТд, и sln J несущей частоты ш соответственно, которые хранятся в блоках 4 и 5 памяти соответственно и считываются из иих также с частотой модуляции Гд. Модулированные ортогональные сигналы суммируются в сумматоре 12,.и после преобразования в цифроаналоговол преобразователе 13 и фильтрации -в фильтре 14 нижних частот сфермированный модулированный сигнал )(V ) (ViT)t(iT)9inu,nT. поступает в канал связи. Таким образом, введение новых блоков позволило повысить точность ормирования сигналов с амплитудноазовой модуляцией. -.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| Многоканальное устройство обработки сложных сигналов | 1989 |

|

SU1704117A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1986 |

|

SU1438017A1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2313184C1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Устройство для передачи и приема многочастотных многопозиционных сигналов | 1988 |

|

SU1578835A1 |

| Цифровой формирователь сигналов с манипуляцией минимальным сдвигом | 1987 |

|

SU1494242A1 |

УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ФОРМИРОВАНИЯ СИГНАЛОВ С АМПЛИТУДНОФАЗОВОЙ МОДУЛЯЦИЕЙ, содержащее источник данных, выход которого соединен с входами первой и второй линий задержки, первый и второй Ллоки памяти, выходы которых подключены к первым входам- соответственно первого и второго перемножителей, выходы которых соединены с входами сумматора, выход которого через цифроаналоговый преобразователь подкршчен квходу фильтра нижних частот, отличающееся тем, что,, с целью повышения точности формирования, введены два дополнительных блока памяти и первый и второй деижфраторы, выходы которых подключены к первым входам соответственно первого и второго дополнительных блоков памяти, выходы которых соединены с вторыми входами соответственно первого и второго перемножителей, причем выходы первой и второй линий задержки под- § ключены к входам соответственно первого и второго дешифраторов, а /Л вторые входы первого и второго дополнительных блоков памяти и входы первого и второго блоков памяти являются модуляционными входами устройства. 1 О о со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Данилов Б.С | |||

| и др | |||

| Однополосная передача цифровых сигналов | |||

| М | |||

| , Связь, 1974, с.59 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Выполнение высокоскоростных модемов на Микро-ЭВМ | |||

| Экспресс-информация | |||

| Сер | |||

| Передача информации, М | |||

| , ВИНИТИ | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1984-01-30—Публикация

1981-12-25—Подача