Изобретение относится к электросвязи и может быть использовано для циклового фазирования в сеансных системах связи, в частности в высо- коскоростных системах передачи цифровой видеоинфЬр11аЦии.

Цель изобретения - повьпиение надежности и быстродействия установления циклового синхронизма.

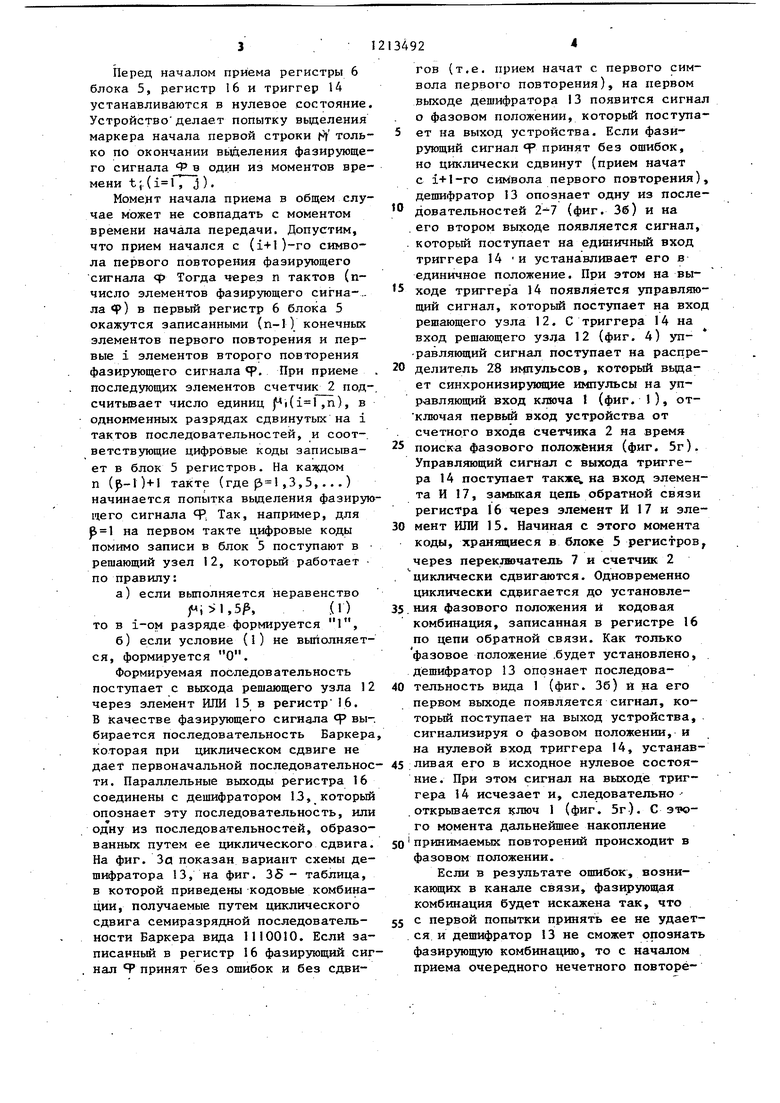

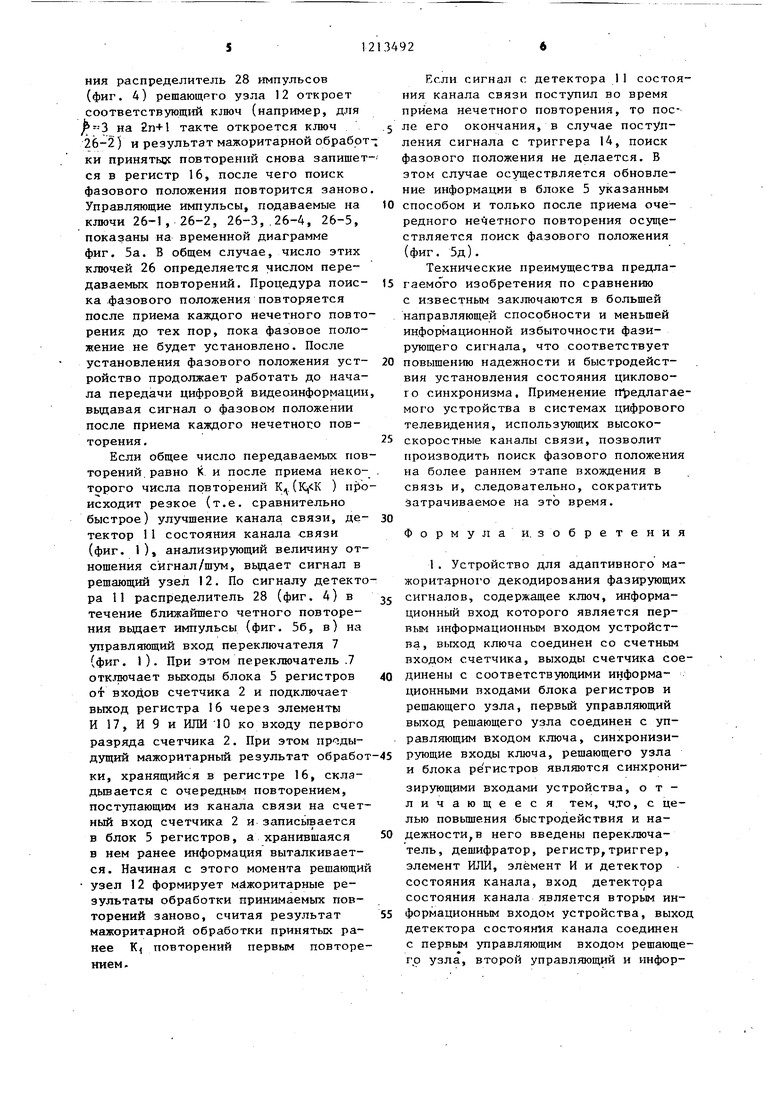

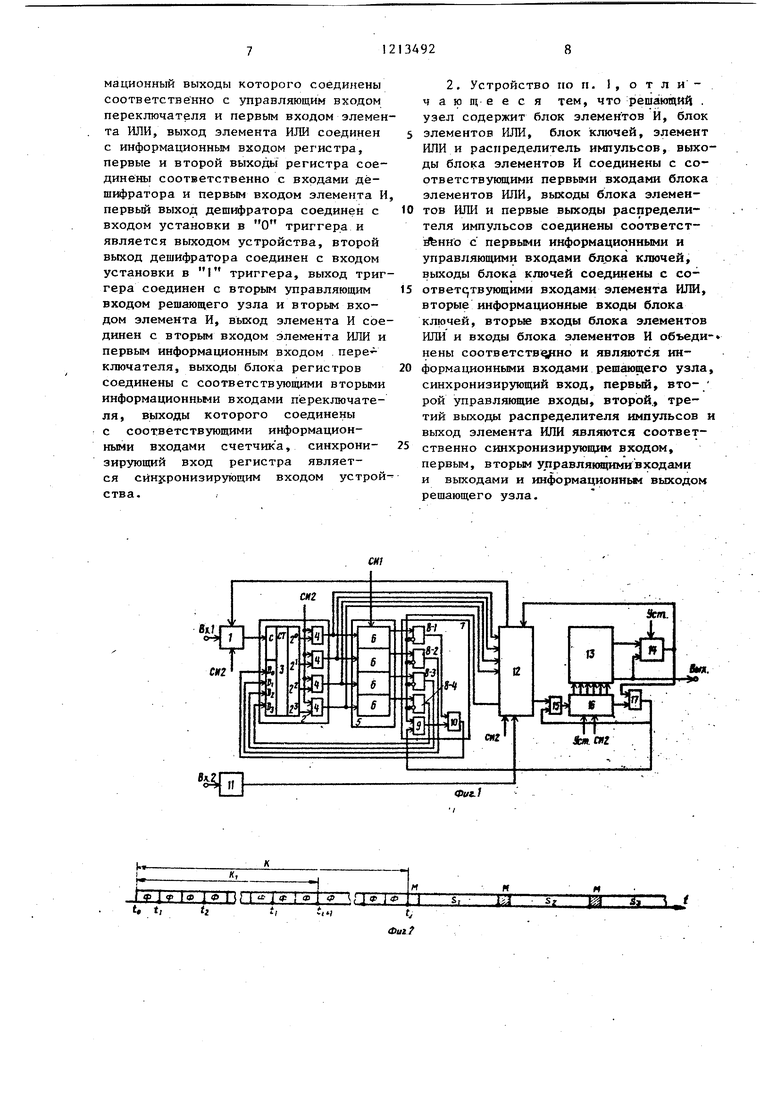

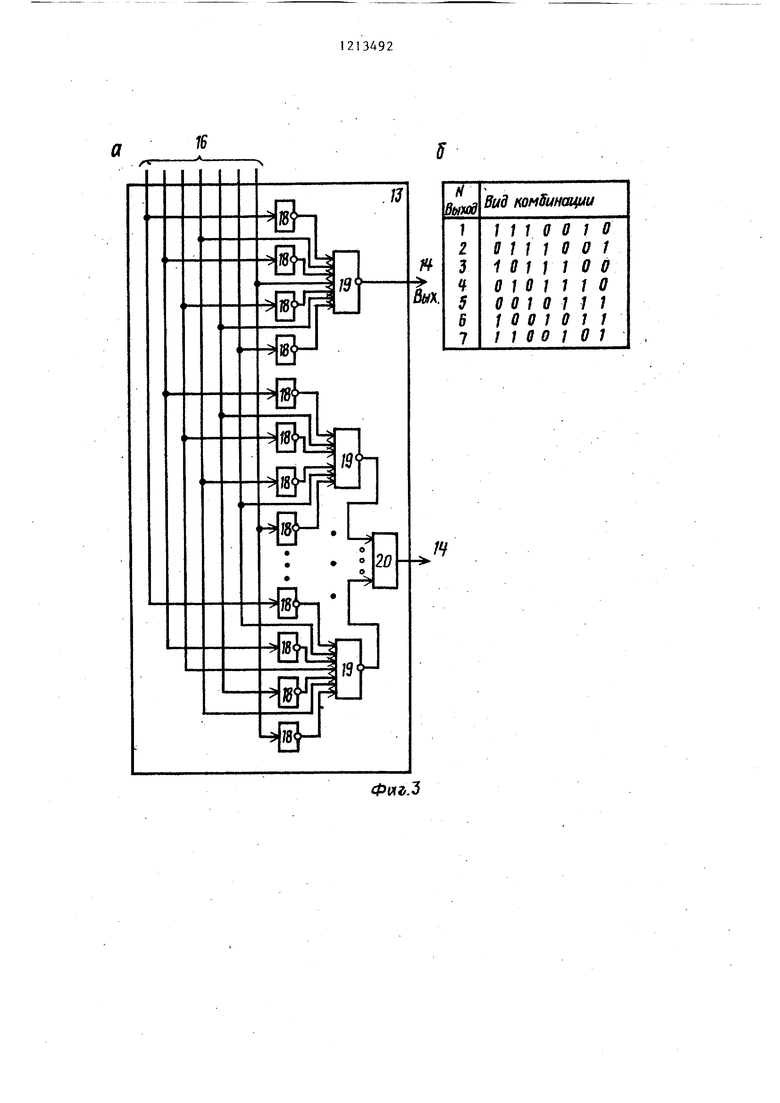

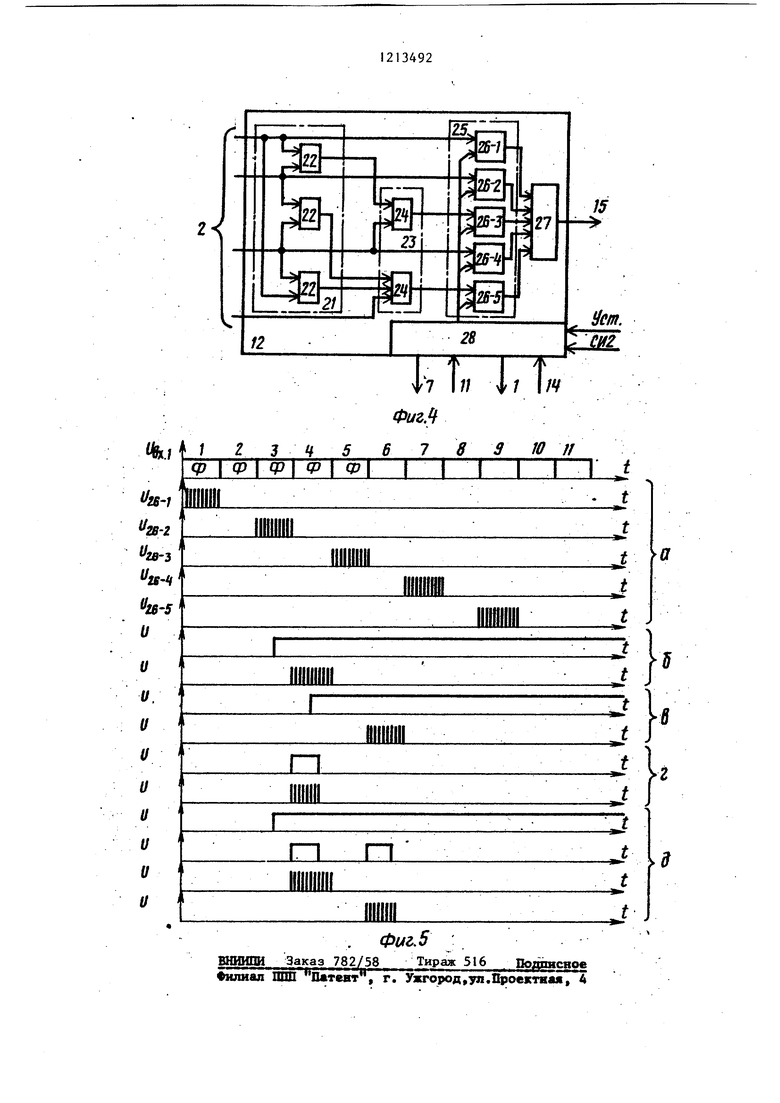

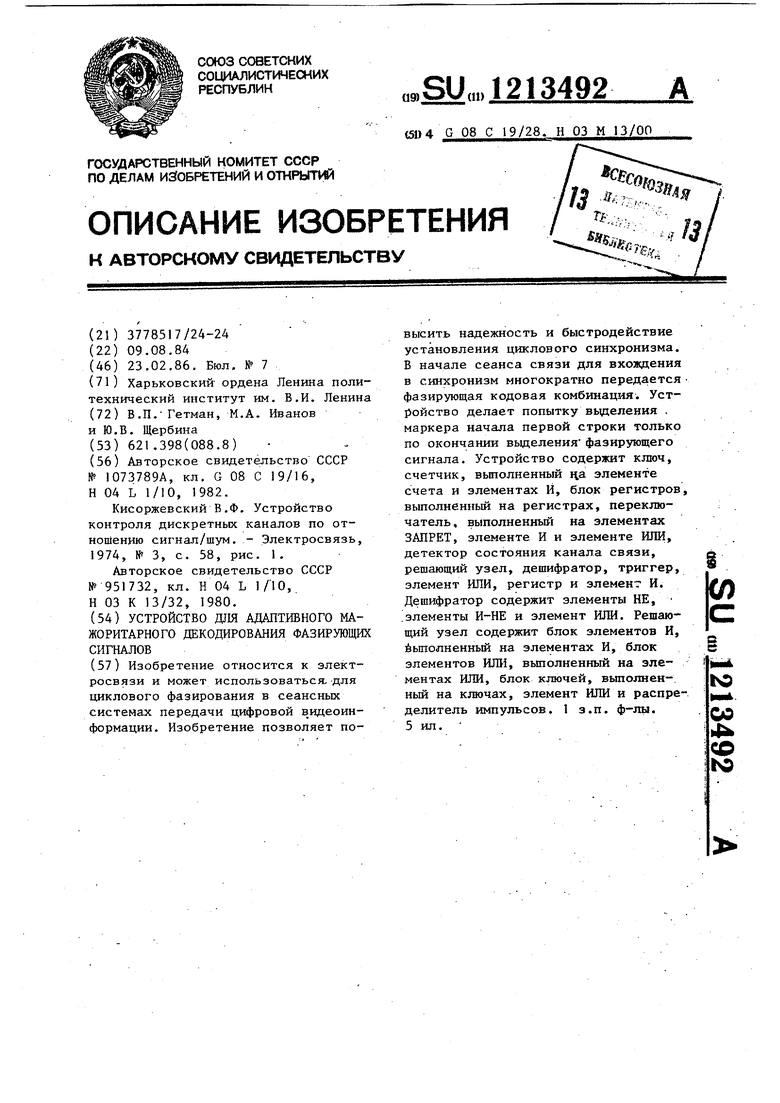

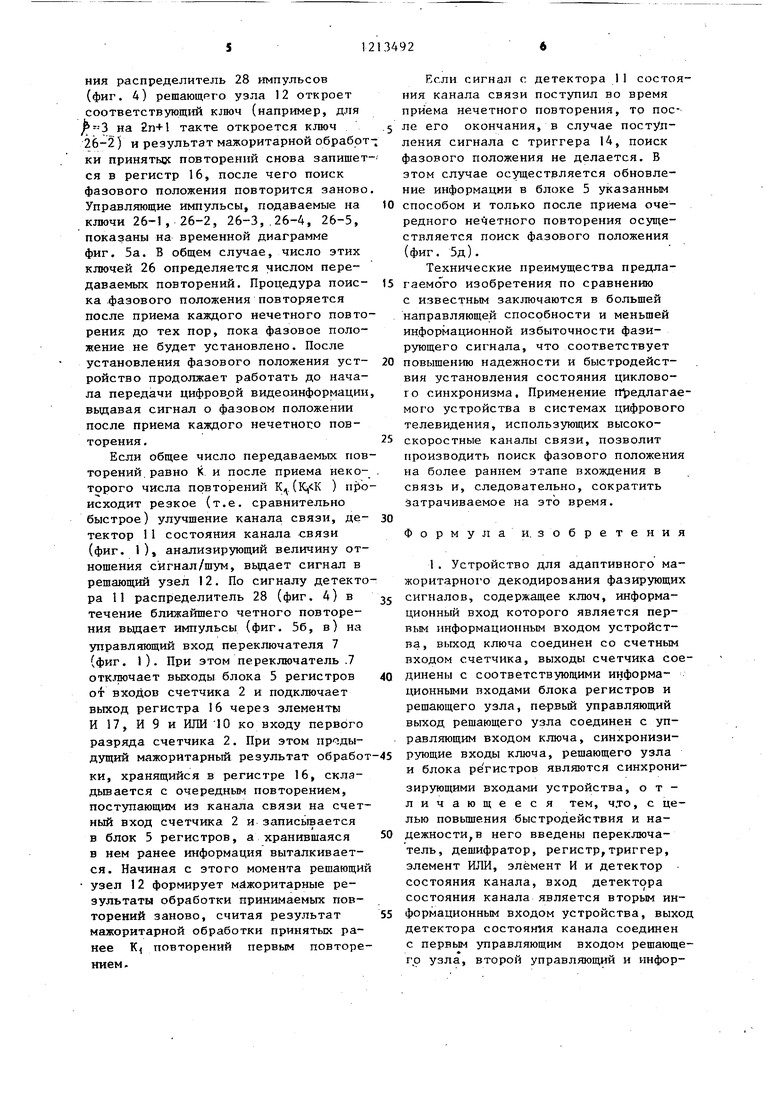

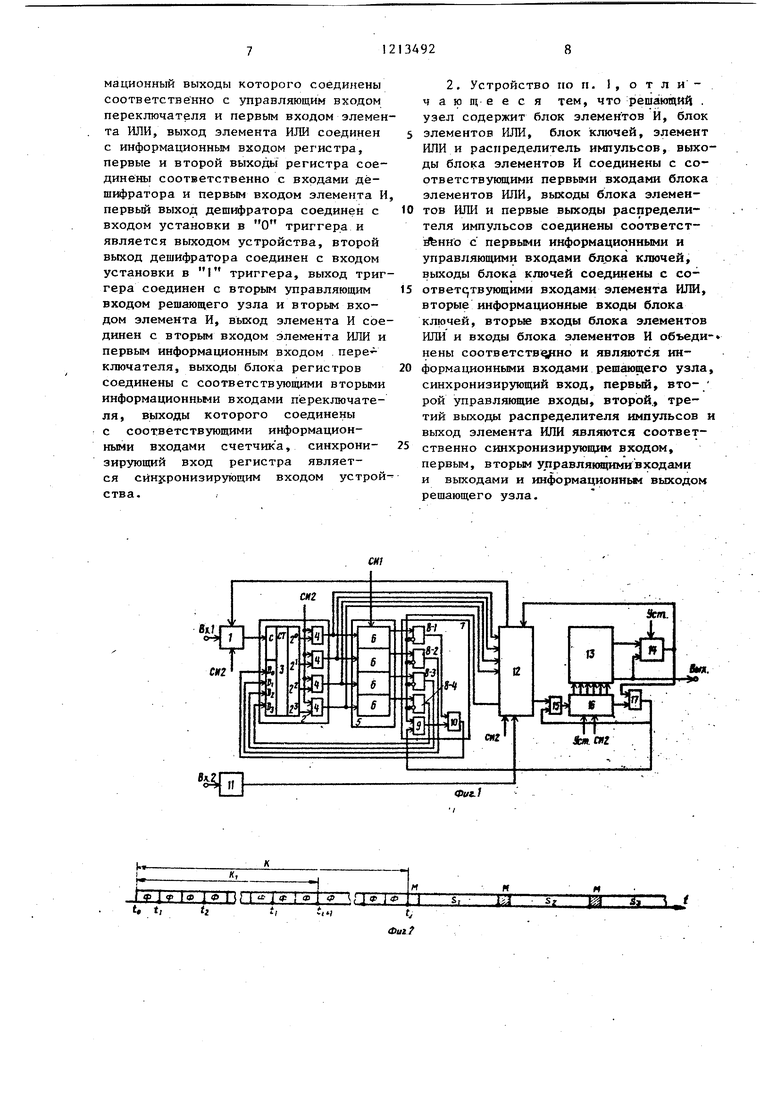

На фиг. 1 показана структурная схема устройства; на фиг. 2 - временная диаграмма, поясняющая принцип передачи информации в системах цифрового телевидения; на фиг. 3 - функциональная схема дешифратора; на фиг. 4 функциональная схема решающего узла; на фиг. 5 - временные диаграммы, поясняющие работу решающего узла.

Устройство для адаптивного мажори тарного декодирования фазирующих сигналов содержит (фиг. 1) ключ 1, счетчик 2, выполненный на элементе 3 счета и элементах И 4, блок-5 регистров, вьтолненный на регистрах 6, переключатель 7, выполненный на элементах ЗАПРЕТ 8, элементе И 9 и элементе ИЛИ 10, детектор 11 состояния канала связи, решающий узел 12, дешифратор 13, триггер 14, элемент ИЛИ 15, регистр 16 и элемент И 17.

Дешифратор 13 содержит (фиг. 3) элементы НЕ 18 элементы И-НЕ 19 и элемент ИЛИ 20.

Решающий узел 12 содержит (фиг. 4 блок 21 элементов И, выполненный на элементах И 22, блок 23 элементов ИЛИ, выполненный на элементах ИЛИ 24 блок 25 ключей, выполненный на ключах 26, элемент ИЛИ 27 и распределитель 28 импульсов.

Ключ 1 отключает счетный вход счетчика 2 от входа устройства по сигналу с решающего узла 12 на время поиска синхронного положения.

Счетчик 2 подсчитьшает число единиц . в одноименных разрядах принимаемых повторений фазирующего сигнала.

Блок 5 регистров содержит регистры 6 сдвига, число которых равно чис лу разрядов счетчика 2 и определяется максимальным числом передаваемых

ловт рений фазирующего сигнала Ф, а число разрядов каждого регистра 6 равно числу разрядов п в этом сигнале.

Решающий узел 12 формирует символы фазирующего сигнала Ф из кодов числа единиц ( п), хранящихся в блоке 5 регистров.

Дешифра:тор 13 опознает фазирующую кодовую комбинацию ср записанную в регистр 16, или одну из комбинаций, образующихся в этом регистре при ее циклическом сдвиге в случае, если в

них нет ошибок, и выдает сигнал о

фазовом положении на выход устройст- ва или сигнал об отсутствии фазового положения на единичный вход триггера 14..

Элементы ИЛИ 15 и И 17 формируют цепь обратной связи регистра 16 во время поиска фазового положения.

Регистр 16 сдвига предназначен для записи, хранения и переписи результатов мажоритарной обработки принимаемых повторений фазирующего сигнала.

Детектор 11 состояния канала связи анализирует величину отношения

сигнал/шум в канале связи и при резком его уменьшении (ниже заданного порога), вьщает управляющий сигнал в решающий узел 12.,

Детектор 11 состояния канала связи содержит сумматор, разделительную цепь, вычитатель, квадраторы, интеграторы и делитель. ,

Телевизионный сигнал (фиг. 2) представляет собой последовательно

передаваемые кодовые комбинации строк S l, перед каждой из которых передается маркер строкиМ. В нача- ле сеанса передачи для вхождения в связь многократно передается фазирующая кодовая комбинации Ф. Многократная передача фазирующего сигнала в начале сеанса обусловлена тем, что в системах цифрового телевидения используются каналы с вероятностью искажения элементарного символа , однако при вхождении в связь эта величина может быть значительно больше (Ро ). При этом улучшение качества канала

связи происходит не постепенно, начиная с момента вхождения в связь, а достаточно быстрым скачком в течение 10-20 символов после приема первых 100-150 символов при .

Такая ситуация характерна, например, для систем высокоскоростной связи.

Устройство работает следующим образом.

Перед началом приема регистры 6 блока 5, регистр 16 и триггер 14 устанавливаются в нулевое состояние. Устройство делает попытку вьщеления маркера начала первой строки ( только по окончании вьделения фазирующего сигнала Ф в один из моментов времени tj.( , j ).

MoMejiT начала приема в общем случае может не совпадать с моментом времени начала передачи. Допустим, что прием начался с (i+l)-ro символа первого повторения фазирующего сигнала р Тогда ч-ерез п тактов (п- число элементов фазирующего сигна-.. ла р) в первый регистр 6 блока 5 окажутся записанными (n-l) конечных элементов первого повторения и первые i элементов второго повторения фазирующего сигнала Р. При приеме последующих элементов счетчик 2 подсчитьшает число единиц ((,n), в одноименных разрядах сдвинутых на 1 тактов последовательностей, и соот-. ветствующие цифровые коды записывает в блок 5 регистров. На калдаом п (-1)+1 такте (где ,3,5,...) начинается попытка вьщеления фазирующего сигнала Ф, Так, например, для 1 на первом такте цифровые коды помимо записи в блок 5 поступают в решающий узел 12, который работает по правилу:

а)если вьшолняется неравенство

f«.l,5 ,(Г) то в i-oM разряде формируется 1,

б)если условие (1 ) не вьптолняет- ся, формируется О.

Формируемая пос-ледовательность поступает с выхода решающего узла 12 через элемент ИЛИ 15 в регистр 16. В качестве фазирующего сигнала ф выбирается последовательность Баркера которая при циклическом сдвиге не дает первоначальной последовательности . Параллельные выходы регистра 16 соединены с дешифратором 13, который опознает эту последовательность, или одну из последовательностей, образованных путем ее циклического сдвига. На фиг. За показан вариант схемы дешифратора 13, на фиг. 35 - таблица, в которой приведены кодовые комбинации, получаемые путем циклического сдвига семиразрядной последовательности Баркера вида 1110010. Если записанный в регистр 16 фазирующий сигнал Я принят без ошибок и без сдвигов (т.е. прием начат с первого символа первого повторения), на первом выходе дешифратора 13 появится сигнал о фазовом положении, который поступа- 5 ет на выход устройства. Если фазирующий сигнал Т принят без ошибок, но циклически сдвинут (прием начат с 1+1-го символа первого повторения), дешифратор 13 опознает одну из после- довательностей 2-7 (фиг. 36) и на . его втором вьпсоде появляется сигнал, . который поступает на единичный вход триггера 14 И устанавливает его в единичное положение. При этом на вы- 5 ходе триггера 14 появляется управляющий сигнал, который поступает на вход решающего узла 12. С триггера 14 на вход решающего узда 12 (фиг. 4) уп- равляющий сигнал поступает на распре- 0 делитель 28 импульсов, который выдает синхронизирующие импульсы на уп- р авляющий вход ключа 1 (фиг. 1), от- ключая первь вход устройства от счетного входа счетчика 2 на время 5 поиска фазового положения (фиг. 5г). Управляющий сигнал с выхода триггера 14 поступает также на вход элемента И 17, замыкая цепь обратной связи регистра 16 через элемент И 17 и эле- 0 мент ИЛИ 15. Начиная с этого момента коды, хранящиеся в блоке 5 регистров, через переключатель 7 и счетчик 2 циклически сдвигаются. Одновременно циклически сдвигается до установле- 5.ния фазового положения и кодовая комбинация, записанная в регистре 16 по цепи обратной связи. Как только фазовое положение .будет установлено, дешифратор 13 опознает последова- 0 тельность вида 1 (фиг. Зб) и на его первом выходе появляется сигнал, который поступает на выход устройства, сигнализируя о фазовом положении, и на нулевой вход триггера 14, устанав- 5:ливая его в исходное нулевое состояние. При этом сигнал на выходе триггера 14 исчезает и, следовательно .открьшается ключ 1 (фиг. 5г). С э-того момента дальнейшее накопление 0 принимаемых повторений пpoиcxoдиt в фазовом положении.

Если в результате ошибок, возникающих в канале связи, фазирующая комбинация будет искажена так, что 5 с первой попытки принять ее не удается и дешифратор 13 не сможет опознать фазирующую комбинацию, то с началом приема очередного нечетного повторения распределитель 28 импульсов (фиг. 4) решающего узла 12 откроет соответствующий ключ (например, для

3 на 2п+1 такте откроется ключ .5 26-2) и результат мажоритарной обработки принятых повторений снова запишет- ся в регистр 16, после чего поиск фазового положения повторится заново. Управляющие импульсы, подаваемые на 10 ключи 26-1, 26-2, 26-3,.26-4, 26-5, показаны на временной диаграмме фиг. 5а. В общем случае, число этих ключей 26 определяется числом передаваемых повторений. Процедура поис- 15 ка .фазового положения повторяется после приема каждого нечетного повторения до тех пор, пока фазовое положение не будет установлено. После установления фазового положения уст- 20 ройство продолжает работать до начала передачи цифровой видеоинформации, выдавая сигнал о фазовом положении после приема каждого нечетного повторения .25

Если общее число передаваемых повторений равно К и после приема неко- . торого числа повторений К, (К,К ) происходит резкое (т.е. сравнительно быстрое) улучшение канала связи, де- ЗО тектор 11 состояния канала связи (фиг. 1), анализирующий величину от- нощения сигнал/шум, вьщает сигнал в решающий узел 12. По сигналу детектора 11 распределитель 28 (фиг. 4) в s течение ближайшего четного повторения вьщает импульсы (фиг. 56, в) на управляющий вход переключателя 7 (фиг. 1). При этом переключатель .7 отключает выходы блока 5 регистров 40 от входов счетчика 2 и подключает выход регистра 16 через элементы И 17, И 9 и ИЛИ 10 ко входу первого разряда счетчика 2. При этом пр эды- дущий мажоритарный результат обработ-45 ки, хранящийся в регистре 16, скла- дьшается с очередным повторением, поступающим из канала связи на счетный вход счетчика 2 и записьшается в блок 5 регистров, а хранившаяся 50 в нем ранее информация выталкивается. Начиная с этого момента решающий

узел 12 формирует мажоритарные результаты обработки принимаемых повторений заново, считая результат 55 мажоритарной обработки принятых ранее К повторений первым повторением.

Если сигнал с детектора 11 состояния канала связи поступил во время приема нечетного повторения, то после его окончания, в случае поступления сигнала с триггера 14, поиск фазового положения не делается. В этом случае осуществляется обновление информации в блоке 5 указанным способом и только после приема очередного нечетного повторения ocynie- ствляется поиск фазового положения (фиг. 5д).

Технические преимущества предлагаемого изобретения по сравнению с известным заключаются в большей направляющей способности и меньшей информационной избыточности фазирующего сигнала, что соответствует повышению надежности и быстродействия установления состояния циклового синхронизма. Применение предлагаемого устройства в системах цифрового телевидения, использующих высокоскоростные каналы связи, позволит производить поиск фазового положения на более раннем этапе вхождения в связь и, следовательно, сократить затрачиваемое на это время.

Формулаи. зобретения

1. Устройство для адаптивного мажоритарного декодирования фазирующих сигналов, содержащее ключ, информационный вход которого является первым информационным входом устройства, выход ключа соединен со счетным входом счетчика, выходы счетчика соединены с соответствующими информационными входами блока регистров и решающего узла, пе-рвьш управляющий выход решающего узла соединен с управляющим входом ключа, синхронизирующие входы ключа, решающего узла и блока ре гистров являются синхронизирующими входами устройства, отличающееся тем, ч.то, с целью повьштения быстродействия и надежности, в него введены переключатель, дешифратор, регистр,триггер, элемент ИЛИ, элемент И и детектор состояния канала, вход детектора состояния канала является вторым информационным входом устройства, выхо детектора состояния канала соединен с первым управляющим входом решающего узла, второй управляющий и информационный выходы которого соединены соответственно с управляющим входом переключателя и первым входом элемента ИЛИ, выход элемента ИЛИ соединен с информационным входом регистра, первые и второй выходы регистра соединены соответственно с входами дешифратора и первым входом элемента И первый выход дешифратора соединен с входом установки в О триггера и является выходом устройства, второй вькод дешифратора соединен с входом установки в Г триггера, выход триггера соединен с вторым управляющим входом решающего узла и вторым входом элемента И, выход элемента И соединен с вторым входом элемента ИЛИ и первым информационным входом . пере ключателя, выходы блока регистров соединены с соответствующими вторыми информационными входами переключателя, выходы которого соединены с соответствующими информационными входами счетчик а, синхрони- зирующий вход регистра является синхронизирующим входом устрой ства.

2. Устройство по п. 1, о т л и - чающееся тем, что решающий . узел содержит блок элементов И, блок элементов ИЛИ, блок ключей, элемент ИЛИ и распределитель импульсов, выходы блока элементов И соединены с соответствующими первыми входами блока элементов ИЛИ, выходы блока элементов ИЛИ и первые выходы распределителя импульсов соединены соответст- rifeHHo с первыми информационными и управляющими входами блока ключей, выходы блока ключей соединены с со- ответцтвующими входами элемента ИЛИ, вторые информационные входы блока ключей, вторые входы блока элементов ИЛИ и входы блока элементов И объединены соответств но и являются информационными входами решающего узла, синхронизирующий вход, первый, вто- рой управляющие входы, второй, третий выходы распределителя импульсов и выход элемента ИЛИ являются соответственно синхронизирующим входом, первым, вторым управ л якицими в ходами и выходами и информационным выходом решающего узла.

Фиг.З

%.

IS l %-2

гв-ъ и-ч

ff26 5

и

и

и. и

и а и и и

ф7 Ь/ 4/ I/V

Фиг.

1 г 345678 3 to П Ф I Ф| Ф| Ф| Ф| I I I I i

IDIIIIIIL

t

Г

л

П П

t

а

л

ВНИИт Заказ 782/58

Филиал ШШ Патент, г. Ужгород,ул.Проектная, k

Фич,5 .

Тираж 516 ПоАроисяое

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Устройство для приема трехкратно повторяемых команд управления | 1986 |

|

SU1385309A1 |

| Устройство для приема многократно повторяемых команд | 1984 |

|

SU1226510A1 |

| Устройство для приема трехкратноповторенных команд телеуправления | 1977 |

|

SU720775A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВЫХ ПОТОКОВ | 1992 |

|

RU2054809C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ | 1991 |

|

RU2023348C1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1988 |

|

SU1555902A2 |

Изобретение относится к электросвязи и может использоваться- для циклового фазирования в сеансных системах передачи цифровой в идеоин- формации. Изобретение позволяет повысить надежность и быстродействие установления циклового синхронизма. В начале сеанса связи для вхождения в синхронизм многократно передается фазирующая кодовая комбинация. Устройство делает попытку вьзделения . маркера начала первой строки только по окончании выделения фазирующего сигнала. Устройство содержит ключ, счетчик, выполненный ца элементе счета и элементах И, блок регистров, выполненный на регистрах, переключатель, выполненный на элементах ЗАПРЕТ, элементе И и элементе ИЛИ, детектор состояния канала связи, решающий узел, дешифратор, триггер, элемент ИЛИ, регистр и элемент И. Дешифратор содержит элементы НЕ, элементы И-НЕ и элемент ИЛИ. Решающий узел содержит блок элементов И, выполненный на элементах И, блок элементов ИЛИ, вьшолненный на элементах ИЛИ, блок ключей, выполнен-, ный на ключах, элемент ИЛИ и распределитель импульсов. 1 з.п. ф-лы. 5 ил. 8 § ю 00 4 СО К9

| Устройство для поворота вала фазорегулятора ртутного выпрямителя | 1943 |

|

SU73789A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Кисоржевский В.Ф | |||

| Устройство контроля дискретньк каналов по отношению сигнал/шум | |||

| - Электросвязь, 1974, № 3, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1980 |

|

SU951732A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-02-23—Публикация

1984-08-09—Подача