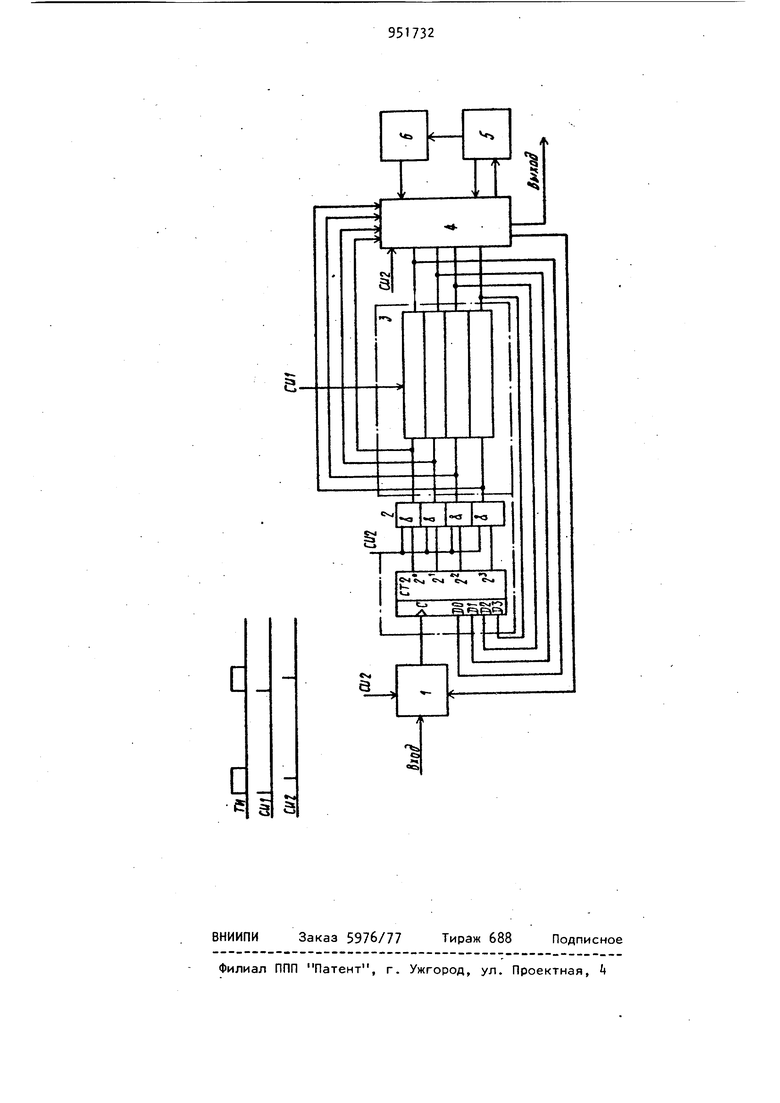

ключ подключен второй вход элемента ИЛИ второго канала, выход которого подключен к второму входу элемента ИЛИ третьего канала, первый вход которого подключен к второму входу элемента ИЛИ первого канала, третий вход которого подключен к второму входу элемента И второго кана.ла и через шестой ключ к шестому входу дополнительного элемента ИЛИp Однако известное устройство обладает ограниченностью функциональных возможностей, проявляющейся в том, что оно не может осуществлять цикло вое фазирование принимаемой информации. Это снижает помехоустойчивость, так как приводит к потере информации или к приему искаженных сообщений. Целью изобретения является повышение помехоустойчивости. Для достижения этой цели в устройство для адаптивного мажоритарно го декодирования телемеханических дублированных сигналов, содержащее два регистра сдвига, первый элемент И и решающий блок, два элемента И, третий регистр сдвига и последоватег льно соединенные ключ и источник, выходы которого подключены к первым входам элементов И, объединенные вторые входы .которых подключены к сбросовому входу ключа, к управляющему входу которого подключен выход решающего блока, при этом выходы регистров сдвига подключены.ко входа решающего блока и установочным входа счетчика, а выходы элементов И соответственно подключены ко входам реги стров сдвига и дополнительным входам решающего блока, при этом решающий блок выполнен в виде трех каналов, каждый из которых состоит из последовательно соединенных переключателя элемента И, элемента ИЛИ и ключа, причем выход ключа каждого из канало подключен ко входам дополнительного элемента ИЛИ, при этом во второй канал введен дополнительный элемент И включенный между выходом элемента и вторым входом элемента ИЛИ, а второй вход дополнительного элемента И объединен с первым входом элемента И первого канала и вторым входом элемента И третьего канала, второй : вход элемента И первого канала объединен с первым входом элемента И вто рого канала и через четвертый ключ подключен к четвертому входу дополнительного элемента ИЛИ, к пятому входу которого через пятый ключ подключен второй вход элемента ИЛИ втор рого канала, выход которого подключен к второму входу элемента ИЛИ третьего канала, первый вход которого подключен к второму входу элемента ИЛИ первого канала, третий вход которого подключен к второму входу элемента И второго канала и через шестой ключ к шестому входу дополнительного элемента ИЛИ, введены последовательно со1единенные анализатор фазирующего сигнала и селектор, выход которого подсоединен к первому дополнительному входу решающего блока, второй дополнительный вход которого является вторым выходом анализатора фазирующегосигнала, вход которого подключен к дополнительному выходу решающего блока. На чертеже приведена структурная электрическая схема предложенного устройства. Устройство содержит ключ 1, счет|чик 2, накопитель 3, решающий блок Ц, анализатор 5 фазирующего сигнала и селектор 6. Устройство работает следующим образом. Ключ 1 открывается, когда устанавливается факт начала поступления информации (например, по выделению несущей частоты и др.). Этот момент в общем случае может не совпадать с началом приема первого элемента принимаемого подблока. Допустим устройство начало работать с момента приема (H-l)-ro элемента. Тогда через п тактов в первый регистр накопителя 3 через счетчик 2 сначала записывается (п-1) конечных элементов первого подблока и затем I начальных элементов второго подблока. При приеме последующих элементов счетчик 2 подсчитывает число единиц V; (j 1, 2, ... n) в одноименных элементах, сдвинутых на i тактов последовательностях и соответству,ющие цифровые коды записывает в накопитель 3. На каждом п()+1 такте (где , 3, 5, ... к) начинается попытка выделения сигнала циклового фазирования. Так, например, для i 1 на 2п+1 такте цифровые коды, помимо записи в накопитель 3, поступают в решающий блок t, который работает следующим образом:

а)если выполняются неравенства 0,5(,5P или Vp2,5(i (1) то в J-OM разряде фазирующего сигнала формируется

б)при невыполнении неравенств

(1)формируется О, формируемая последовательность

поступает в анализатор 5 фазирующего сигнала. Если ошибки отсутствуют, то анализатор 5 идентифицирует сформированную в блоке последовательность, как фазирующую, однако сдвинутую на I-тактов. На такое же число тактов сдвинуты цифровые коды, а следовательно, и сообщение в накопителе 3- Последовательно, прежде чем начать выделен сообщения, необходимо цифровые коды в накопителе 3 циклически сдвинуть на (n-i) тактов, чтобы однознано зафиксировать начало сообщения. Для этого при выделении фазирующего сигнала анализатор 5 формирует управляющий сигнал, который поступает через решающий блок k на ключ 1, закрывая его. Информация на вход счетчика 2 прекращает поступать и цифровые коды с выхода накопителя через счетчик 2 перезаписываются на вход накопителя 3 без изменени:я. Одновременно и синхронно с циклической перезаписью цифровых кодов селектор 6 отслеживает фазовое положение сигнала циклового фазирования. Этот процесс продолжается до момента, когда селектор 6 зафиксирует заданную (начальную) фазу. Тогда сигнал с выхода селектора 6 поступает в решающий блок , который начинает работать по прави;лу:

а)если выполняется неравенство

Mj- 1,5Р (2 то в J-OM разряде сообщения формируется

б)при невыполнении неравенства

(2)формируется О.

В рассматриваемом случае () сформированное сообщение выводится на выход устройства.

Если в принятых подблоках имеют место ошибки (при |Ь 1), то фазирующий сигнал не будет выделен и устройство продолжает прием последующих подблоков. На 8п+1 такте () осуществляется вторая попытка выделения фазирующего сигнала с исправлением части ошибок. При этом сформированная из цифровых кодов по правилу (1)

nocлeдoвateльнocть поступает в анализатор 5- Если все ошибки были исправлены правильно, что анализатор 5 идентифицирует сформированную

в блоке 4 последовательность, как фазирующую. При этом через блок k подается управляющий сигнал на ключ 1, который закрывается. Осуществляется циклический сдвиг цифровых кодов

в накопителе 3 и поиск начальной фазы фазирующего сигнала аналогично рассмотренному ранее. В момент выделения начальной фазы селектор 6 формирует управляющий сигнал, который изменяет режим работы решающего блока 4. Сообщение формируется по правилу (2) из цифровых кодов, поступающих из накопителя k, и выдается на выход устройства.

Если в принятых подблоках () имеют место неисправляемые ошибки, то фазирующий сигнал не будет выделен и продолжается прием последующих

подблоков.

На Itn+l также () осуществляется третья попытка вь деления фазирующего сигнала с исправлением ошибок большей кратности. При этом сформированная по правилу (1) последовательность поступает в анализатор 5. Если все ошибки были исправлены правильно, то анализатор 5 идентифицирует сформированную последовательность как фазирующую. При этом закрывается ключ 1, осуществляется циклический сдвиг цифровых кодов в накопителе 3 и поиск начальной фазы фазирующего сигнала. При выделении начальной фазы селектор 6 изменяет

режим работы решающего блока , и

сообщение, сформированное () ,по правилу (2) , Лоступает на выход устройства.

Таким образом, предложенное устi ройство обладает более высокой технико-экономической эффективностью, чем известное. Известное устройство позволяет подвергать мажоритарной обработке кодовые слова, начало которых известно. Предлагаемое устройство дополнительно подвергает мажоритарной обработке кодовые слова, прием которых может быть начат в произвольный момент времени и, следрвательно, начало кодовых слов неизвестно. Это расширяет функциональные возможности устройства и повышает помехоустойчивость, так как устройство становится малочувствительным к ошибкам, нарушающим фазирование по циклам. Если в известном устройстве ни няя граница вероятности сбоя фазирования Рф определяется вероятностью искажения одного элемента Р, т в предлагаемом устройстве вероятнос сбоя фазирования оценивается выраже нием Рл о НТО в rj раз меньше, чем в известном устройстве, а именно И т EФj :vpЧO ц-) 27 если PC, 10 , V| 20, то к 10 Формула изобретения Устройство для адаптивного мажоритарного декодирования телемехани8ческих дублированных сигналов по авт, св. ff , .отличающееся тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные анализатор фазирующего сигнала и селектор, выход которого подсоединен к первому дополнительному входу решающего блока, второй дополнительный вход которого является вторым выходом анализатора фазирующего сигнала, вход которого подключен к дополнительному выходу решающего блока. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 88ifl63, кл.. Н Qi L 1/10, 1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство для приема трехкратноповторенных команд телеуправления | 1977 |

|

SU720775A1 |

| Устройство для адаптивного мажоритарного декодирования фазирующих сигналов | 1984 |

|

SU1213492A1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Устройство для исправления ошибок дискретной информации | 1977 |

|

SU690640A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| Устройство для передачи и приема дискретной информации | 1982 |

|

SU1072271A1 |

Авторы

Даты

1982-08-15—Публикация

1980-01-11—Подача