Изобретение относится к области функциональной электроники и предназначено для производства полупроводниковых интегральных схем (ИС).

Использование принципов нейронных сетей является одним из перспективных направлений развития вычисли,тельных устройств для ЭВМ. Например,

известна модель нейрона, которая содержит входы, выходы и сумматор, осуществлянмдий сложение возбуждающих и тормозящих сигналов. Недостатком такого интегрального нейрона является то, что сумматор в ней .выполнен на операционном усилителе, что при изменении температуры приводит к

сильному дрейфу его характеристик, резко увеличивающему ошибку при сложении сигналов. Для компенсации характеристик используют очень сложные термостабилизирующие цепочки, сводящие на нет преимзга1ества нейронов в качестве очень компактных элементов.

Недостатком также является низкая помехоустойчивость и невысокие функциона:льные возможности.

Наиболее близким по своей технической сущности является интегральный нейрон, включающий шину питания. возбуждающие и тормозящие входы, сум- g матор, вьтолненный на основе переключающих транзисторов, и выход. Известный интегральный нейрон имеет невысокие функциональные- возможности из-за низкой помехоустойчивости и невозможности выполнения большого числа входов (10-20), ограничиваемого коэффициентом усиления переключающих транзисторов (обычно не более 20-100). При традиционной реализации интегрального на основе, например, И Л-элементов, многовходовый сумматор занимает большую площадь кристалла, на которой не может быть размещено более 10.,,10 сумматоров при существующих допусках Кроме того, такой сумматор не сможет усиливать сигнал, для усиления jcOToporo на большом числе выходов потребуется существенное усложнение схемы ячейки и резкое увеличение ее размеров. Низкая нагрузочная способность нейрона не позволяет реализовать большое число связей. Цель изобретения - расширение функциональ-ньп4 возможностей. Это достигается тем, что В известном интегрсшьном нейроне, включаю щем шину питания, возбуждающие и то МОзящие входы, сумматор, выполненны на основе переключающих транзисторо

и выход в нейрон дополнительно введены шина питания и два сумматора, при этом все три сумматора имеют выходы, свои входные, выходные и расположенные между ними буферные транзисторы, выполненные в виде биполярных транзисторов с плазменной связью в общем высокоомном полупроводнике, причем первый и второй сумматоры имеют общие возбуждающие транзисторы, эмиттеры которых подсоединены к возбуждающим входам, эмиттеры выход-. ных транзисторов всех трех сумматоров соединены с соответствующими выходами, через нагрузочные резисторы подключены к первой шине питания и через шунтирующие резисторы соединены с базами этих же транзисторов, эмиттеры буферных транзисторов первого и второго сумматоров через первые щунтирующие резисторы соединены с базами этих же транзисторов и через нагрузочные резисторы подключены ко второй шине питания, эмиттеры буферных транзисторов третьего сумматора через вторые шуйтирующйе резисрезистор 13 подключены к первой шине питания 33. При этом эмиттер 10 выходного транзистора в первом сумматоре подключен к выходу 1, а эмиттеры 1 li и 12 выходных транзисторов во втором и третьем сумматорах подключены соответственно к выходам 2 и 3, Каждый сумматор содержит также

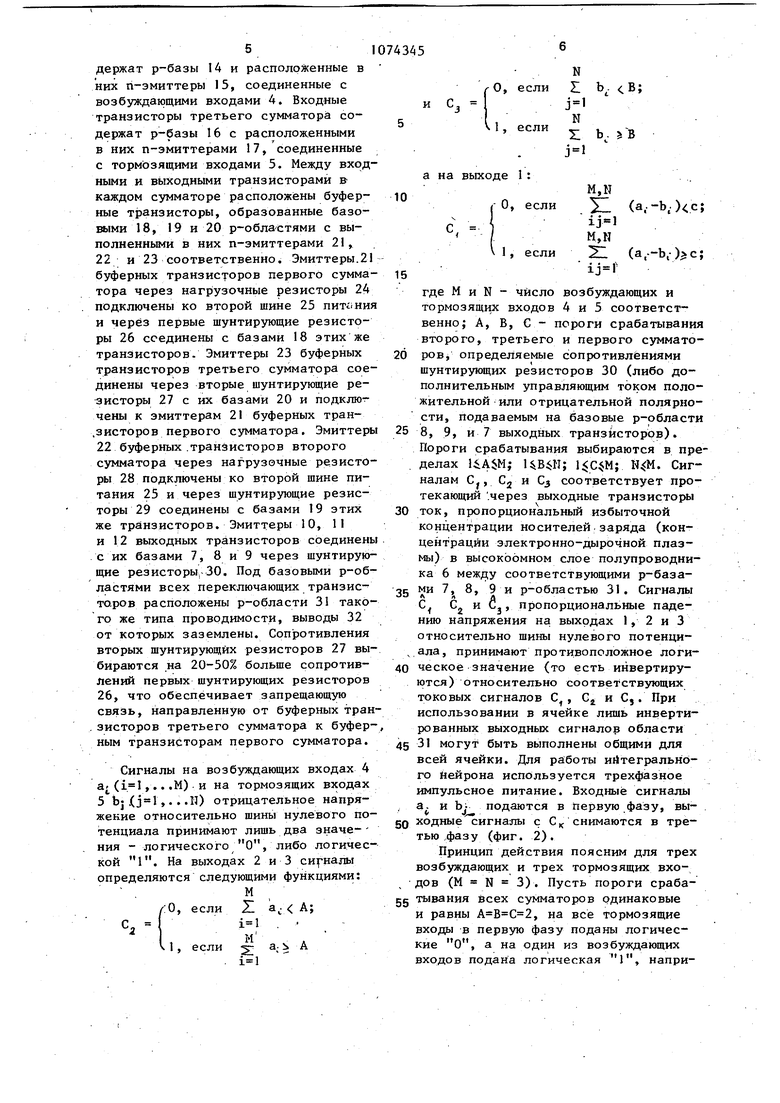

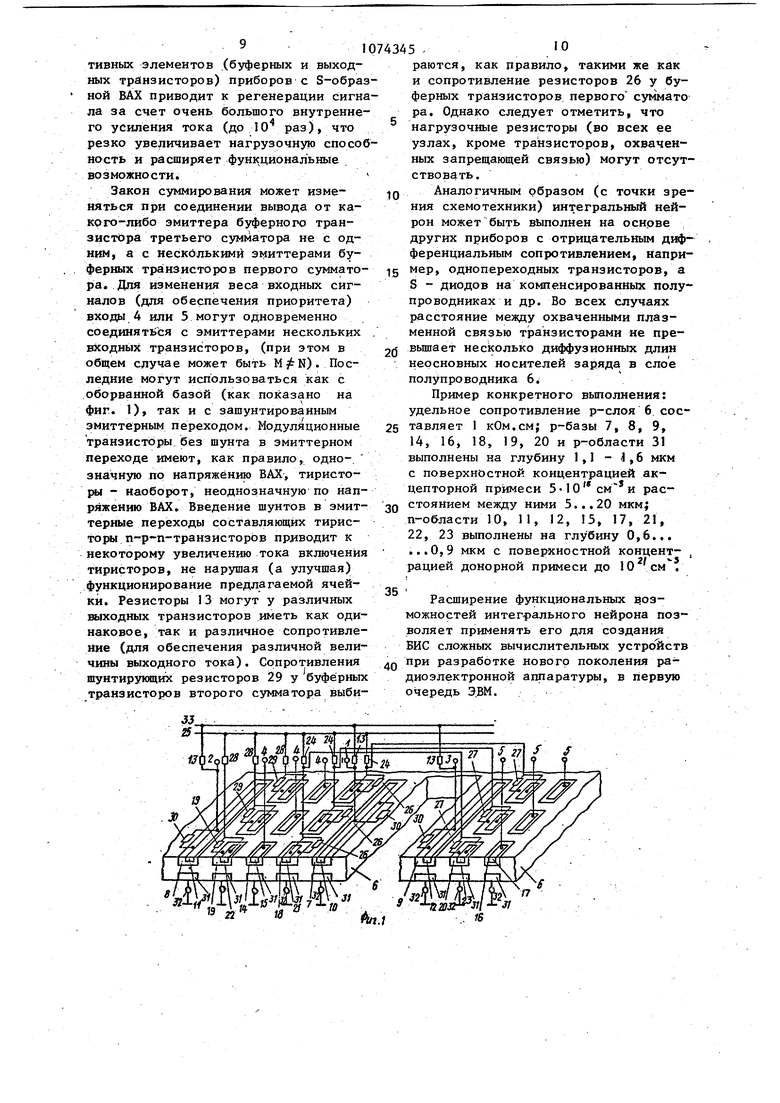

входные и буферные транзисторы, имеющие общую зону влияния с -соответствующими выходными транзисторами. Входные транзисторы первого и второго сумматора являются общими и соторы соединены с базами этих же транзисторов и подключены к эмиттерам соответствующих буферных транзисторов первого сумматора, причем сопротивление вторых шунтирующих резисторов превьш1ает сопротивление шунтирующих-резисторов по крайней мере на 20-50%, эмиттеры возбуждающих транзисторов третьего сумматора подсоединены к тормозящим входам, В качестве перекл1рчающих биполярных транзисторов могут бЫть использованы модуляционные транзисторы шш совмещенные дополняющие п-р-п и р-п-р Транзисторы (тиристоры), I . На фиг. 1 представлен общий вид (с разрезом) интегрального нейрона; на фиг. 2 - временные диаграммы работы интегрального нейрона при пяти различных комбинациях входных сигналов. Интегральный нейрон содержит три выхода , возбуждающие входы 4 и тормозящие входы 5, три сумматора, выполненные на переключающих биполярных транзисторах с плазменной связью в общем высокоомном полупроводник;е 6, Каждьй из трех сумматоров включает выходной транзистор с р-базами 7, 8 и 9 и п-эмиттерами 10, П и 12 соответственно, эмиттеры выходных транзист-оров через нагрузочный 5 держат р-базы 14 и расположенные в них п-змиттеры 15, соединенные с возбуждающими входами 4. Входные транзисторы третьего сумматора содержат р-базы 16 с расположенными в них п-эмиттерами 17, соединенные с тормозящими входами 5. Между входными и выходными транзисторами в каждом сумматоре расположены буферные транзисторы, образованные базовыми 18, 19 и 20 р-обла стями с выполненными в них п-эмиттерами 21, 22 и 23 соответственно. Эмиттеры.21 буферных транзисторов первого сумматора через нагрузочные резисторы 24 подключены ко второй шине 25 и через первые щунтирующие резисторы 26 соединены с базами 18 этих же транзисторов. Эмиттеры 23 буферных транзисторов третьего сумматора соединены через вторые щунтирующие резисторы 27 с их базами 20 и подклюгчены к эмиттерам 21 буферных тран.зисторов первого сумматора. Эмиттеры 22 бз ферных .транзисторов второго сумматора через нагрузочные резисторы 28 подключены ко второй щине питания 25 и через шунтирующие резисторы 29 соединены с базами 19 этих же транзисторов. Эмиттеры 10, 11 и 12 выходных транзисторов соединены с их базами 7, 8 и 9 через шунтирующие резисторы,-30. Под базовыми р-областями всех переключающих транзисторов расположены р-области 31 такого же типа проводимости, выводы 32 от которых заземлены. Сопротивления вторых щунтирующйх резисторов 27 выбираются на 20-50% больше сопротивлений первых шунтирующих резисторов 26, что обеспечивает запрещающую связь, направленную от буферных тран . зисторов третьего сумматора к буферным транзисторам первого сумматора. Сигналы на возбуждающих входах 4 а(,...М) и на тормозящих входах 5 bj jCj l,.. .11) отрицательное напряжение относительно шины нулевого потенциала принимают лишь два значе- ния - логического О, либо логической 1. На выходах 2 и 3 сигналы определяются следующими функциями: 21 а А; :0, если i 1 . 1, если 5 b В; о, если j 1, если а на выходе 1 (- О, если 1, если где М и N - число возбуждающих и тормозящих входов 4 и 5 соответственно; А, В, С - пороги срабатывания второго, третьего и первого сумматоров, определяемые Сопротивлениями шунтирующих резисторов 30 (либо дополнительным управляющим током положительной или отрицательной полярности, подаваемым на базовые р-области 8, 9, и 7 выходных транзисторов). Пороги срабатывания выбираются в пределах . Сигналам Cj, Су я Сз соответствует протекающий .через выходные транзисторы ток, пропорциональный избыточной концентрации носителей заряда (концентрации электронно-дырочной плазмы) в высокоомном слое полупроводника 6 между соответствующими р-базами 7, 8, 9 и р-областью 31. Сигналы С Cj и Cj, пропорциональные падению напряжения на выходах 1,2 и 3 относительно ткаы нулевого потенциала, принимают противоположное логическое значение (то есть инвертируются) относительно соответствующих токовых сигналов С, С и С,. При использовании в ячейке лишь инвертированных выходных сигналов области 31 могут быть выполнены общими для всей ячейки. Для ра;боты ийтегрального йейрона используется трехфазное импульсное питание. Входные сигналы а и bj подаются в Первую фазу, выходные1:игналы с С,( снимаются в третью фазу (фиг. 2). Принцип действия поясним для трех возбуждающих и трех тормозящих вхоов (М N 3). Пусть пороги срабатывания всех сумматоров одинаковые и равны , на всё тормозящие входы в первую фазу поданы логичесие О, а на один из возбуждающих ходов подана логическая 1, например а I. Во вторую фазу электронно-дырочная плазма от первого входного транзистора в первом и втором сумматорах достигает п&рзьк .буферных транзисторов, и к началу третьей фазы часть ее .дистигает выходных транзисторов первого и второго сумматоров. Однако вследствие выбранного порога выходные транзисторы не регенерируют этот сигнал, оставаясь в третью фазу в выключенном состоянии с большим сопротивлением. Также в выключенном состоянии остается выходной транзистор третьего сумматора Поэтому токовые сигналы С С и С в третьей фазе при рассмотренной комбинации сигналов отсутствуют, соответствуя логическим О (С С Cj 0), а напряженные на выходах 1, 2, наоборот соответствуют логическим I то есть С. 2 & .1 (первая комбинация на фиг. 1, где символы . и 4 соответствуют напряжению импульсного питания на шинах 25 и 33 соответственно)

Если возбуждающие сигналы поданы на два входа 4, а тормозящие сигналы по прежнему отсутствуют (Ь . 0), то к началу третьей фазы выходных транзисторов в первом и втором сумматорах достигает такое количество электронно-дырочной плазмы, которое при выбранных порогах А С 2 оказывается достаточным для регенерации плазмы выходными транзисторами в третьей фазе и их включения. При этом становится С, С; 1 и соответственно С б. О Поскольку на тормозящие входы ячейки логические 1 не подавались, то электронно-дырочная плазма в слое полупроводника 6, общего для всех транзисторов третьего сумматора, отсутствует, и С О, а (5 1 (2-ая комбинация сигналов ни фиг. 2). I

Пусть по-прежнему на два возбуждающих входа поданы логические 1 а а 1, а 0. Пусть теперь на один из тормозящих входов подается логическая 1, например, Ь 1, bj bj 0. Теперь по прежнему Са 1, но С, О, так как теперь вследствие запрета на включение первого буферного транзистора в первом сумматоре к его выходному транзистору к началу третьей фазы будет поступать плазма лишь от второго буферного транзистора, которой будет недостаточно для регенераций сигнала выходным транзистором в третьей фазе, и он останется в выключенном состоянии. В таком же состоянии останется и выходной транзистор третьего сумматора, поскольку в него поступает плазма лишь от первого буферного транзистора, которой при выбранном пороге .срабатывания В 2 недостаточно для регенерации в третьей фазе. Поэтому/по-прежнему С О и Сз 1, и Cj Г, 6j О (3-я комбинация сигналов на фиг. 2).

Если сохранится Ь 1, но теперь на все возбз ждающие входы будут поданы логические 1, то, очевидно, электронно-дырочной плазмы будет достаточно для включения выходных транзисторов как во втором, так и Первом сумматорах. Поэтому станет С, Cg 1 и по-прежнему останется

0; на инвертирующих выходах С,

рующю ячейки станет С C,j О и С 1 1

(4-я комбинация сигналов на фиг. 2). Если же сохранятся сигналы а 2 aj I, но тормозящие сигналы будут поступать в третью фазу на два входа 5, например (для определенности) Ь. О и Ь- bj 1 , то в третью фазу логические 1 появляется на плазменных выходах второго и третьего сумматора. На первом выходе будет С. О,так как в выходной транзистор плазма поступает лишь от первого (а J) буферного транзистора, но при выбранном пороге А 2 ее недостаточно для регенерации сигнала. Соответственно, на втором, третьем и первом выходах ячейки 2, 3 и I будут сигналы С Сд О и С I (5-я комбинация сигналов на Фиг. 2).

Расширение функциональных возмож.ностей интегрального нейрона связано с тем, что помимо пороговой суммы возбуждающих и тормозящих сигналов, формируются их пороговые суммы в отдельности, что достигается практически без увеличения транзисторов за счет физической (функциональной) интеграции активных элементов. Все входные и выходные сигналы являются Однополярными, что упрощает согласование интегрального нейрона с известными схемами, например, с приборами с плазменной связью на основе модуляционных транзисторов или тиристоров. Использование в качестве активных элементов (буферных и выходных транзисторов) приборов с S-образной ВАК приводит к регенерации сигнала за счет очень большого внутреннего усиления тока (до 10 раз), что резко увеличивает нагрузочную способность и расширяет функдаональные возможности

Закон суммирования может изменяться при соединении вывода от какого-либо эмиттера буферного транзистора третьего сз матора не с одним, а с несколькими эмиттерами буферных транзисторов первого сумматора. Для изменения веса входных сигналов (для обеспечения приоритета) входы 4 или 5 могут одновременно соединяться с эмиттерами нескольких входных транзисторов, (при этом в общем случае может быть MjtN). Последние могут использоваться как с оборванной базой (как показано на фиг. 1), так и с зашунтированным эмиттерным переходом. Модуляционные транзисторы,без шунта в эмиттерном переходе имеют, как правило, однозначную по напряжению БАХ, тиристоры - наоборот, неоднозначную по напряжению ВАХ. Введение шунтов в эмиттерНые переходы составляющих тиристоры п-р-п-транзисторов пркводит к некоторому увеличению тока включения тиристоров, не нарушая (а улучшая) функционирование предлагаемой ячейки. Резисторы 13 могут у различных выходных транзисторов иметь как одинаковое, так и различное сопротивление (для обеспечения различной величины выходного тока). Сопротивления шунтирукнцих резисторов 29 у буферных транзисторов второго сумматора выбираются, как правило, такими же как и сопротивление резисторов 26 у буферных транзисторов первого суммато ра. Однако следует отметить, что нагрузочные резисторы (во всех ее узлах, кроме транзисторов, охваченных запрещающей связью) могут отсутствовать.

Аналогичным образом (с точки зрения схемотехники) интегральный нейрон может быть выполнен на основе других приборов с отрицательным дифференциальным сопротивлением, например, однопереходных транзисторов, а S - диодов на компенсированных полупроводниках и др. Во всех случаях расстояние между охваченными плазменной связью транзисторами не превышает несколько диффузионных длин неосновных носителей заряда в слое полупроводника 6.

Пример конкретного выполнения: удельное сопротивление р-слоя 6 составляет 1 кОм.см; р-базы 7, 8, 9, 14, 16, 18, 19, 20 и р-области 31 выполнены на глубину 1,1 - 1,6 мкм с поверхностной концентрацией акцепторной прИмеси 5-10 расстоянием между ними 5...20 мкм; п-области 10, 11, 12, 15, 17, 21, 22, 23 выполнены на глубину 0,6... ... О,9 мкм с поверхностной концентр

рацией донорной примеси до 10

Расширение функциональных возможностей интегрального нейрона позволяет применять его для создания БИС сложных вычислительных устройств при разработке нового поколения радиоэлектронной аппаратуры, в первую очередь Э.ВМ. 41) Mm/tV

« Й«./ .. «

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторно-транзисторный инвертор | 1989 |

|

SU1651372A1 |

| Устройство для моделирования нейрона | 1977 |

|

SU623215A1 |

| Модель нейрона | 1975 |

|

SU623214A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1972 |

|

SU354576A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

ИНТЕГРАЛЬНЫЙ НЕЙРОН, включающий шину питания, возбуждающие и тормозящие входы, сумматор, выполненный на основе переключающих транзисторов, и выход, отличающий с я тем, что, с целью расширения функциональных возможностей, в нейрон дополнительно введены шина питания и два сумматора, при этом все три сумматора имеют выходы, свои входные, выходные и расположенные между ними буферные транзисторы, выполненные в виде биполярных транзисторов с плазменной связью в общем высокоомном полупроводнике, причем первый и второй сумматоры имеют общие возбуждающие транзисторы, эмиттеры которых подсоединены к возбуждающим входам, эмиттеры выходных транзисторов всех трех сумматоров соединены с соответствующими выходами, через нагрузочные резисторы подключены к .первой шине питания и через шунтирующие резисторы соединены с базами этих же транзисторов, эмиттеры буферных транзисторов первого и второго сумматоров через первые шунтирующие резисторы соединены с базами этих же транзисторов и через нагрузочньш резисторы подключены ко второй шине питания, эмиттеры буферсл ных транзисторов третьего сумматора через вторые шунтирующие резисторы соединены с базами этих же транзисторов и подключены к эмиттерам соответствующих буферных транзисторов первого сумматора, причем сопротивление вторых шунтирующих резисторов превышает сопротивление первых шун тирующих резисторов по крайней мере NU на 20-50%, эмиттеры возбуждающих 00 транзисторов третьего сумматора под4;ik соединены к тормозящим входам. ел

| Свечников С.В., Лопов М.А | |||

| Микроэлектронный аналоговьй процессор для матричного считывания изображений | |||

| - Микроэлектроника, 1981, т | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

| Сочивко В.П | |||

| Электрические модели нейронов | |||

| - М. | |||

| Энергия, 1965, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

Авторы

Даты

1989-05-15—Публикация

1981-06-01—Подача