,1

Изобретение относится /к вычислительной технике и автоматике и может быть использоваио для построения особо надежных структурно избыточных логических устройств посредством интегральной технологии.

Известные пороговые элементы, использующие суМ,мирова1Ние магнитных потоков в магиитопроводах различной конфигурации, отличаются нетехнологичностью и в них затруднительно применение интегральной технологии.

Известные резистивио-транзисторные пороговые элементы с резистивиыми схемами суммирования избыточных версий аргументов и активными пороговыми схемами (а.мплитудными дискри,ми натора:ми) обладают недО|Стато,чно высокими корректирующими способностями из-за наличия только возбуждающих входов и при большом числе входов недостаточно технологичны.

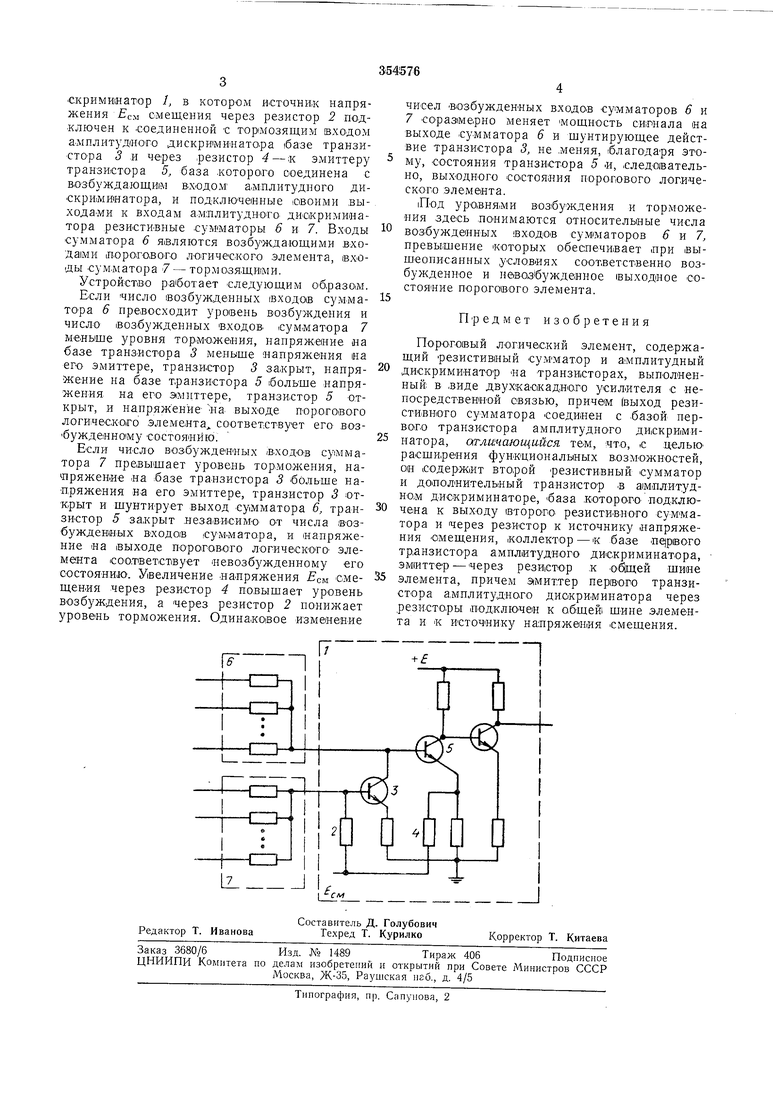

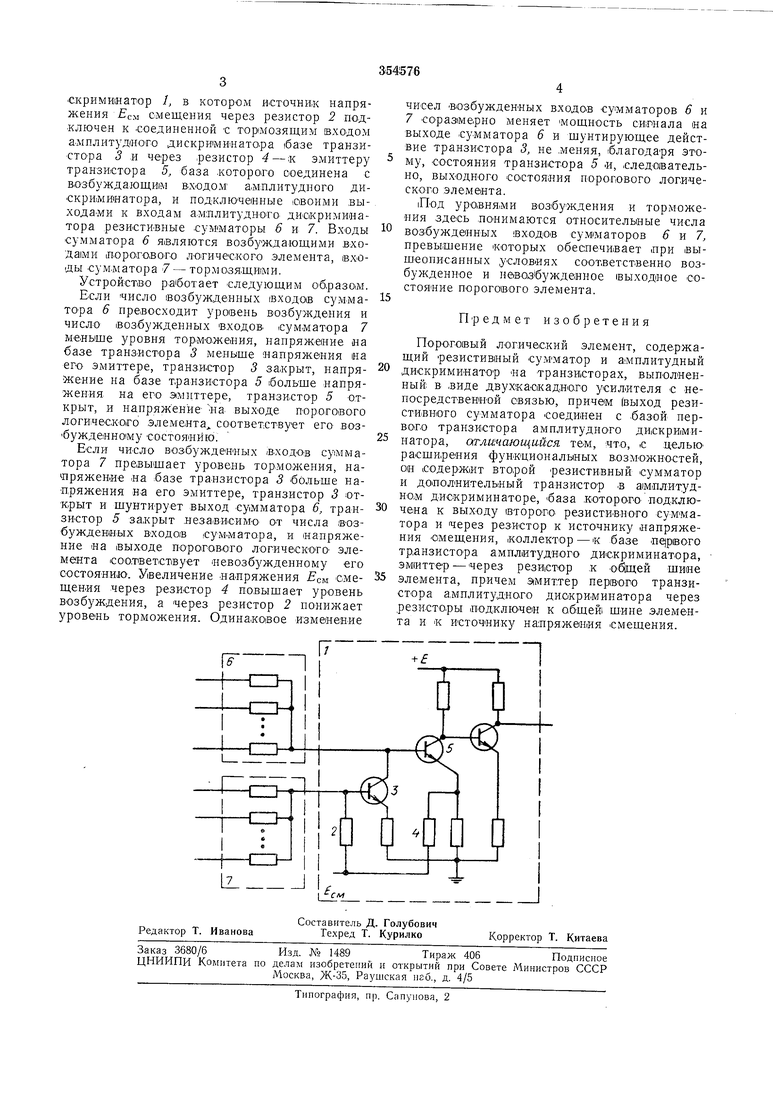

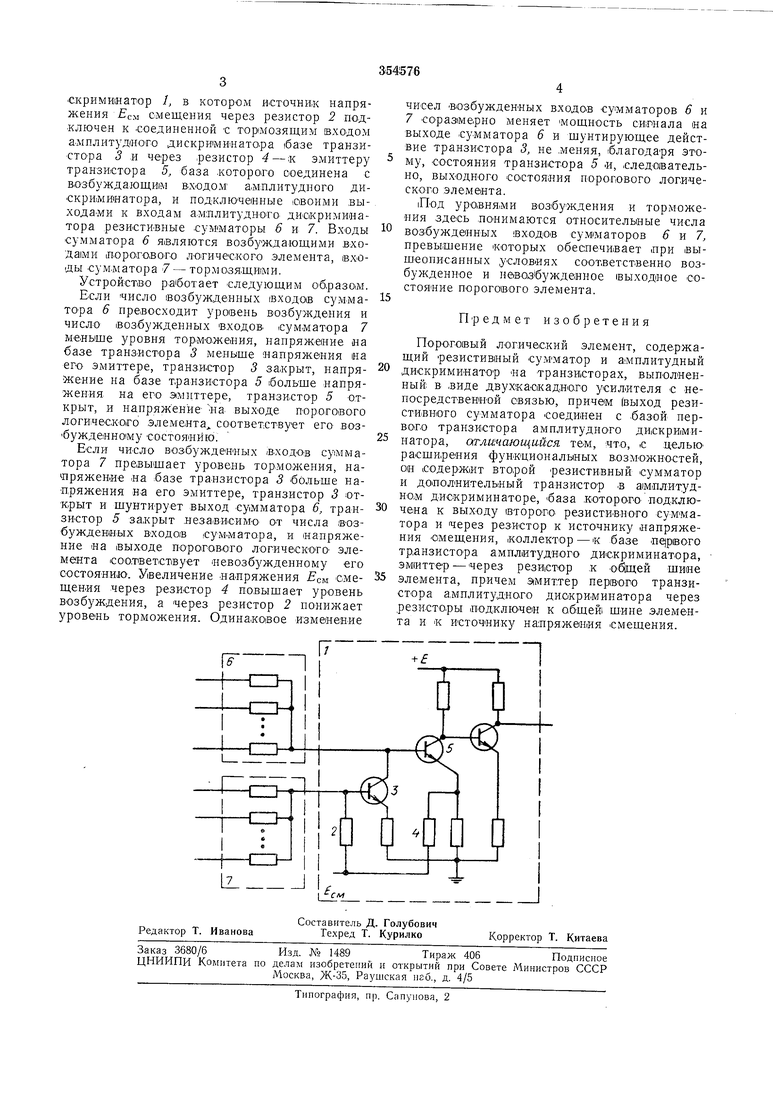

Для расширения функциональных возможностей предлагаемый пороговый логический элемент содержит второй резистивный сум(Матор и дополнительный транзистор в амплитудном дискриминаторе, база которого подключена к выходу второго резнстивного сумматора и через резистор к источнику напряжения смещения, коллектор - к базе первого транзистора амплитудного дискриминатора, эмиттер - че.рез резистор к

Общей шине элемента, причем эмиттер первого транзистора амплитудного дискриминатора через резисторы подключен к общей шине элемента и к источнику напряжения смещения.

Это позволяет дополнительно корректировать часть ошибок, обусловленных ненра1вильны1ми соединениями входов порогового элемента с выходами, поставляющих избыточные версии аргументов других пороговых элементов структурно избыточных логических устройств, получать высокие корректирующие способности многовходового порогового элемента при фактическом использовании, благодаря выполнению резистивных схем сумми.рования заодно с включающими в себя резисторы этих схем межэлементными связями более технологичной маловходо1ВОЙ (например, двухвходовой) схемы запрета, а также согласовать величину порога резИстивно-транзисторного порогового элемента с общей взвешенной суммой избыточных версий сигналов на возбуждающих и тормозящих входах этого элемента при

представлении возбуждающих и тормозящих сигналов одинаковыми уровнями напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный нейрон | 1981 |

|

SU1074345A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1973 |

|

SU370728A1 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

| Генератор импульсов | 1978 |

|

SU790109A1 |

| ПРИЕМНОЕ ИНТЕГРАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU367553A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1972 |

|

SU341163A1 |

| Многоканальный коммутатор | 1980 |

|

SU907799A1 |

| Универсальный многозначный логический элемент | 1978 |

|

SU746904A1 |

Даты

1972-01-01—Публикация