2. Сумматор-вычитаТель по п.1, otnH4arotHHftcH тем, что, блок формирования позиционного признака содержит группу элементов И, элемент ИЛИ и шифратор, причег-i управляющие BxojM блоки соединены соответственно с первым входом элемента ИЛИ и первыми входами элементов И группы, вторые входы которых соединены соответственно с информационными входами с (m-t-l)-ro блока и выходами шифратора, входы которого соединены соответственно с информационнь /т входами с первого по ю-й .блоки, выходы элементов И группы соединены соответственно с входами элемента ИЛИ,начиная со второго,выход элемента ИЛИ является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| @ -Ичный сумматор | 1983 |

|

SU1166097A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для выравнивания порядков чисел,представленных в системе остаточных классов | 1973 |

|

SU781812A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ | 1997 |

|

RU2131618C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для определения ранга числа | 1982 |

|

SU1108435A1 |

| Устройство для сложения по модулю | 1982 |

|

SU1064278A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

1. СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ, содержащий сумматор, блок инвертирования кода, причем информационные входы блока инверти рования кода соединены с шиной первого операнда сумматора-внчитателя по модулю, первый управляющий вход блока инвертирования кода сое динен с управляющим входом Сложения сумматора-вычитателя по модул первая и вторая группы Входов сумматора соединены соответственно с выходами блока инвертирования кода и шиной второго операнда сумматора вычитателя по модулю, отлича щийся тем, что, с лелью сокра щения аппаратурных затрат, он соде жит дешифратор, счетчик, блок форм рования позиционного признака, эле- мент ИЛИ и элемент И, причем шина первого операнда сумматора-Bi ,1итателя по модулю соединена с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого- соединен с управляющим входом Вычитание сумматора-вычитателя по модулю, выход элемента И соединен с вторым управляющим входом -блока инвертирования и первым входом дешифратора, входы с второго по (т+1)-й которого соединены с шиной кода основания сумматора-вычитателя по модулю, выходы дешифрато- ра соединены с соответствующими управляющими входами блока формирования позиционного признака, информа ционнме входы которого соединены соответственно с выходами разрядных сумм и переносов сумматора, внходщ разрядных сумм которого соединены соответственно с входами счетчика, выходы которого являются выходами результата сумматора-вычитателя по модулю, выход блока формирования позиционного признака соединен со счетным входом счетчика и является выходом позиционного призна ка сумматора-вычитателя по модулю.

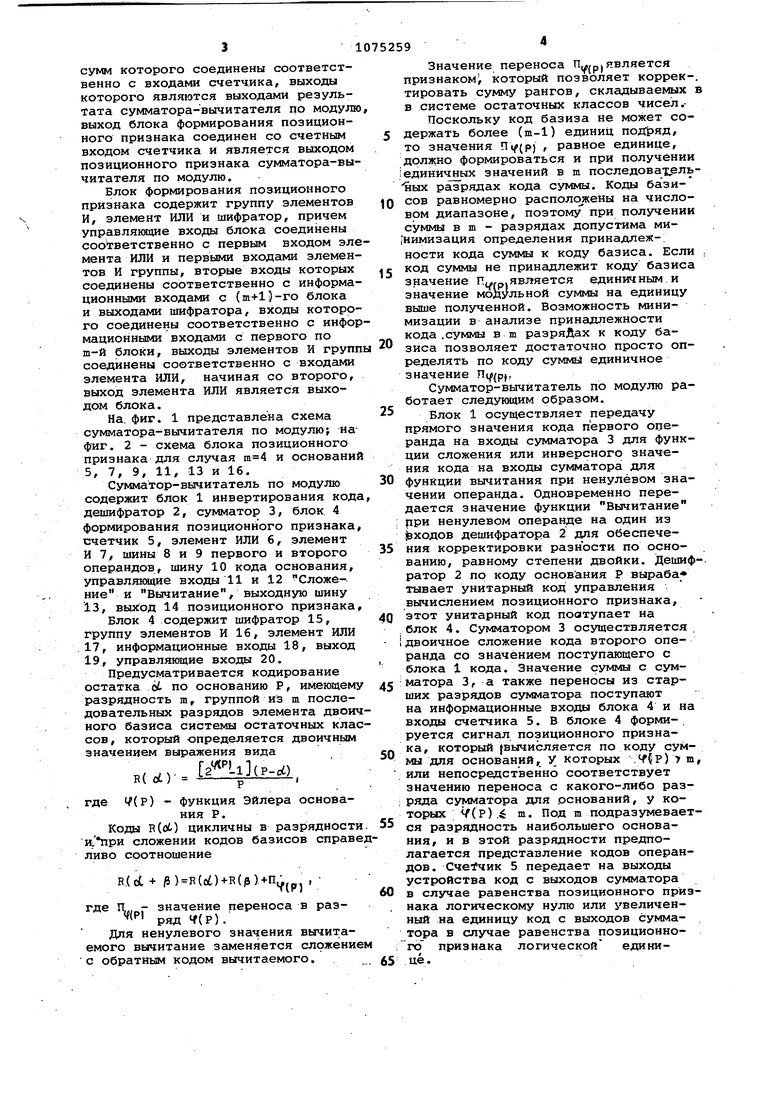

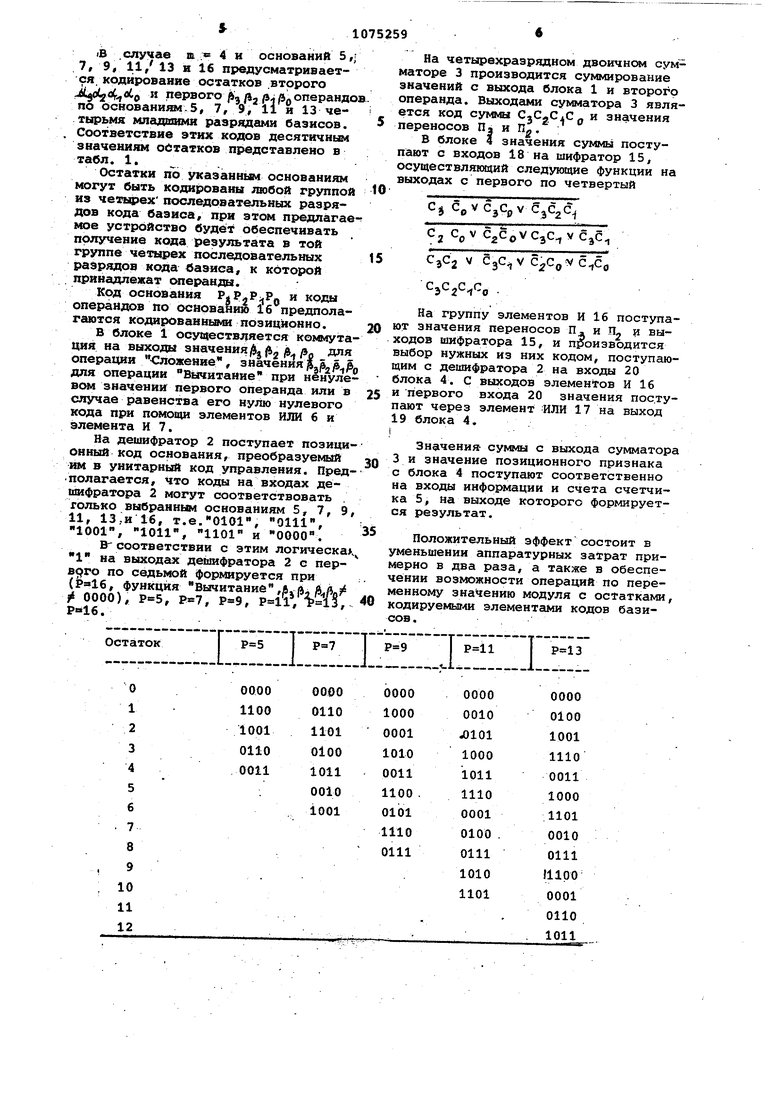

Изобретение относится к вычислительной технике и может быть исполь зовано в вьйчислительных машинах, работан)щих с числами в системе остаточных классов. Известны сумматоры по модулю, содержащие непоэиционный сумматорtl Недостатком данных сумматоров яв ляется необходимость в дополнительном позиционном сумматоре для получения дополнения второгооперанда, что повышает аппаратурные затраты. . Наиболее близким техническим решением к изобретению является ,сумма тор-вычитатель , по модулю, содержащий позиционный и непозиционный сумматоры, две группы элементов И, группу элементов ИЛИ, блок инвертирования кода, блок переполнения позиционного сумматора, причем входы блока инвертирования кода соединены с шиной первого числа, управляющий вход блока инвертирования кода - с шиной управления, выходы блока ин: вертирован.ия кода соединены с первой группой входов позиционного сумматора, йтора:я группа входов которого соединена с шиной второго числа, третья группа входов позиционного сумматора соединена с ши.ной кода дополнения,выходы позициокного сумматора соединены с входами блока переполнения позиционного су лматбра.и первыми входами элементов И первой группы, вторые входы к торых подключены к первому выходу блока переполнения позиционного сумматора, выходы элементов И первой группы подключены к первым вхо дам элементов ИЛИ группы, вторые входы которых соединены с выходами элементов И второй группы, выходы элементов ИЛИ группы являются выходами сумматора по модулю, первые вх ды, элементов И второй группы подклю чены к выходам непозиционного сумма тора, вторые входы элементов И второй группы подключены к второму вы}1оду блока переполнения позицион.ного сумматора, первая группа входо непо5ициоиног6 сумматора подключена к выходам блока инвертирования кода, вторая группа входов непозиционного сумматора подключена к шине второго числа 2. .Недостатком известного сумматора по модулю является наличие позиционного сумматора, осуществляющего сложение трех чисел, что повышает аппаратурные затраты. Целью изобретения является сокращение annapaiTypHbjx затрат. Поставленная цель достигается тем, что сумматор-вычитатель по модулю, содержащий сумматор, ,блок инвертирования кода, причем инфор- мационные входы блока инвертирования кода соединены с шиной первого операнда сумматора-вычитателя по модулю, первый управляющий вход блока инвертирования кода соединен с управляющим входом Сложения сумматора-вычитателя по модулю, первая и вторая группы входов сумматора соединены соответственно с выходами блока инвертирования кода и шиной второго операнда сумматоравычитателя по модулю, содержит дешифратор, счетчик, блок формирования позиционного признака, элемент ИЛИ и элемент И, причем шина первого операнда сумматора-вычитателя по модулю соединена с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с управляквдим входом Вы- читание сумматора-вычитателя по модулю, выход элемента И соединен с вторьм управляницим входом блока инвертирования и первым входом дешифратора, входы с второго по (т+1)-й которого соединенны с шиной кода основания сумматора-вычитателя по модулю, выходы дешифратора соединены с соответствующими управляющими входами блока формирования позиционного признака, информационные входы которого соединены соответственно р выходами разрядных сумм и переносов сумматора, выходы разрядных сумм которого соединены соответственно с входами счетчика, выходы которого являются выходами результата сумматора-вычитателя по модул выход блока формирования позиционного признака соединен со счетным входом счетчика и является выходом позиционного признака сумматора-вы читателя по модулю. Блок формирования позиционного признака содержит группу элементов И, элемент ИЛИ и шифратор, причем управлякицие входы блока соединены соответственно с первым входом эл мента ИЛИ и первыми входами элемен тов И группы, вторые входы которых соединены соответственно с информа ционными входами с (т+15-го блока и выходами шифратора, входы которо го соединены соответственно с инфо мационными входами с первого по т-й блоки, выходы элементов И груп соединены соответственно с входами элемента ИЛИ, начиная со второго, выход элемента ИЛИ является выходом блока. На. фиг. 1 представлена схема сумматора-вычитателя по модулю; -на фиг. 2 - схема блока позиционного признака для случая и основани 5, 7, 9, 11, 13 и 16. Сумматор-вычитатель по модулю содержит блок 1 инвертирования код дешифратор 2, сумматор 3, блок 4 форгдирования позиционного признака счетчик 5, элемент ИЛИ 6, элемент И 7, шины 8 и 9 первого и второго операндов, шину 10 кода основания, управлякицие входы 11 и 12 Сложение и Вычитание, выходную шину 13, выход 14 позиционного признака Блок 4 содержит шифратор 15, группу элементов И 16, элемент ИЛИ 17, информационные входы 18, выход 19, управляющие входы 20. Предусматривается кодирование остатка oi- по основанию Р, имеющему разрядность га, группой из m последовательных разрядов элемента двоич ного базиса системы остаточных клас сов , который определяется двоичным значением выражения вида ,. s -ilcP-) R( ot)- , где /(Р) - функция Эйлера основания Р. Коды кСоб) цикличны в разрядности и. сложении кодов базисов справе ливо соотношение P.(ct + P)H{ot)-bR(p) , где It - значение переноса в ряд Ч(Р). Для ненулевого значения вычитаемого вычитание зеиленяется сложение с обратным кодом вычитаемого. Значение переноса П,-,является признаком который позволяет коррек-. тировать сумму рангов, складываемых в в системе остаточных классов чисел.Поскольку код базиза не может содержать более (т-1) единиц подГряд, то значения nVf(p) , равное единице, должно формироваться и при получении iединичных значений в m последова ель ых разрядах кода суммы. Коды базисов равномерно расположены на числовом диапазоне, поэтому при получении суммы Вт- разрядах допустима миГНимизация определения принадлеж-: ности кода суммы к коду базиса. Если , код суммы не принадлежит коду базиса значение .является единичным и значение модульной суммы на единицу выше полученной. Возможность минимизации в анализе принадлежности кода .суммы в m разряДах к коду базиса позволяет достаточно просто определять по коду суммы единичное значение , Сумматор-вычитатель по модулю работает следующим образом. Блок 1 осуществляет передачу прямого значения кода первого опе ранда на входы сумматора 3 для функции сложения или инверсного значения кода на входы сумматора для функции вычитания при ненулевом значении операнда. Одновременно передается значение функции Вычитание при ненулевом операнде на один из |входов дешифратора 2 для обеспечения корректировки разности по основанию, равному степени двойки. Дешифратор 2 по коду основания Р выраба тывает унитарный код управления вычислением позиционного признака, этот унитарный код поатупает на блок 4. Сумматором 3 осуществляется двоичное сложение кода второго операнда со значением поступающего с блока 1 кода. Значение суммы с сумматора 3, а также переносы из старших разрядов сумматора поступают на информационные входы блока 4 и на входы счетчика 5. В блоке 4 формируется сигнал позиционного признака, который {вычисляется по коду суммы для оснований, У которых .) m, или непосредственно соответствует значению переноса с какого-либо разряда сумматора для оснований, у которых V(P) . т. Под m подразумевается разрядность наибольшего основания, и в этой разрядности предполагается представление кодов операндов. Счетчик 5 передает на выходы устройства код с выходов сумматора в случае равенства позиционного признака логическому нулю или увеличенный на единицу код с выходов сумматора в случае равенства позиционного признака логической единице.

В .случае m .« 4 и оснований 5,; 7, 9, 11/ 13 и 16 предусматривается кодйрованяе остатков второго jkyalyclf oLf и первого,/ijpj/sj,операндов по основаниям - 5, 7, 9, li и 13 четырьмя младшими разрядами базисов. Соответствие этих кодов десятичным значеииям остатков представлено в тавл. 1,

Остатки по указанным основаниям могут быть кодированы любой группой из четьфех последовательных разрядов кода базиса, при этом предлагавмое устройство будет обеспечивать получение кода результата в той группе 4ei%ipex последовательных кода Ъазиса, к которой принадлежат сшеранды.

Код основания

PjPjP;,, и коды операндов по основа 1НИ1о 16 предполагаются кодированны1 и позиционно.

В блоке 1 осуществляется KOhenyTaция на выходы значения j (ij ° операции -Сложение, значенияJ( для операции Вычитание при ненулевсш значении первого операнда или в случае равенства его нулю нулевого кода при помощи элементов ИЛИ 6 и элемента И 7.

На дешифратор 2 поступает позиционный код основания, преобразуемый им в унитарный код управления. Пред полагается, что коды на входах дешифратора 2 могут соответствовать . голько выбранным основаниям 5, 7, 9, 11, 13.И 16, т.е.0101, 0111, 1001, 1011, 1101 и 0000.

Вт соответствии с этим логическа 1 на выходах дешифратора 2 с перНа четырехразрядном двоичном сумматоре 3 производится суммирование значений с выхода блока 1 и второго операнда. Выходами сумматора 3 является код сум№ CjCgCiCp и значения переносов П, и П. ;

В блоке 4 значения суммы поступают с входов 18 иа шифратор 15, осуществляющий следующие функции иа выходах с первого по четвертый

GJ Ср V CaCnV 6,C,Cj

-З-Р

Cj Cj,v CgCoVCaC y 636

V CjCjC C .

Ha группу элементов И 16 поступают значения переносов П, и П и выходов шифратора 15, и производится выбор нужных из них кодом, поступающим с дешифратора 2 на входы 20 блока 4. С выходов элементов И 16 и первого входа 20 значения пос.тупают через элемент ИЛИ 17 на выход 19 блока 4. i . .

Значения суммы с выхода сумматора 3 и значение позиционного признака с блока 4 поступают соответственно на входы информации и счета счетчика 5, иа выходе которого формируется результат.

Положительный эффект состоит в уменьшении аппаратурных затрат примерно в два раза, а также в обеспечении возможности операций по переостатками.

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Акушский И.Я., Юдицкий Д.H Машинная арифметика в остаточных классах | |||

| М.., Советское радио, 1968, с | |||

| Способ приготовления массы для карандашей | 1921 |

|

SU311A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сумматор по модулю | 1975 |

|

SU570052A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-23—Публикация

1982-12-28—Подача