(54) УСТЮЙСТВО ДЛЯ ВЫРАВНИВАНИЯ ПОРЯДКОВ ЧИСЕЛ, ПРЕДСТАВЛЕННЫХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ

Изобретение относится к вычислительной технике и мбжет быть использовано в арифметических устройствах различного назначения.

Известно устройство для суммирования и вычитания чисел с перемешшгм основанием, содержащее сумматоры, блок управления, логические схемы, триггеры блокировки и коррекции, счетчик констант и регистр переменного модуля 1 .

Недостатком его является большой объем оборудования и малое быстродействие.

Наиболее близкое к предлагаемому изобретению техническое решение - сумматор в системе остаточных классов (СОК), содержапщй два входных регистра и операционнуи схему, выполненную на ферритовых сердечниках, злемент ИЛИ, причем каждая выходная шина одного регистра через элемент ИЛИ и соответствующую обмотку ферритового сердечника операционной схемы соединена с каждой выходной щиной другого регистра 2.

Недостатком известного устройства является невозможность определения знака результата суммирования аппаратными средствами и. малая

скорость опредеяения программными средствами.

- Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее регистры первого и . второго операндов, выходами соедийенш 1е ieo входами соотвётствуюЕчих дешифраторов первого и второго операндов, выходы которых соедянёны со входами сумматора по мбдупю

10 Р(Р - простое число) входы регистров являются входами устройства, допошительио введены блок анализа разности порядков, блок управления сдвигом, шифратор, вьЬсодной регистр, элемент И, элемент ШШ, элемент

15 ЗАПРЕТ, причем первый и второй выходы сзгмматора по модулю Р соединены соответственно с первьпи и вторым входами блока анализа разности порядков, выход которого со.единен с первым входом элемента ЗАПРЕТ,

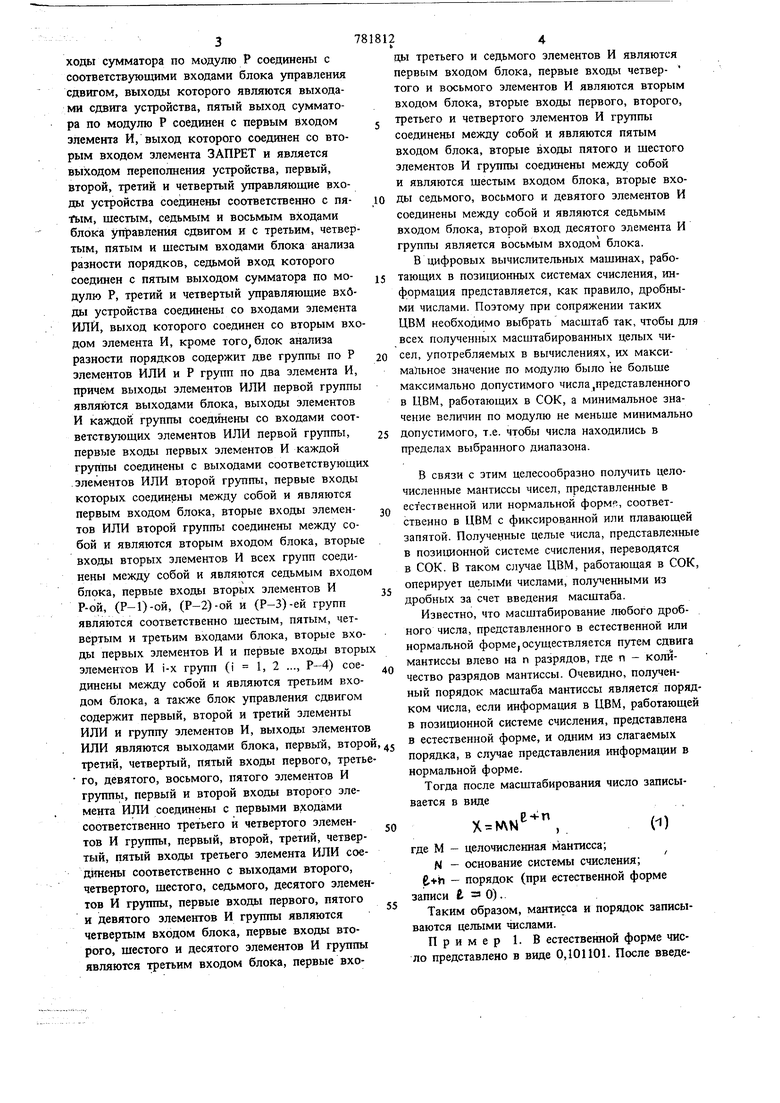

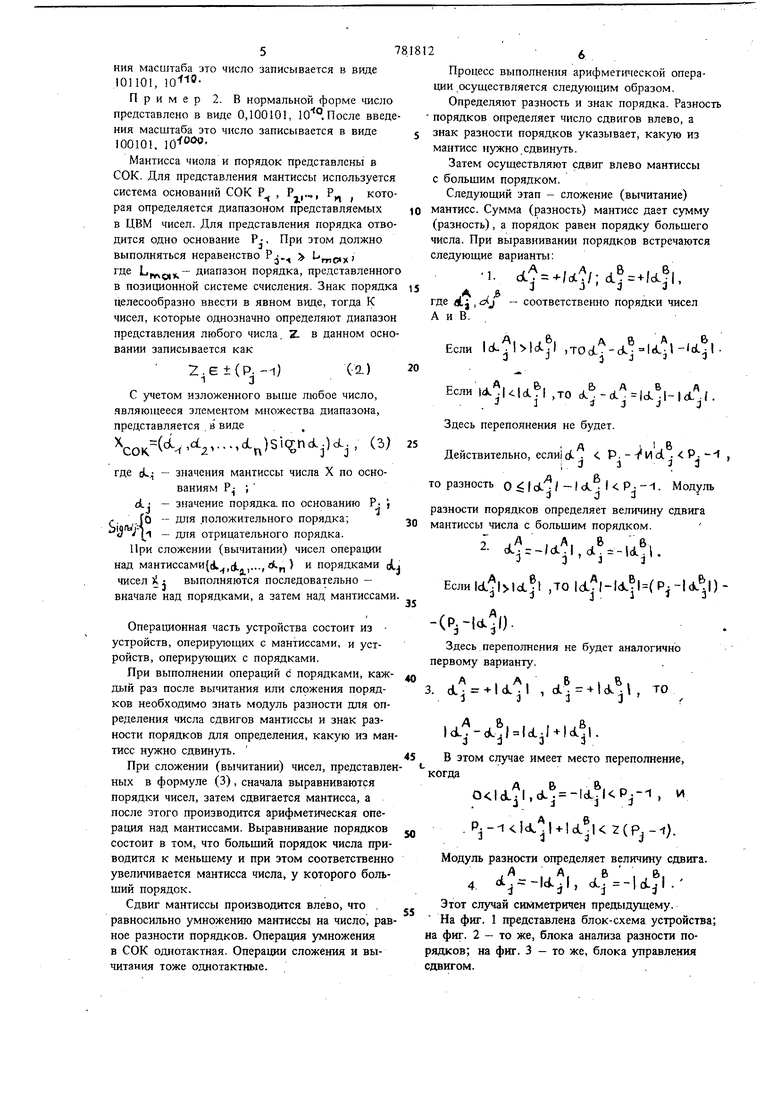

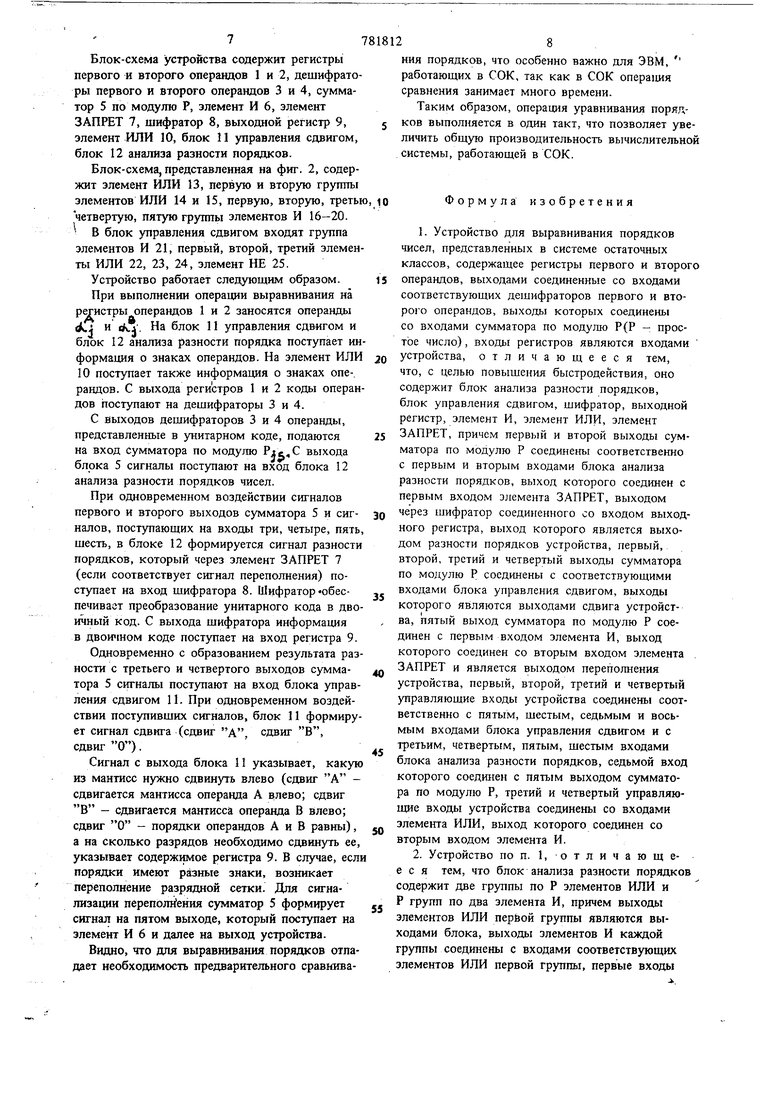

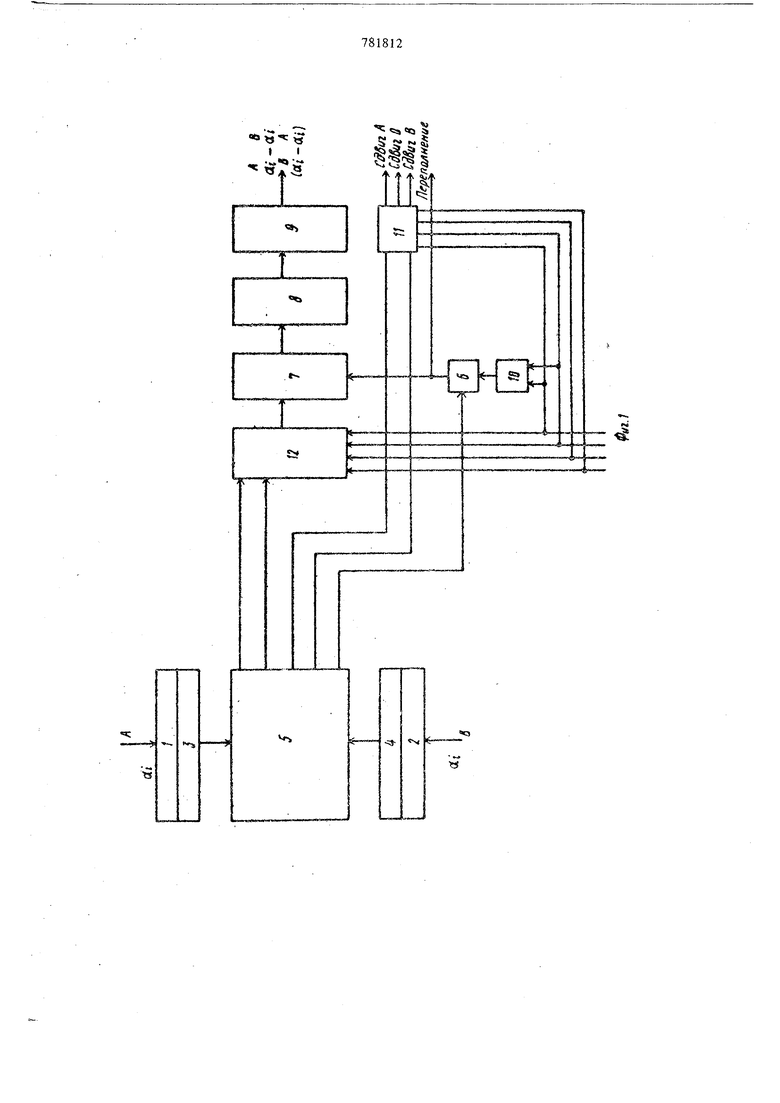

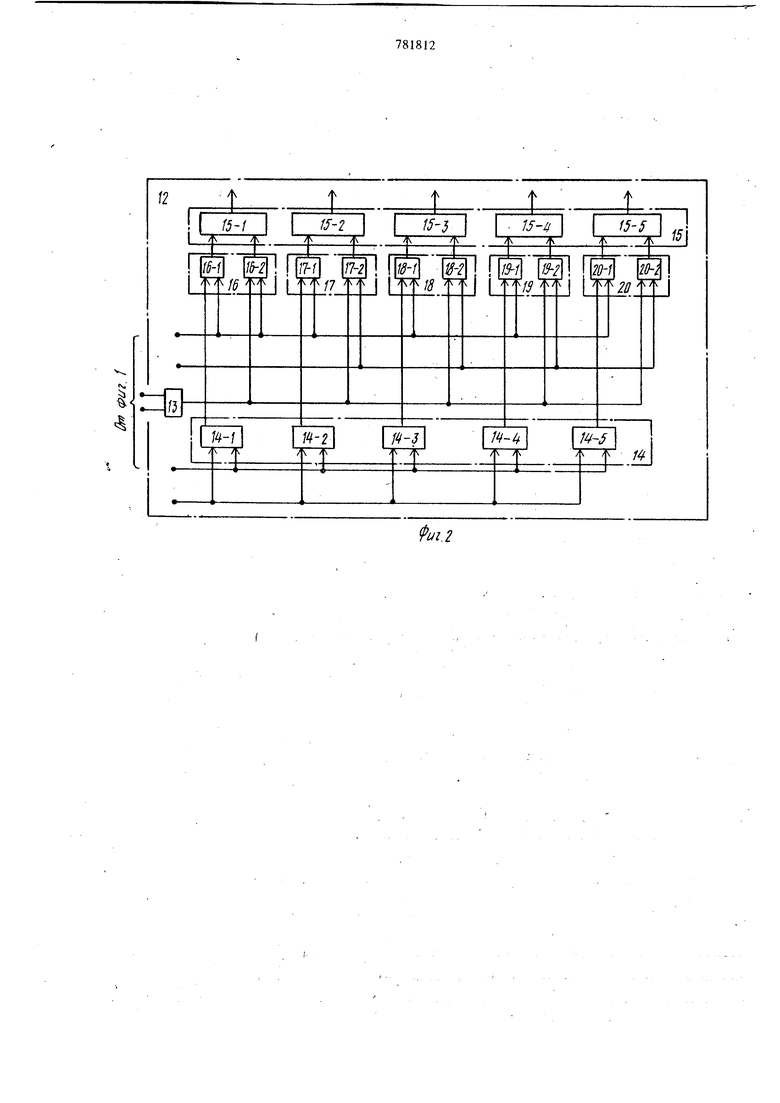

20 выходом через шифратор соединенного со входом выходного регистра, выход которого является выходом разности порядков устройства, первый, второй, третий и четвертый выходы сумматора по модулю Р соединены с соответствующими входами блока управления сдвигом, выходы которого являются выходами сдвига устройства, пятый выход сумматора по модулю Р соединен с первым входом элемента И, выход которого соединен со вторым входом элемента ЗАПРЕТ и является выходом переполнения устройства, первый, второй, третий и четвертый управляющие входы устройства соединены соответственно с пяfbiM, шестым, седьмым и восьмым входами блока 5 авления сдвигом и с третьим, четвертым, пятым и щестым входами блока анализа разности порядков, седьмой вход которого соединен с пятым выходом сумматора по модулю Р, третий и четвертый управляющие вхбды устройства соединены со входами элемента ИЛИ, выход которого соединен со вторым вхо дом элемента И, кроме того, блок анализа разности порядков содержит две группы по Р элементов ИЛИ и Р групп по два элемента И, причем выходы элементов ИЛИ первой группы являются выходами блока, выходы элементов И каждой группы соединены со входами соответствующих элементов ИЛИ первой группы, первые входы первых элементов И каждой группы соединены с выходами соответствующи .элементов ИЛИ второй группы, первые входы которых соединены между собой и являются первым входом блока, вторые входы элементов ИЛИ второй группы соединены между собой и являются вторым входом блока, вторые входы вторых элементов И всех групп соединены между собой и являются седьмым входо блока, первые входы вторых элементов И Р-ой, (Р-1)-ой, (Р-2)-ой и (Р-З)-ей групп являются соответственно щестым, пятым, четвертым и третьим входами блока, вторые входы первых элементов И и первые входы вторы элементов И i-x групп (i 1, 2 ..., Р-4) соединены между собой и являются третьим входом блока, а также блок управления сдвигом содержит первый, второй и третий элементы ИЛИ и группу элементов И, выходы элементов ИЛИ являются выходами блока, первый, второ третии, четвертый, пятый входы первого, треть го, девятого, восьмого, пятого элементов И группь, первый и второй входы второго элемента ИЛИ соединены с первыми входами соответственно третьего и четвертого элементов И грзтшы, первый, второй, третий, четвертый, пятый входы третьего элемента ИЛИ соеД1шены соответственно с выходами второго, четвертого, шестого, седьмого, десятого элемен тов И группы, первые входы первого, пятого и девятого элементов И группы являются четвертым входом блока, первые входы второго, шестого и десятого элементов И группы являются третьим входом блока, первые вхо74 ды третьего и седьмого элементов И являются первым входом блока, первые входы четвертого и восьмого элементов И являются вторым входом блока, вторые входы первого, второго, третьего и четвертого элементов И группы соединены между собой и являются пятым входом блока, вторые входы пятого и щестого элементов И группы соединены между собой и являются шестым входом блока, вторые входы седьмого, восьмого и девятого элементов И соединены между собой и являются седьмым входом блока, второй вход десятого элемента И группы является восьмым входом блока. В Щ1ФРОВЫХ вычислительных мащинах, работающих в позиционных системах счисления, информадия представляется, как правило, дробными числами. Поэтому при сопряжении таких ЦВМ необходимо выбрать масщтаб так, чтобы для всех полученных масщтабированных делых чисел, употребляемых в вычислениях, их максимальное значение по модулю было не больше максимально допустимого числа,представленного в ЦВМ, работающих в СОК, а минимальное значение величин по модулю не меньше минимально допустимого, т.е. чтобы числа находились в пределах выбранного диапазона. В связи с этим целесообразно получить целочисленные мантиссы чисел, представленные в естественной или нормальной форме, соответственно в ЦВМ с фиксиров.анной или плавающей запятой. Полученные целые числа, представленные в позиционной системе счисления, переводятся в СОК. В таком случае ЦВМ, работающая в СОК, оперирует целыми числами, полученными из дробных за счет введения масштаба. Известно, что масштабирование любого дробного числа, представленного в естественной или нормальной форме, осуществляется путем сдвига мантиссы влево на п разрядов, где п - количество разрядов мантиссы. Очевидно, полученный порядок масштаба мантиссы является порядком числа, если информация в ЦВМ, работающей в позиционной системе счисления, представлена в естественной форме, и одним из слагаемых порядка, в случае представления информации в нормальной форме. Тогда после масщтабирования число записывается в виде , где М - целочисленная мантисса; N - основание системы счисления; ,Н - порядок (при естественной форме записи fc 0).. Таким образом, мантисса и порядок записываются целыми числами. Пример 1. В естественной форме число представлено в виде 0,101101. После введения масштаба это число записывается в виде 101101, 10®Пример 2. В нормальной форме число представлено в виде 0,100101, . После введе ния масштаба это число записывается в виде 100101, Мантисса чиола и порядок представлены в СОК. Для представления мантиссы используется система оснований СОК Р , Р,,., Р„ кото рая определяется диапазоном представляемых в ЦВМ чисел. Для представления порядка отво дится одно основание Р , При этом должно выполняться неравенство Р. mc«x диапазон порядка, представленног в позиционной системе счисления. Знак порядка целесообразно ввести в явном виде, тогда К чисел, которые однозначно определяют диапазон представления любого числа. Z. в данном осно вании записывается как Z.etCRji)(-2-) с учетом изложенного выше любое число, являющееся элементом множества диапазона, представляется в виде, COK() где dL; - значения мантиссы числа X по основаниям Р -значение порядка, по основанию - дпя положительного порядка; -для отрицательного порядка. При сложении (вычитании) чисел операции над мантиссами((1.д .,А,) и порядками 1 чисел i выполняются последовательно - вначале над порядками, а затем над мантиссами Операционная часть устройства состоит из устройств, оперирующих с мантиссами, и устройств, оперирующих с порядками. При выполнении операций с порядками, каждый раз после вычитания или слржения порядков необходимо знать модуль разности для определения числа сдвигов мантиссы и знак разности порядков для определения, какую из ман тисс нужно сдвинуть. При сложении (вычитании) чисел, представле ных в формуле (3), сначала выравниваются порядки чисел, затем сдвигается мантисса, а после этого производится арифметическая операция над мантиссами. Выравнивание порядков состоит в том, что больший порядок числа приводится к меньшему и при этом соответственно увеличивается мантисса числа, у которого больший порядок. Сдвиг мантиссы производится влево, что . равносильно умножению мантиссы на число, рав ное разности порядков. Операция умножения в СОК однотактная. Операции сложения и вычитания тоже однотактные. Процесс выполнения арифметической операции осуществляется следующим образом. Определяют разность и знак порядка. Разность порядков определяет число сдвигов влево, а знак разности порядков указывает, какую из мантисс нужно сдвинуть. Затем осуществляют сдвиг влево мантиссы с большим порядком. Следующий этап - сложение (вычитание) мантисс. Сумма (разность) мантисс дает сумму (разность), а порядок равен порядку большего числа. При выравнивании порядков встречаются следующие варианты: d , А , где а, j , j - соответственно порядки чисел ldcjl lijl .TOd djHcL l-dL I. Ecлиtd.-U|dp,тod..|-|dL.J. Здесь переполнения не будет. P -Vnd. А Действительно, если dо разность О (d /-IdL UP--1. Модуль ЭJ3 разности порядков определяет величину сдвига мантиссы числа с большим порядком. ,d; -|ci;i. Если1сС Ыо1 1 ,()-(Prl OЗдесь переполнения не будет аналогично первому варианту. . ™ .ld. 4J/ Id.J-dL HcL.i + ldL. 3JV3 . в этом случае имеет место переполнение, огда (,d., ..(P,,--t). Модуль разности определяет величину сдвига. 4 , d -Ujl. Этот случай симметричен предыдущему. На фиг. 1 представлена блок-схема устройства; а фиг. 2 - то же, блока анализа разности поядков; на фиг. 3 - то же, блока управления двигом. 77 Блок-схема устройства содержит регистры первого и второго операндов 1 и 2, дешифраторы первого и второго операндов 3 и 4, сумматор 5 по модулю Р, элемент И 6, элемент ЗАПРЕТ 7, шифратор 8, выходной регистр 9, элемент ИЛИ 10, блок 11 управления сдвигом, блок 12 анализа разности порядков. Блок-схема, представленная на фиг. 2, содержит элемент ИЛИ 13, первую и вторую группы элементов ИЛИ 14 и 15, первую, вторую, третью четвертую, пятую группы элементов И 16-20. В блок управления сдвигом входят группа элементов И 21, первый, второй, третий элементы ИЛИ 22, 23, 24, элемент НЕ 25. Устройство работает следзтощим образом. При выполнении операции выравнивания на регистры операндов 1 и 2 заносятся операнды (.i и (Л. На блок II управления сдвигом и блок 12 анализа разности порядка поступает ин формация о знаках операндов. На элемент ИЛИ 10 поступает также информация о знаках one-, рандов. С выхода регистров 1 и 2 коды операн дов поступают на дешифраторы 3 и 4. С выходов дешифраторов 3 и 4 операнды, представленные в унитарном коде, подаются на вход сумматора по модулю Pit,С выхода блока 5 сигналы поступают на вход блока 12 анализа разности порядков чисел. При одновременном воздействии сигналов первого и второго выходов сумматора 5 и сигналов, поступаюших на входы три, четыре, пять шесть, в блоке 12 формируется сигнал разности порядков, который через элемент ЗАПРЕТ 7 (если соответствует сигнал переполнения) поступает на вход шифратора 8. Шифратор «обеспечивагт преобразование унитарного кода в дво ичный код. С выхода шифратора информация в двоичном коде поступает на вход регистра 9. Одновременно с образованием результата раз ности с третьего и четвертого выходов сумматора 5 сигналы поступают на вход блока управления сдвигом 11. При одновременном воздействии поступивших сигналов, блок 11 формирует сигнал сдвига (сдвиг А, сдвиг В, сдвиг О). Сигнал с выхода блока 11 указывает, какую из мантисс нужно сдвинуть влево (сдвиг А сдвигается мантисса операнда А влево; сдвиг В - сдвигается мантисса операнда В влево; сдвиг О - порядки операндов А и В равны), а на сколько разрядов необходимо сдвинуть ее, указывает содержимое регистра 9. В случае, есл порядки имеют разные знаки, возникает переполнение разрядной сетки. Для сигнализации переполнения сумматор 5 формирует сигнал на пятом выходе, который поступает на элемент И 6 и далее на выход устройства. Видно, что для выравнивания порядков отпадает необходимость предварительного сравнивания порядков, что особенно важно для ЭВМ, работающих в СОК, так как в СОК опера1шя сравнения занимает много времени. Таким образом, операция уравнивания порядков выполняется в один такт, что позволяет увеличить обшую производительность вычислительной системы, работаюшей в СОК. Формула изобретения 1.Устройство для выравнивания порядков чисел, представленных в системе остаточных классов, содержащее регистры первого и второго операндов, выходами соединенные со входами соответствующих дешифраторов первого и второго операндов, выходы которых соединены со входами сумматора по модулю Р(Р - простое число), входы регистров являются входами устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит блок анализа разности порядков, блок управления сдвигом, шифратор, выходной регистр, элемент И, элемент ИЛИ, элемент ЗАПРЕТ, причем первый и второй выходы сумматора по модулю Р соединены соответственно с первым и вторым входами блока анализа разности порядков, выход которого соединен с первым входом элемента ЗАПРЕТ, выходом через шифратор соеди1генного со входом выходного регистра, выход которого является выходом разности порядков устройства, первый, второй, третий и четвертый выходы сумматора по модулю Р соединены с соответствующими входами блока управления сдвигом, выходы которого являются выходами сдвига устройства, пятый выход сумматора по модулю Р соединен с первым входом элемента И, выход которого соединен со вторым входом элемента ЗАПРЕТ и является выходом переполнения устройства, первый, второй, третий и четвертый управляющие входы устройства соединены соответственно с пятым, шестым, седьмым и восьмым входами блока управления сдвигом и с третьим, четвертым, пятым, шестым входами блока анализа разности порядков, седьмой вход которого соединен с пятым выходом сумматора по модулю Р, третий и четвертый управляющие входы устройства соединены со входами элемента ИЛИ, выход которого соединен со вторым входом элемента И. 2.Устройство по п. 1, о т л и ч а ю щ ее с я тем, что блок анализа разности порядков содержит две группы по Р элементов ИЛИ и Р групп по два элемента И, причем выходы элементов ИЛИ перйой группы являются выходами блока, выходы элементов И каждой группы соединены с входами соответствующих элементов ИЛИ первой группы, первые входы первых элементов И каждой группы соединены с выходами соответствующих элементов ИЛИ второй группы, первые входы которых соединены между собой и являются первым входом блока, вторые входы элементов ИЛИ второй группы соединены между собой и являются вторым входом блока, вторые входы вторых элементов И всех групп соединены между собой и являются седьмым входом блока, первые входы вторых элементов И Р-ой, (Р-1)-ой, (Р-2)-ой и (Р-3)-ей групп являются соответственно шестым, пятым, четвертым и третьим входами блока, вторые входы первых элементов И и первые входы вторых элементов И i-ых групп (, 2, ...Р-4) соединены между собой и являются третьим входом блока. 3. Устройство по п. 1, отличающееся тем, что блок управления сдвигом содержит первый, второй и третий элементы ИЛИ и группу элементов И, выходы элементов ИЛИ являются выходами блока, первый, второй третий, четвертый, пятый входы первого, третьего, девятого, восьмого, пятого элементов И группы, первый и второй входы второго элемента ИЛИ соединены с первыми входами соответственно третьего и четвертого элементов И группы, первый, второй, третий, четвертый, пятый входы третьего элемента ИЛИ соединены соответственно с выходами второго, четвертого, шестого, седьмого, десятого элементов И группы, первые входы первого, пятого и девятого элементов И группы являются четвертым входом блока, первые входы второго, шестого и десятого элементов И являются третьим входом блока, первые вхбды третьего и седьмого элементов И являются первым входом блока, первые входы четвертого и восьмого элементов И. являются вторым входом блока, вторые входы первого, второго, третьего и четвертого элементов И группы соединены между собой и являются пятым входом блока, вторые входы пятого и шестого элементов И группы соединены между собой и являются шестым входом блока, вторые входы седьмого, восьмого и девятого элементов И соединены между собой и являются седьмым входом блока, второй вход десятого элемента И группы является восьмым входом блока. Источники информации, принятые во внимание при экспертиэе 1. Акушский И. Я., Юдицкий Д. И. Машинная арифметика в остаточных классах. М., Сов. радио, 1968, I, 4. 2. Авторское свидетельство СССР № 377771, кл. G 06 F 7/50, 1973.

I I

т

«siecs

,S t-j.g

-SC

m

S

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство в системе остаточных классов | 1979 |

|

SU857992A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

13

«

/гл ГW И| И и И И IИ л,

. 41

f3

/4-/

rLJ

ж7 Ч/ 1

/«-J

/« И 0 И 7/7 /

Авторы

Даты

1980-11-23—Публикация

1973-12-11—Подача