Изобретение относится к вычисли- те,пьной технике и может быть использовано для работы в составе процессора быстродействующих ЭВМ,

Целью изобретения является повышение быстродействия.

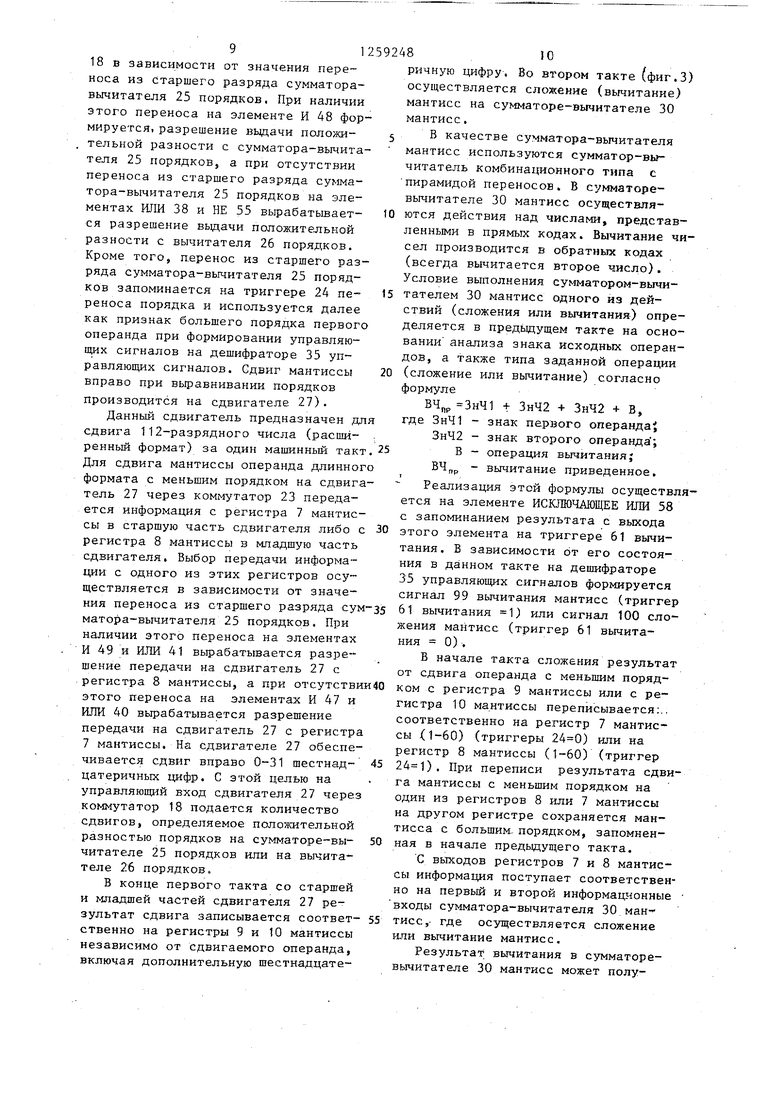

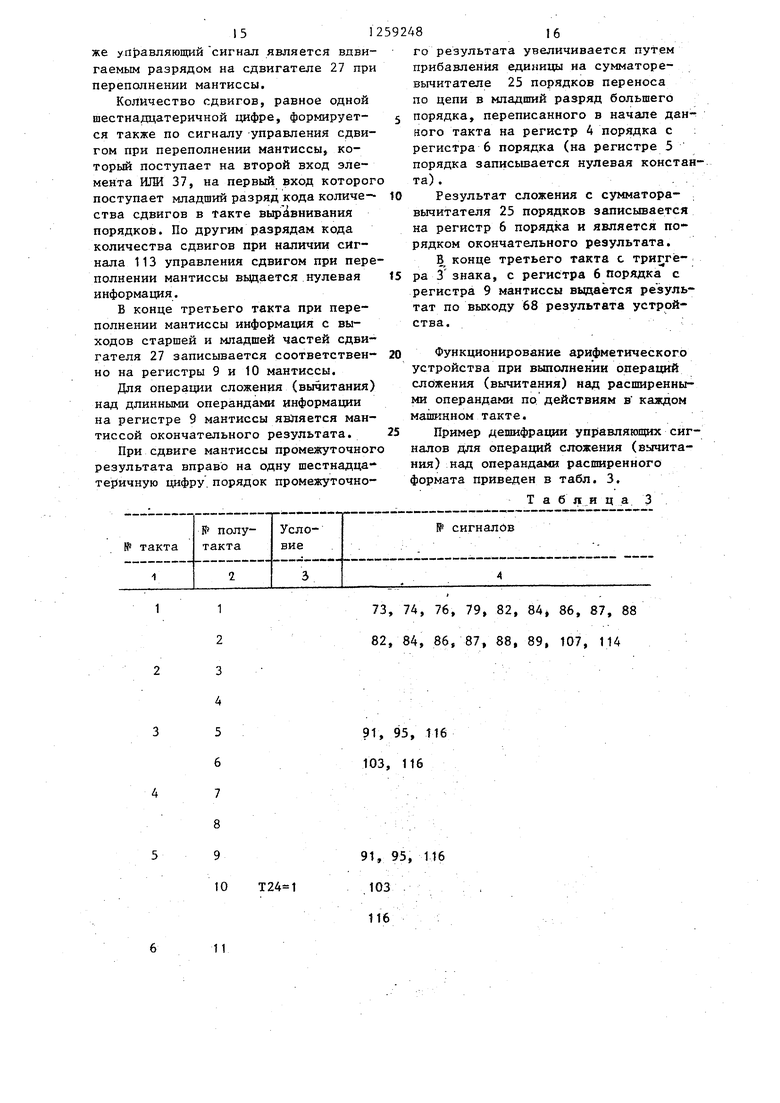

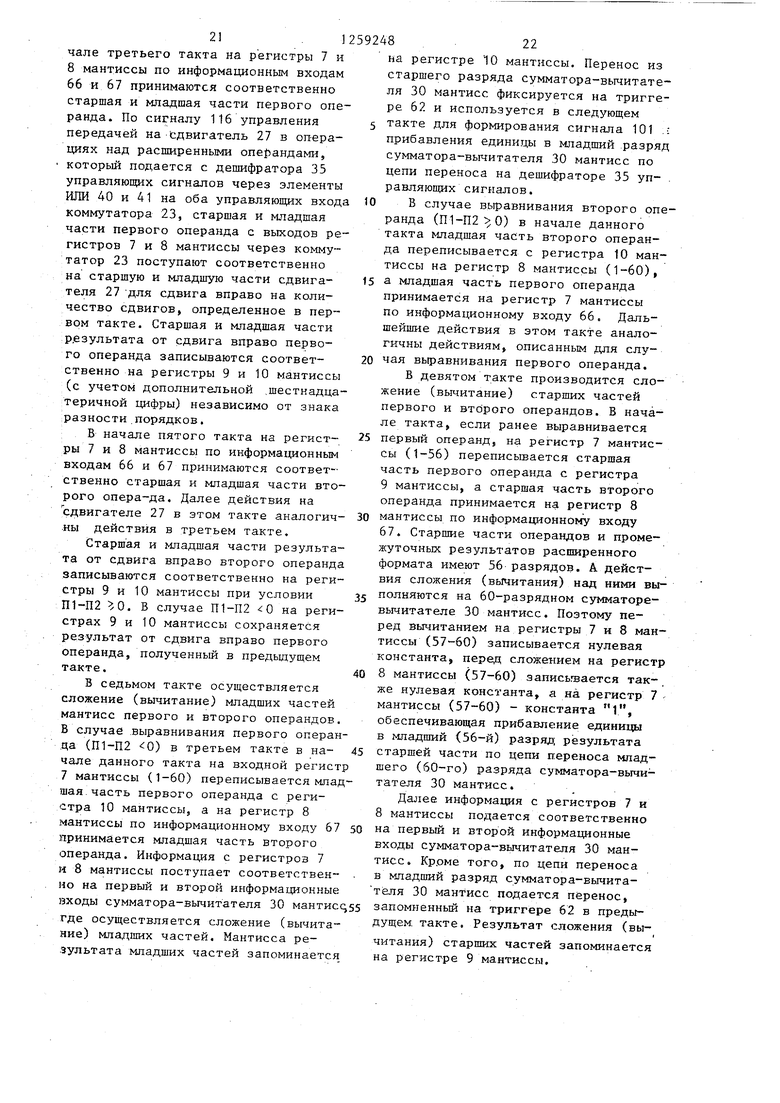

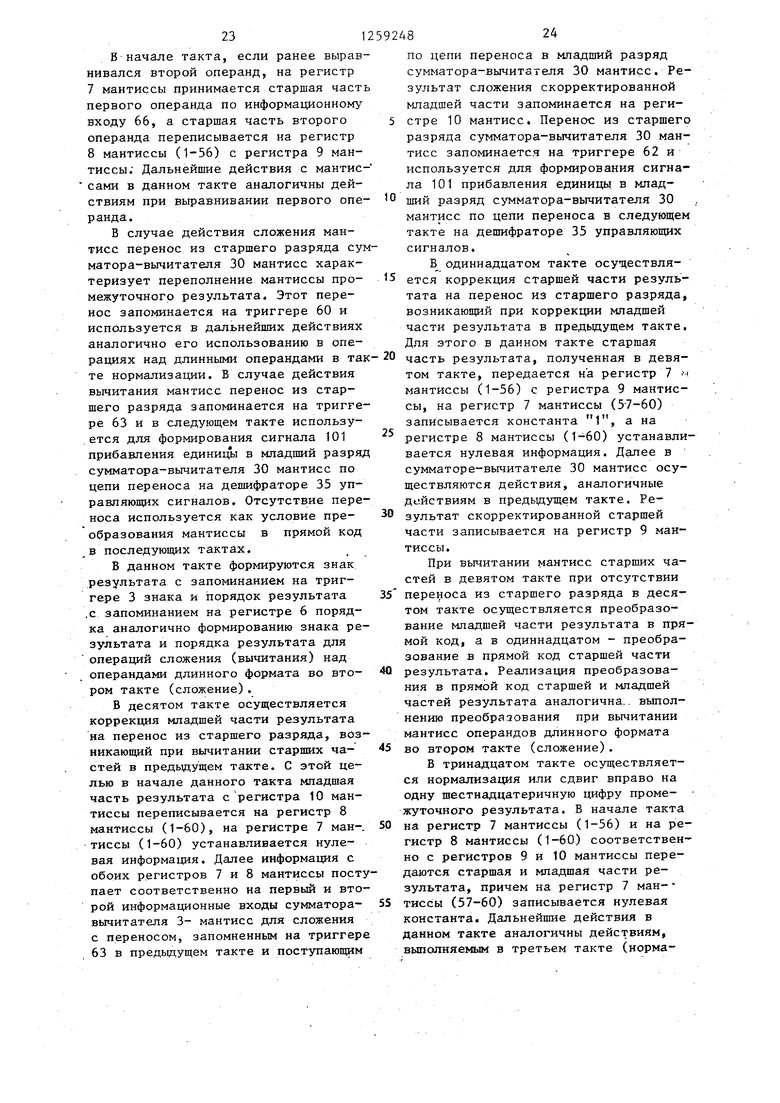

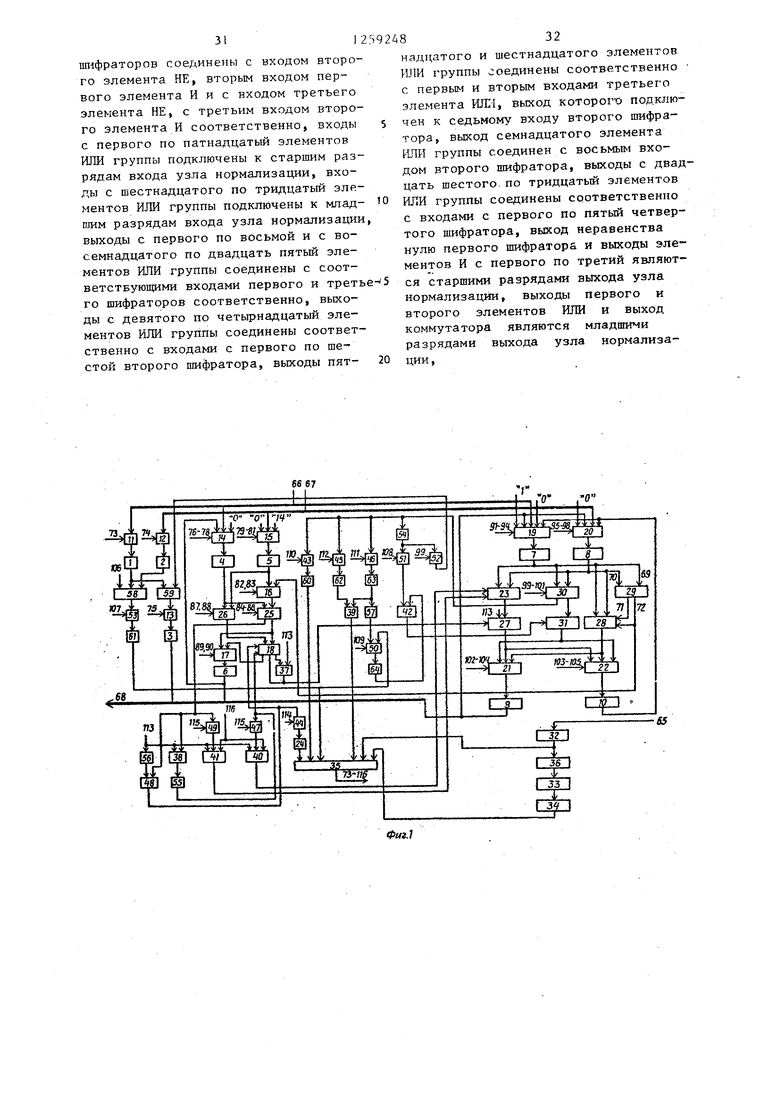

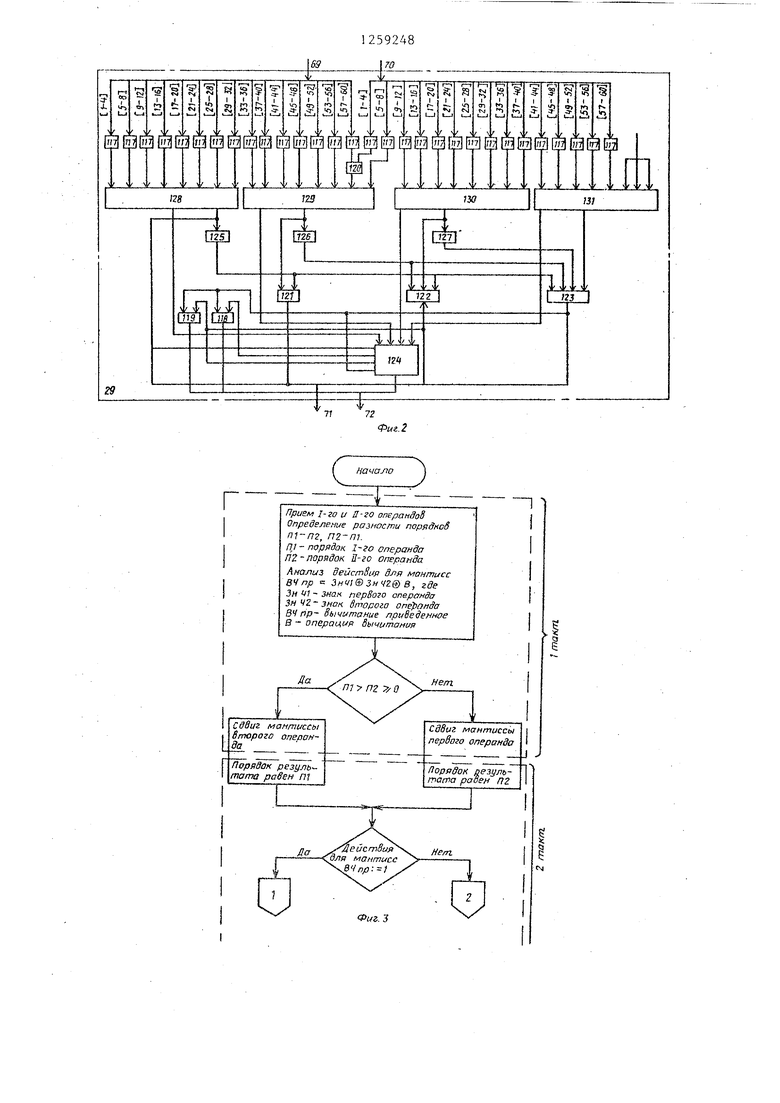

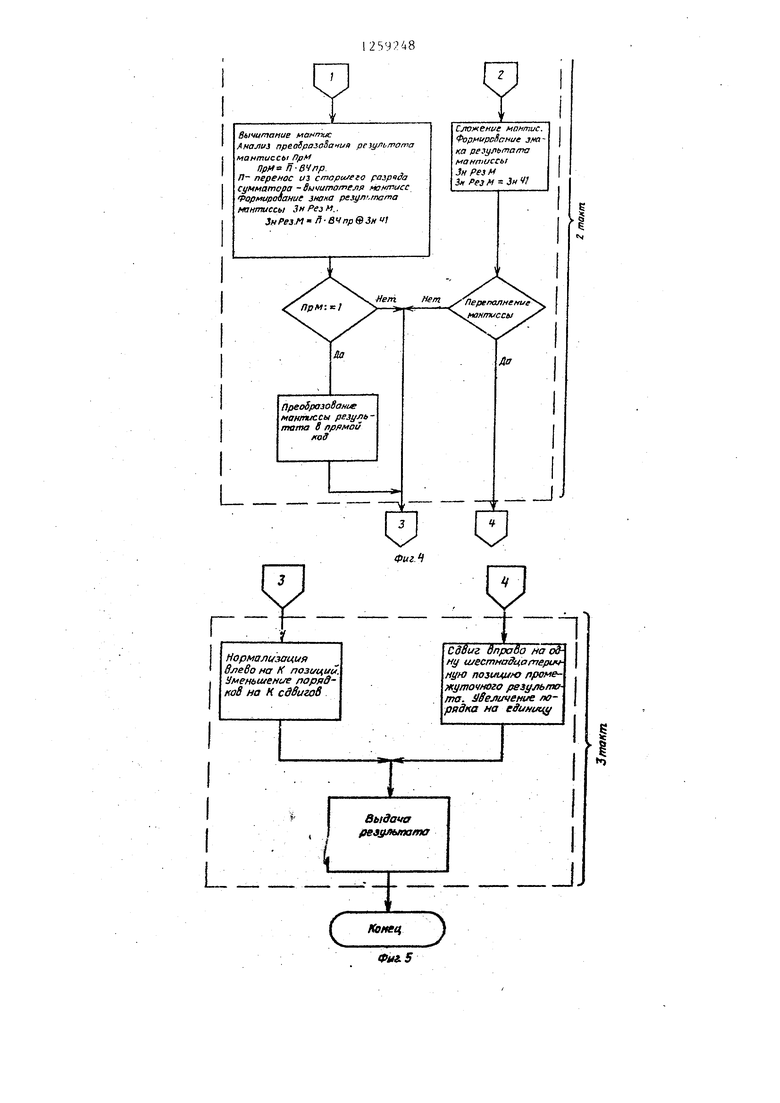

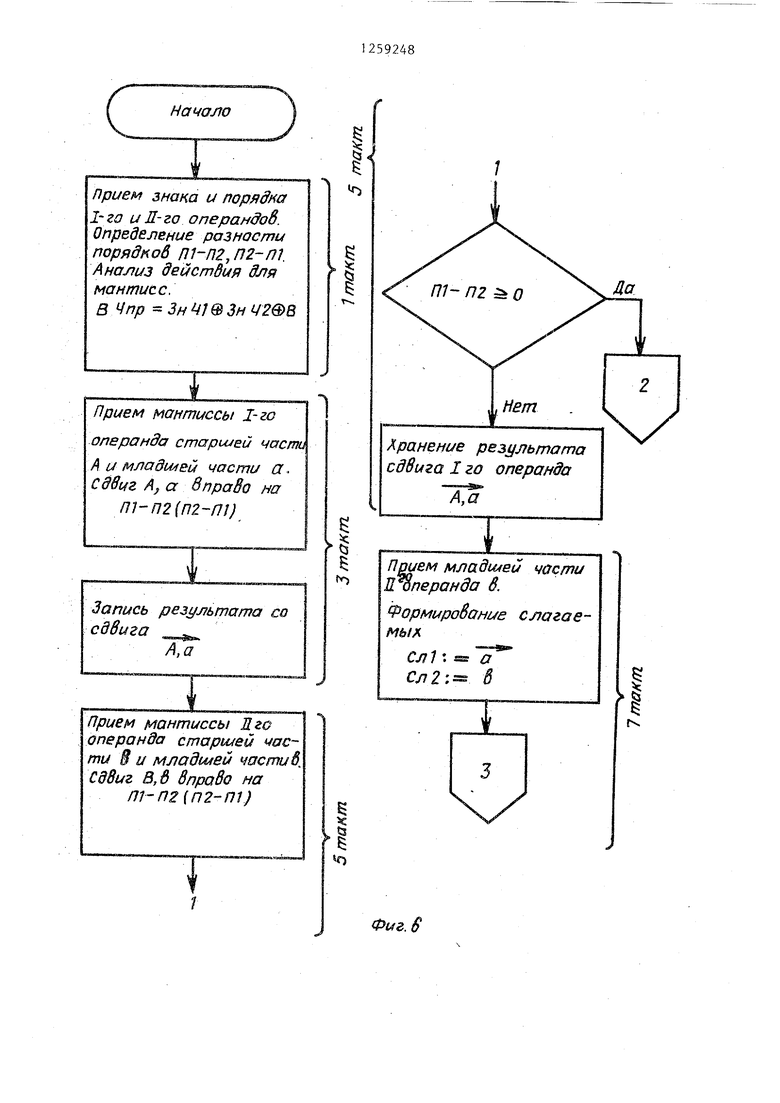

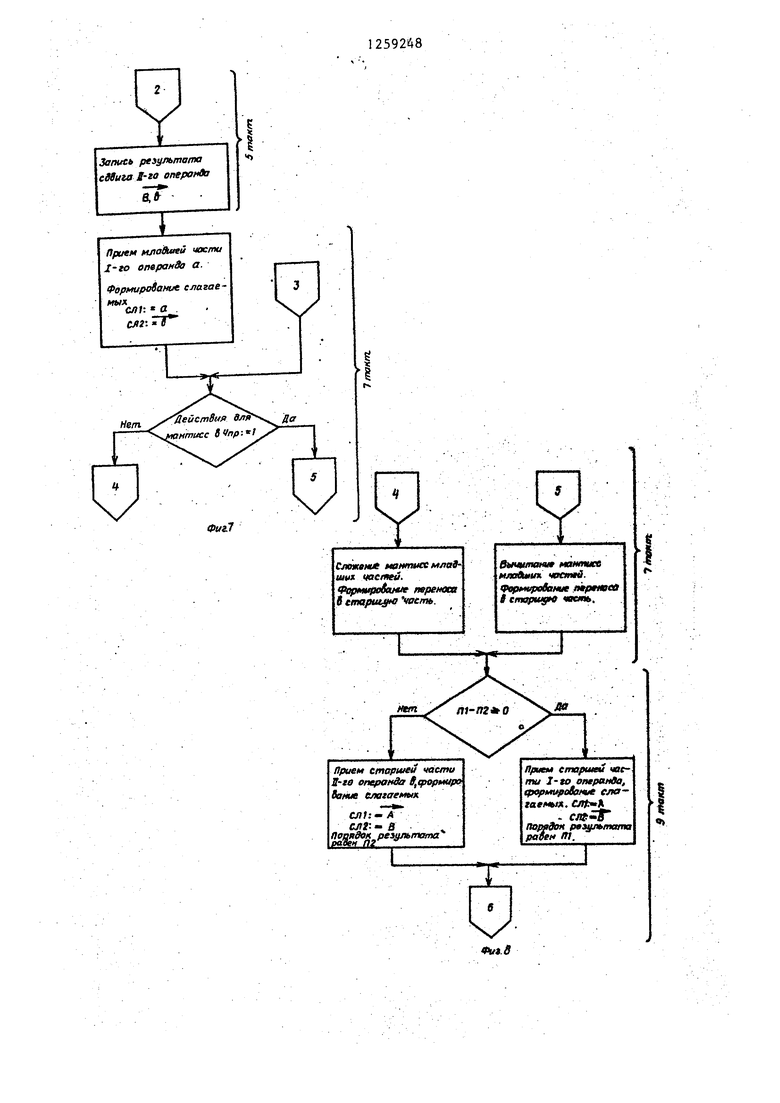

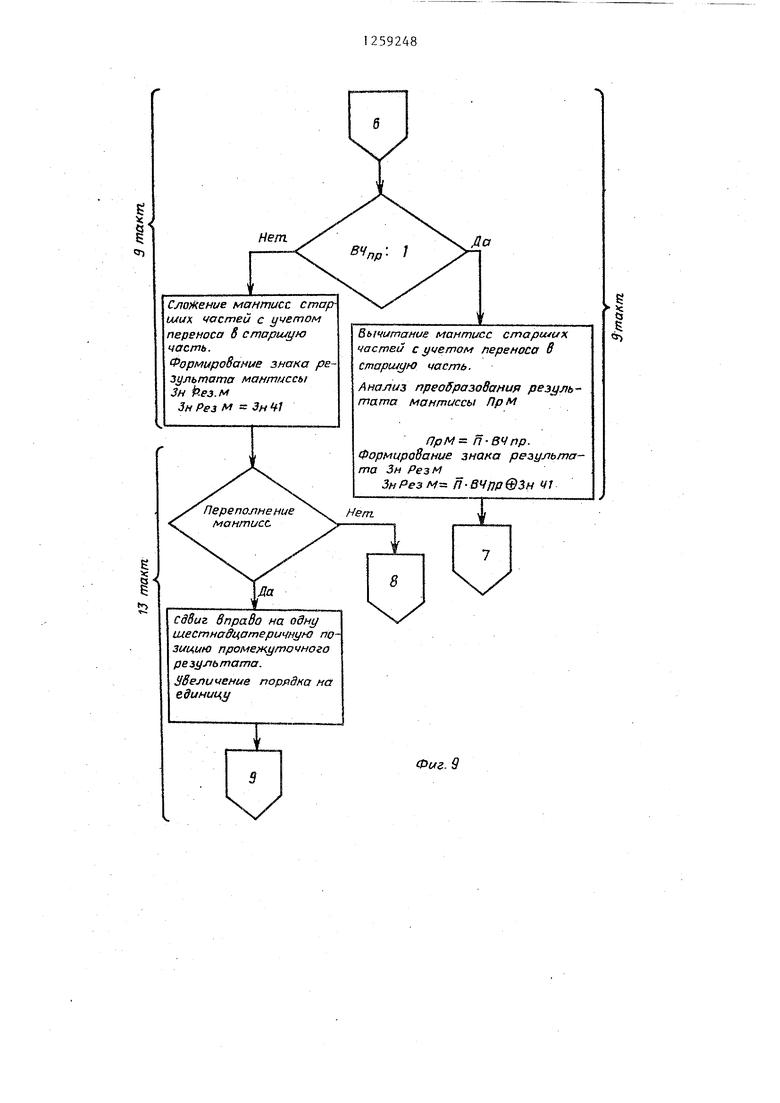

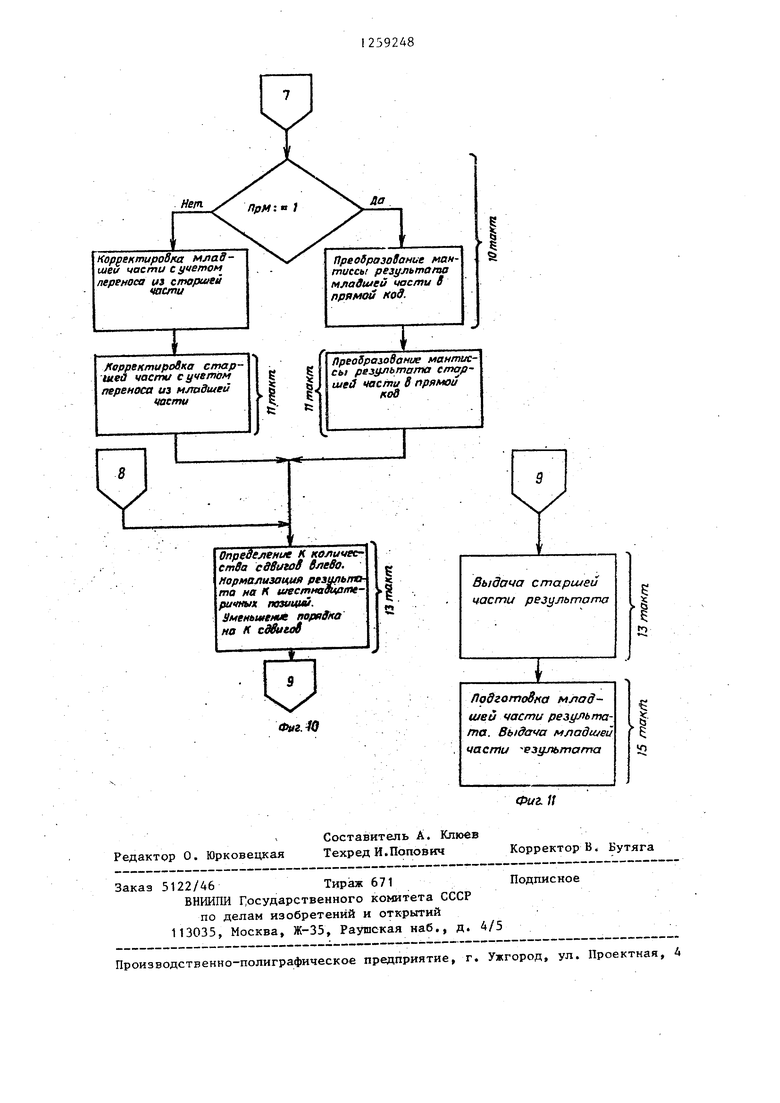

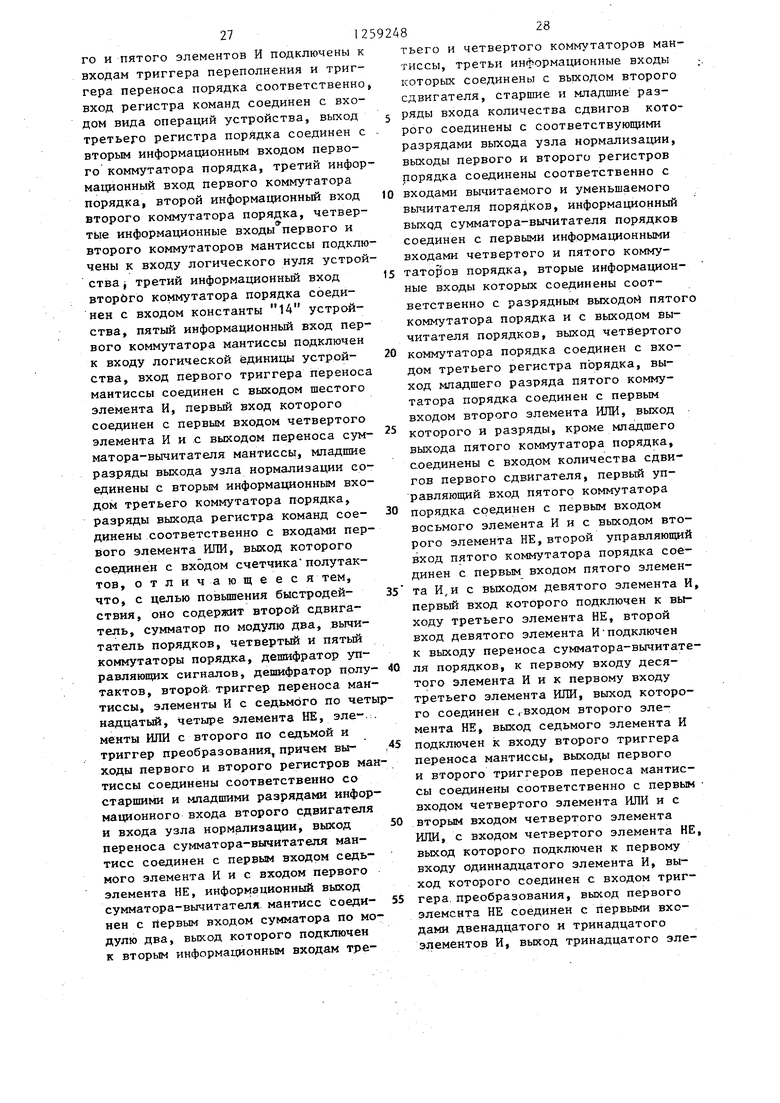

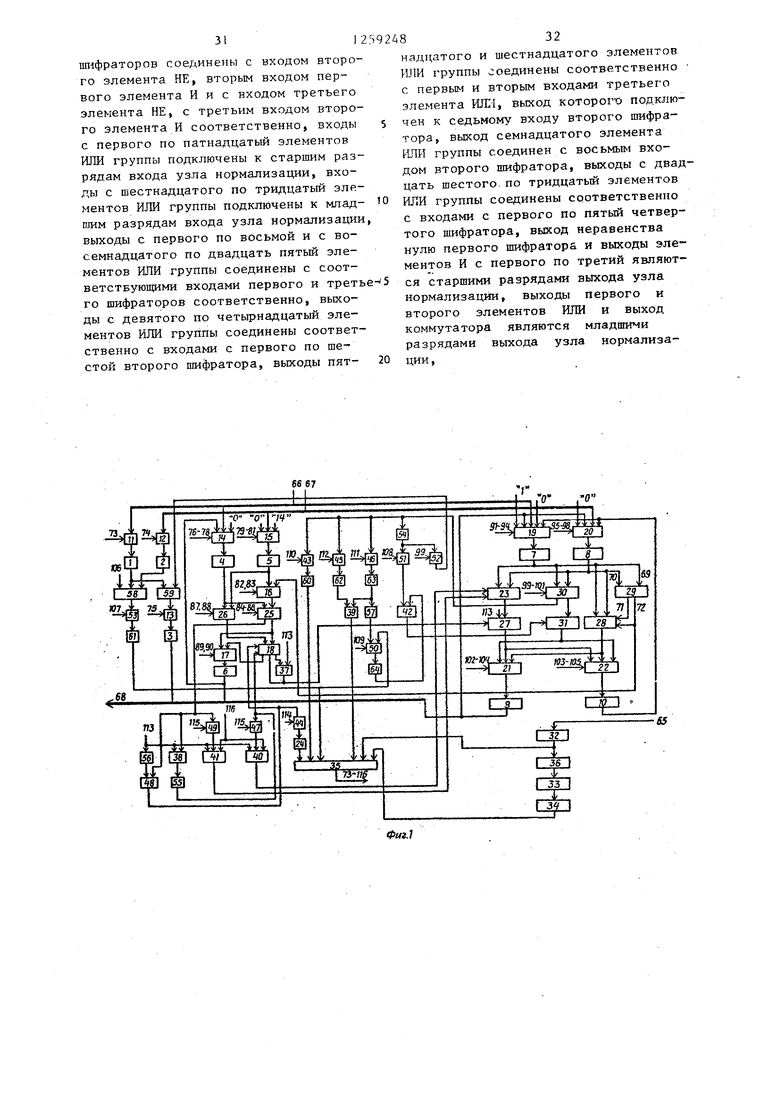

На фиг, 1 представлена структурная схема устройства с плавающей точкой , на фиг. 2 - структурная схема узла управления нормализацией; на фиг- 3 - алогоритм выполнения операций сложения (вычитания) над длинными операндами; на фиг. 6-11 - алгоритм выполнения операций сложения (вычитания) над расширенными операндами ./

Арифметическое устройство с плавающей точкой (фиг.1) содержит три триггера 1-3 знака, три регистра 4-6 порядка, четыре регистра 7-10 мантиссы, три элемента И 11-13, пят коммутаторов 14-18 порядка, пять коммутаторов 19-23 мантиссы, тригге 24 переноса порядка, сумматор--вычи- татель 25 порядков, вычитатель 26 порядков, два сдвигателя 27 и 28, узел 29 нормализации, сумматор-вы- читатель 30 мантисс, сумматор 31 по модулю два, регистр 32 команд,счетчик 33 полутактов, дешифратор ЗА полутактов, дешифратор 35 управляющих сигналов, семь элементов ИЛИ 36 42, одиннадцать элементов И 43-53, четыре элемента НЕ 54-57, два элемента ИСКгаОЧАЩЕЕ ИЛИ 58-59, тригге 60 переполнения, триггер 61 вычитания, два триггера 62 и 63 переноса

Сигнал

Наименование сигнала

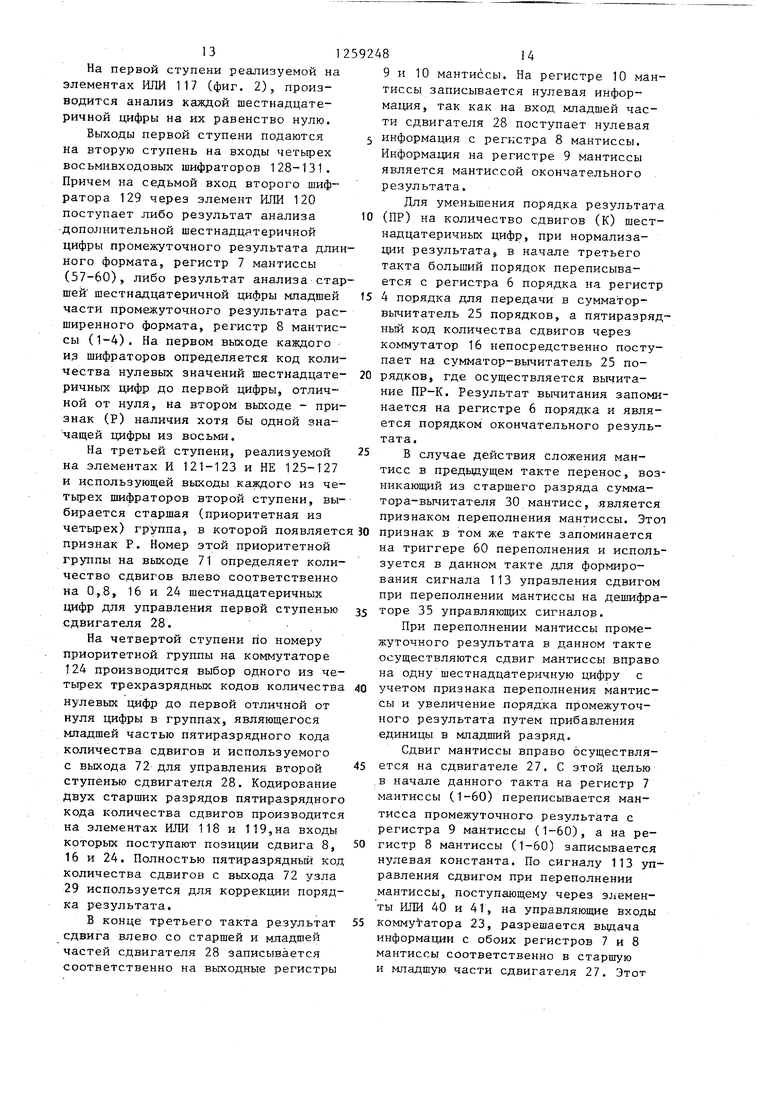

73Прием знака первого операнда на триггер 1 знака

74Прием знака второго операнда на триггер 2 знака

75Запись знака результата на триггер 3 знака

76Прием порядка первого операнда на регистр 4 порядка

77Перепись на регистр 4 порядка с регистра 6 порядка

78Запись константы О на регистр 4 порядка

79Прием порядка второго операнда на регистр 5 порядка

80Запись константы О на регистр 5 порядка

5

мантиссы, триггер 64 преобразования, вход 65 вида операции устройства, вход 66 первого операнда устройства, вход 67 второго операнда устройства, выход 68 результата устройства, первый и второй входы 69 и 70 узла 29 нормализации, старшие и младшие выходы 7 1 и 72 разрядов узла 29 нормализации и выходы 73-116 дешифратора 35 управляющих сигналов.

Узел 29 нормализации (фиг.2) содержит группу элементов ИЛИ 117, элементы ИЛИ Г18-123, коммутатор 124, элементы НЕ 125-127 и. шифраторы 128- 131.

Узлы обработки мантиссы имеют по 56 основных и четыре дополнительных разряда, Сдвигатели имеют удвоенную разрядность. Узлы обработки порядка имеют по семь основных и одному дополнительному разряду.

Функционирование арифметического устройства с плавающей запятой при вьтолнении операции сложения (вычитания) с нормализацией над операндами длинного формата.

Время реализации одного этапа при вьтолнении этих операций соответствует одному машинному такту. Каждый 0 нечетньй (четный) выход дешифратора 34 полутактов формирует управление регистрами, срабатывающими в начале (в конце) такта.

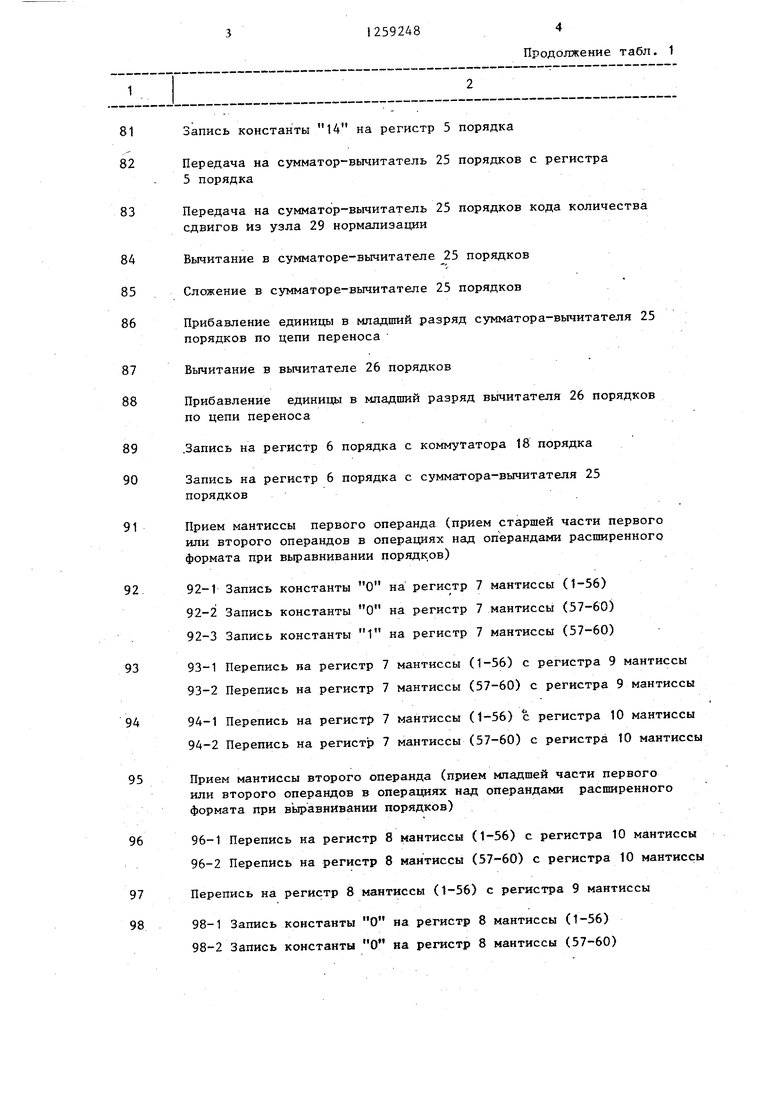

5 Перечень управляющих сигналов,

вырабатьшаемых дешифратором 35 управляющих сигналов, приведен в табл,1. Таблица 1

0

81Запись константы 14 на регистр 5 порядка

82Передача на сумматор-вычитатель 25 порядков с регистра 5 порядка

83Передача на сумматор-вычитатель 25 порядков кода количества сдвигов Из узла 29 нормализации

84Вычитание в сумматоре-вычитателе 25 порядков

85Сложение в сумматоре-вычитателе 25 порядков

86Прибавление единицы в мпадший разряд сумматора-вычитателя 25 порядков по цепи переноса

87Вычитание в вычитателе 26 порядков

88Прибавление единицы в младший разряд вычитателя 26 порядков по цепи переноса

89.Запись на регистр 6 порядка с коммутатора 18 порядка

90Запись на регистр 6 порядка с сумматора-вычитателя 25 порядков

91Прием мантиссы первого операнда (прием старшей части первого или второго операндов в операциях над операндами расширенного формата при вьфавнивании порядк,ов)

9292-1 Запись константы О на регистр 7 мантиссы (1-56) 92-2 Запись константы О на регистр 7 мантиссы (57-60) 92-3 Запись константы 1 на регистр 7 мантиссы (57-60)

9393-1 Перепись на регистр 7 мантиссы (1-56) с регистра 9 мантиссы 93-2 Перепись на регистр 7 мантиссы (57-60) с регистра 9 мантиссы

9494-1 Перепись на регистр 7 мантиссы (1-56) с регистра 10 мантиссы 94-2 Перепись на регистр 7 мантиссы (57-60) с регистра 10 мантиссы

95Прием мантиссы второго операнда (прием младшей части первого или второго операндов в операциях над операндами расширенного формата при выравнивании порядков)

9696-1 Перепись на регистр В мантиссы (1-56) с регистра 10 мантиссы 96-2 Перепись на регистр 8 мантиссы (57-60) с регистра 10 мантиссы

97Перепись на регистр 8 мантиссы (1-56) с регистра 9 мантиссы

9898-1 Запись константы О на регистр 8 мантиссы (1-56) 98-2 Запись константы О на регистр 8 мантиссы (57-60)

12592484

Продолжение табл. 1

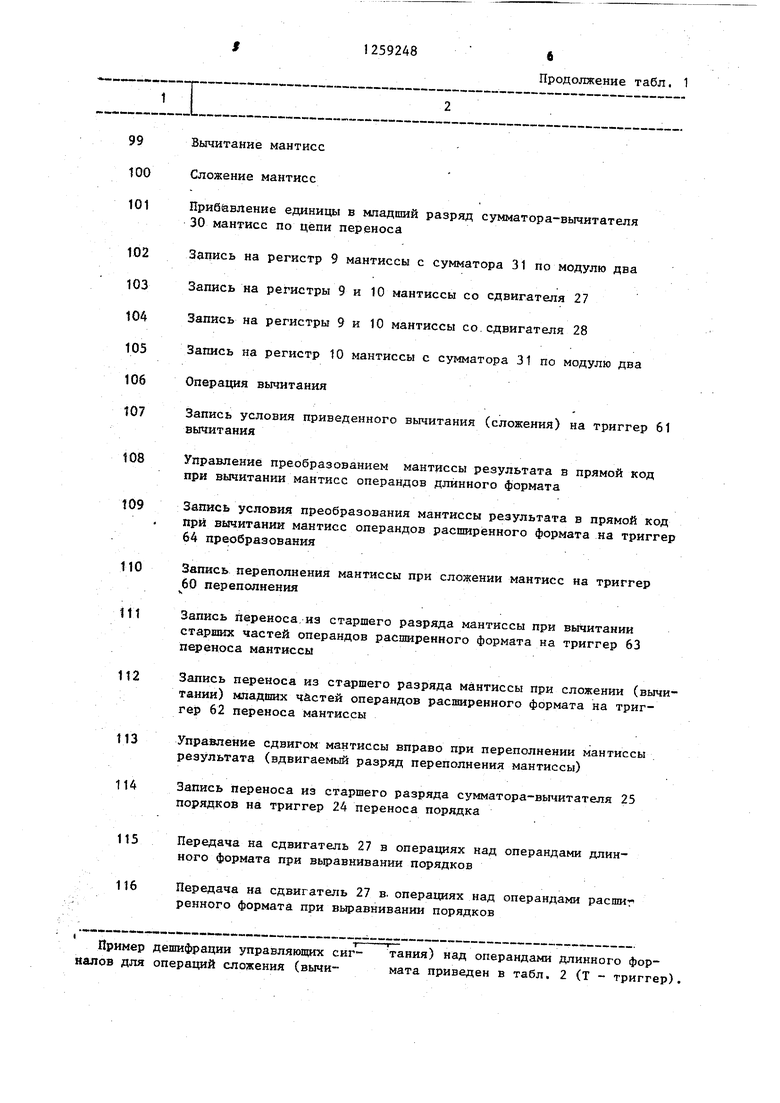

99Вычитание мантисс

100Сложение мантисс

101Прибавление единицы в младший разряд сумматора-вычитателя 30 мантисс по цепи переноса

102Запись на регистр 9 мантиссы с сумматора 31 по модулю два

103Запись на регистры 9 и 10 мантиссы со сдвигателя 27

104Запись на регистры 9 и 10 мантиссы со.сдвигателя 28

105Запись на регистр 10 мантиссы с сумматора 31 по модулю два

106Операция вычитания

107Запись условия приведенного вычитания (сложения) на триггер 61 вычитания

108Управление преобразованием мантиссы результата в прямой код при вычитании мантисс операндов длинного формата

109Запись условия преобразования мантиссы результата а прямой код при вычитании мантисс операндов расширенного формата на триггер 64 преобразования

110Запись переполнения мантиссы при сложении мантисс на триггер 60 переполнения

1..

111Запись переноса, из старшего разряда мантиссы при вычитании старших частей операндов расширенного формата на триггер 63 переноса мантиссы

112Запись переноса из старшего разряда мантиссы при сложении (вычитании) младших частей операндов расширенного формата на триггер 62 переноса мантиссы

113Управление сдвигом мантиссы вправо при переполнении мантиссы результата (вдвигаемый разряд переполнения мантиссы)

114Запись переноса из старшего разряда сумматора-выштателя 25 порядков на триггер 24 переноса порядка

115Передача на сдвигатель 27 в операциях над операндами длинного формата при выравнивании порядков

116Передача на сдвигатель 27 в. операциях над операндами расшиг ренного формата при выравнивании порядков

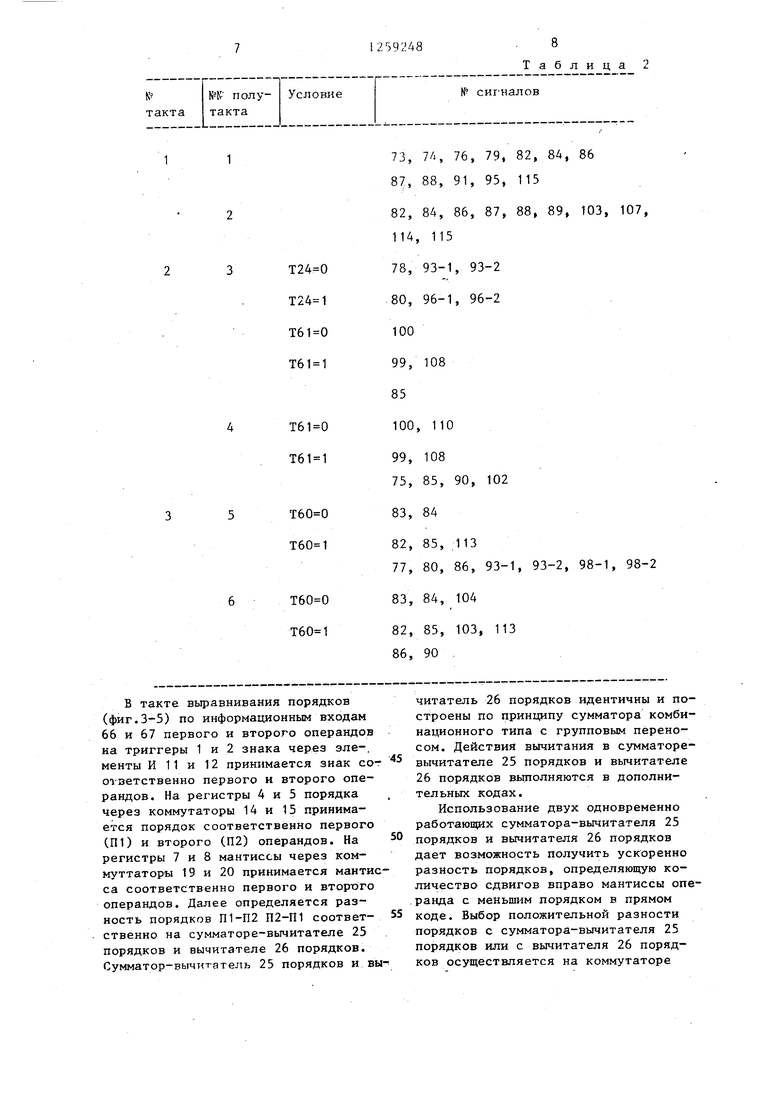

Пример дешифрации управляющих сиг- тания) над операндами длинного фор- напов для операций сложения (вычи- мата приведен в табл. 2 (Т - триггер)

259248 6

Продолжение табл. 1

Т61 1

Т61 1

В такте вьфавнивания порядков (фиг.3-5) по информационным входам 66 и 67 первого и второго операндов на триггеры 1 и 2 знака через эле-, менты И 11 и 12 принимается знак co ответственно первого и второго операндов. На регистры 4 и 5 порядка через коммутаторы 14 и 15 принимается порядок соответственно первого (П1) и второго (П2) операндов. На регистры 7 и 8 мантиссы через ком- муттаторы 19 и 20 принимается мантиса соответственно первого и втортэго операндов. Далее определяется разность порядков П1-П2 П2-П1 соответственно на сумматоре-вычитателе 25 порядков и вычитателе 26 порядков. Сумматор-вычитатель 25 порядков и вы

Таблица

82, 84, 86 115

88, 89 103, 107,

, 93-2, 98-1, 98-2

0

5

читатель 26 порядков идентичны и построены по принципу сумматора комбинационного типа с групповым переносом. Действия вычитания в сумматоре- вычитателе 25 порядков и вычитателе 26 порядков вьщолняются в дополнительных кодах.

Использование двух одновременно работающих сумматора-вычитателя 25 порядков и вычитателя 26 порядков дает возможность получить ускоренно разность порядков, определяющую количество сдвигов вправо мантиссы опе- .ранда с меньшим порядком в прямом коде. Выбор положительной разности порядков с сумматора-вычитателя 25 порядков или с вычитателя 26 порядков осуществляется на коммутаторе

9

18 в зависимости от значения переноса из старшего разряда сумматора- вычитателя 25 порядков. При наличии этого переноса на элементе И 48 формируется, разрешение выдачи положительной разности с сумматора-вычита- теля 25 порядков, а при отсутствии переноса из старшего разряда сумма- тора-вь читателя 25 порядков на элементах ШШ 38 и НЕ 55 вьфабатьшает- ся разрешение выдачи положительной разности с вычитателя 26 порядков. Кроме того, перенос из старшего разряда сумматора-вьгчитателя 25 порядков запоминается на триггере 24 переноса порядка и используется далее как признак большего порядка первого операнда при формировании управляющих сигналов на дешифраторе 35 управляющих сигналов. Сдвиг мантиссы вправо при выравнивании порядков производится на сдвигателе 27).

Данный сдвигатель предназначен дл сдвига 112-разрядного числа (расши- ренный формат) за один машинный такт Для сдвига мантиссы операнда длинног формата с меньшим порядком на сдвигатель 27 через коммутатор 23 передается информация с регистра 7 мантиссы в старшую часть сдвигателя либо с регистра 8 мантиссы в младшую часть сдвигателя. Выбор передачи информации с одного из этих регистров осуществляется в зависимости от значения переноса из старшего разряда сум матора-вычитателя 25 порядков. При наличии этого переноса на элементах И Д9 и ИЛИ 41 вырабатывается разрешение передачи на сдвигатель 27 с регистра 8 мантиссы, а при отсутстви этого переноса на элементах И 47 и ИЛИ 40 вырабатывается разрешение передачи на сдвигатель 27 с регистра 7 мантиссы. На сдвигателе 27 обеспечивается сдвиг вправо 0-31 шестиад- цатеричных цифр. С этой целью на управляющий вход сдвигателя 27 через коммутатор 18 подается количество сдвигов, определяемое положительной разностью порядков на сумматоре-вы- читателе 25 порядков или на вычита- теле 26 порядков.

В конце первого такта со старшей и младшей частей сдвигателя 27 результат сдвига записывается соответственно на регистры 9 и 10 мантиссы независимо от сдвигаемого операнда, включая дополнительную шестнадцате12

10

20

я; . 25 о 30-35и40

5924810

ричную цифру. Во втором такте (фиг.З) осуществляется сложение (вычитание) мантисс на сумматор е-вычитателе 30 мантисс.

В качестве сумматора-вычитателя мантисс используются сумматор-вы- читатель комбинационного типа с пирамидой переносов. В сумматоре- вычитателе 30 мантисс осуществляются действия над числами, представленными в прямых кодах. Вычитание чисел производится в обратных кодах (всегда вычитается второе число). Условие выполнения сумматором-вычи- 15 тателем 30 мантисс одного из действий (сложения или вычитания) определяется в предьщущем такте на основании анализа знака исходных операндов, а также типа заданной операции (сложение или вычитание) согласно формуле

ВЧ„р ЗнЧ1 + ЗнЧ2 + ЗнЧ2 + В, где ЗнЧ1 - знак первого операндаJ ЗнЧ2 - знак второго операнда ;

В - операция вычитания; ВЧпр - вычитание приведенное. Реализация этой формулы осуществляется на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 58 с запоминанием результата с выхода этого элемента на триггере 61 вычитания. В зависимости от его состояния в данном такте на дешифраторе 35 управляющих сигналов формируется сигнал 99 вычитания мантисс (триггер 61 вычитания 1) или сигнал 100 сложения мантисс (триггер 61 вычитания 0).

В начале такта сложения результат от сдвига операнда с меньшим порядком с регистра 9 мантиссы или с регистра 10 мантиссы переписывается;., соответственно на регистр 7 мантиссы j(1-60) (триггеры ) или на регистр 8 мантиссы (1-60) (триггер ). При переписи результата сдвига мантиссы с меньшим порядком на один из регистров 8 или 7 мантиссы на другом регистре сохраняется мантисса с большим, порядком, запомненная в начале предьщущего такта.

С выходов регистров 7 и 8 мантиссы информация поступает соответственно на первый и второй информационные входы сумматора-вычитателя 30 ман тисе,- где осуществляется сложение или вычитание мантисс.

Результат вычитания в сумматоре- вьиитателе 30 мантисс может полу45

50

55

читься в прямом или обратном коде. Признаком прямого или обратного кода при действии приведенного вычитания является соответственно наличие или отсутствие переноса из старшего 5 разряда сумматора-вычитателя 30 мантисс. В случае результата, выраженного в Обратном коде, для операции сложения (вычитания) над длинными операндами преобразование результата 10 в прямой код осуществляется в данном такте. Сигнал преобразования мантиссы формируется на элементе И 51 при действии вычитания мантисс и отсутствии переноса из старшего разряда 15 сумматора-вычитателя 30 мантисс.Преобразование осуществляется на сумматоре 31, на управляющий вход которого через элемент ИЛИ 42 поступает сигнал преобразования, а на информа- 20 ционный вход - результат вычитания с сумматора-вычитателя 30 мантисс.

В конце второго такта результат сложения (вычитания) мантисс записывается на регистр 9 мантиссы (1-60) через коммутатор 21.

Во втор ом такте формируется знак результата на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 59 на первый вход этого элемента поступает знак первого перанда, кото-30 рый хранится на триггере 1 знака от предьщущего такта, а на второй вход этого элемента подается сигнал,сформированный в данном такте на элементе И 52 при действии вычитания мантисс 55 и отсутствии переноса из старшего разряда сумматора-вычитателя 30 мантисс.

В конце данного такта знак результата записывается на триггер 3 знака 40 через элемент И 13.

В этом же такте порядок результата приравнивается к большему порядется на регистр 6 порядка через коммутатор 17,

В третьем тякте (фиг.З) вьшолня- ется нормализация или сдвиг вправо на одну шестнадцатеричную цифру мантиссы промежуточного результата с соответствующей коррекцией порядка.

Нормализация промежуточного результата заключается в сдвиге мантиссы влево до старшей шестнадцате- ричной цифры, отличной от нуля, и в уменьшении порядка на количестве сдвигов шестнадцатеричных цифр.

Сдвиг влево осуществляется на сдвигателе 28. Данньш сдвигатель предназначен для сдвига 116-разрядного промежуточного результата (расширенный формат с учетом дополнительной шестнадцатеричной цифры).

При нормализации промежуточного результата расширенного формата старшая часть результата (разряды 1-56) помещается на регистр 7 мантиссы (1-56),. причем на регистр 7 мантиссы (57-60) записывается нулевая ин формация, а младшая часть результата (разряды 57-116) - на регистр 8 мантиссы (1-60). При нормализации промежуточного результата длинного формата в начале такта нормализации результат сложения мантисс, полученный во втором такте, передается с регистра 9 мантиссы на регистр 7 мантиссы (1-60), на входном регистре 8 мантиссы (1-60) записывается нулевая константа.

Далее информация с обоих регист- .ров 7 и 8 мантиссы поступает соответственно на старшую и младшую части сдвигателя 28.

Сдвигатель 28 представляет узех из двух ступеней. На первой ступени осуществляется сдвиг на 0,8, 16 и 24

ку, которьШ хранится на одном их ре- шестнадцатеричных цифр влево, на вто

гистров 4 или 5 порядков от преды--. дущего такта. С этой целью в начале данного такта на один из регистров 4 Или 5 порядков, на котором хранится меньший порядок от предыдущего такта, записывается нулевая константа, С выхода регистров 4 и 5 порядков информация поступает на сумма- тор-вычитатель 25 порядков, где осуществляется сложение большего порядка с нулевой константой. В конце такта результат от сложения йа сумма- торё-вычитателе 25 порядков эаписывается на регистр 6 порядка через коммутатор 17,

В третьем тякте (фиг.З) вьшолня- ется нормализация или сдвиг вправо на одну шестнадцатеричную цифру мантиссы промежуточного результата с соответствующей коррекцией порядка.

Нормализация промежуточного результата заключается в сдвиге мантиссы влево до старшей шестнадцате- ричной цифры, отличной от нуля, и в уменьшении порядка на количестве сдвигов шестнадцатеричных цифр.

Сдвиг влево осуществляется на сдвигателе 28. Данньш сдвигатель предназначен для сдвига 116-разрядного промежуточного результата (расширенный формат с учетом дополнительной шестнадцатеричной цифры).

При нормализации промежуточного результата расширенного формата старшая часть результата (разряды 1-56) помещается на регистр 7 мантиссы (1-56),. причем на регистр 7 мантиссы (57-60) записывается нулевая ин формация, а младшая часть результата (разряды 57-116) - на регистр 8 мантиссы (1-60). При нормализации промежуточного результата длинного формата в начале такта нормализации результат сложения мантисс, полученный во втором такте, передается с регистра 9 мантиссы на регистр 7 мантиссы (1-60), на входном регистре 8 мантиссы (1-60) записывается нулевая константа.

Далее информация с обоих регист- .ров 7 и 8 мантиссы поступает соответственно на старшую и младшую части сдвигателя 28.

Сдвигатель 28 представляет узех из двух ступеней. На первой ступени осуществляется сдвиг на 0,8, 16 и 24

шестнадцатеричных цифр влево, на вто

рой ступени - сдвиг на 0-7 шестнадцатеричных цифр влево. Управление первой и второй ступенями сдвигателя 28 осуществляется с узла 29 нормализации соответственно по входам 71 и 72. В узел 29 (фиг. 2) по входам 69 и 70 подается та же информация, что и на данный сдвигатель, т.е. с регистров 7 и В мантиссы. Далее в узле 29 определяется количество нулевых шестнадцатеричных цифр до старшей цифры, отличной от нуля, последовательно на четырех ступенях.

На первой ступени реализуемой на элементах ИЛИ 117 (фиг. 2), производится анализ каждой шестнадцате- ричной цифры на их равенство нулю.

Выходы первой ступени подаются на вторую ступень на входы четьфех восьмивходовых шифраторов 128-131. Причем на седьмой вход второго шифратора 129 через элемент ИЛИ 120 поступает либо результат анализа дополнительной шестнадцатеричной цифры промежуточного результата длинного формата, регистр 7 мантиссы (57-60), либо результат анализа старшей шестнадцатеричной цифры мпадшей части промежуточного результата расширенного формата, регистр 8 мантиссы (1-4). На первом выходе каждого из шифраторов определяется код количества нулевых значений шестнадцате- ричных цифр до первой цифры, отличной от нуля, на втором выходе - признак (Р) наличия хотя бы одной зна- чащей цифры из восьми.

На третьей ступени, реализуемой на элементах И 121-123 и НЕ 125-127 и использующей выходы каждого из четырех шифраторов второй ступени, выбирается старшая (приоритетная из

четырех) группа, в которой появляется 30 признак в том же такте запоминается признак Р. Номер этой приоритетной на триггере 60 переполнения и испольгруппы на выходе 71 определяет количество сдвигов влево соответственно на 0,8, 16 и 24 шестнадцатеричных цифр для управления первой ступенью сдвигателя 28.

На четвертой ступени по номеру приоритетной группы на коммутаторе 124 производится выбор одного из четьфех трехразрядных кодов количества

нулевых цифр до первой отличной от нуля цифры в группах, являющегося младшей частью пятиразрядного кода количества сдвигов и используемого с выхода 72 для управления второй ступенью сдвигателя 28. Кодирование двух старших разрядов пятиразрядного кода количества сдвигов производится на элементах ИЛИ 118 и 119,на входы которых поступают позиции сдвига 8, 16 и 24. Полностью пятиразрядный код количества сдвигов с выхода 72 узла 29 используется для коррекции порядка результата.

Б конце третьего такта результат сдвига влево со старшей и младшей частей сдвигателя 28 записывается соответственно на выходные регистры

9 и 10 мантиссы. На регистре 10 мантиссы записывается нулевая информация, так как на вход младшей части сдвигателя 28 поступает нулевая

информация с регистра 8 мантиссы. Информация на регистре 9 мантиссы является мантиссой окончательного , результата.

Для уменьшения порядка результата

(ПР) на количество сдвигов (К) шест- надцатеричных цифр, при нормализации результатаJ в начале третьего такта больший порядок переписывается с регистра 6 порядка на регистр

4 порядка для передачи в сумматор- вычитатель 25 порядков, а пятиразрядный код количества сдвигов через коммутатор 16 непосредственно поступает на сумматор-вычитатель 25 порядков, где осуществляется вычитание ПР-К. Результат вычитания запоминается на регистре 6 порядка и является порядком окончательного результата.

в случае действия сложения мантисс в предыдущем такте перенос, возникающий из старшего разряда сумма- тора-вычитателя 30 мантисс, является признаком переполнения мантиссы. Этот

зуется в данном такте для формирования сигнала 113 управления сдвигом при переполнении мантиссы на дешифраторе 35 управляющих сигналов.

При переполнении мантиссы промежуточного результата в данном такте осуществляются сдвиг мантиссы вправо на одну шестнадцатеричную цифру с

учетом признака переполнения мантиссы и увеличение порядка промежуточного результата путем прибавления единицы в младший разряд.

Сдвиг мантиссы вправо осуществляется на сдвигателе 27. С этой целью .в начале данного такта на регистр 7 мантиссы (1-60) переписывается мантисса промежуточного результата с регистра 9 мантиссы (1-60), а на регистр 8 мантиссы (1-60) записывается нулевая константа. По сигналу 113 управления сдвигом при переполнении мантиссы, поступающему через элементы ИЛИ 40 и 41, на управляющие входы

коммутатора 23, разрешается выдача информации с обоих регистров 7 и 8 мантиссы соответственно в старшую и младшую части сдвигателя 27. Этот

же уп равляющий сигнал является вдви- гаемьм разрядом на сдвигателе 27 при переполнении мантиссы.

Количество сдвигов, равное одной шестнадцатеричной цифре, формирует- ся также по сигналу управления сдвигом при переполнении мантиссы, который поступает на второй вход элемента ИШ 37, на первый вход которог поступает младший разряд кода количе- ства сдвигов в такте выравнивания порядков. По другим разрядам кода количества сдвигов при наличии сигнала 113 управления сдвигом при переполнении мантиссы ведается нулевая информация.

В конце третьего такта при переполнении мантиссы информация с выходов старшей и младшей частей сдви- гателя 27 записывается соответствен- но на регистры 9 и 10 мантиссы.

Для операции сложения (вычитания) над длинными операндами информации на регистре 9 мантиссы является мантиссой окончательного результата.

При сдвиге мантиссы промежуточного результата вправо на одну шестнадца- теричную цифру.порядок промежуточно

го результата увеличивается путем прибавления единицы на сумматоре- вычитателе 25 порядков переноса по цепи в младший разряд большего порядка, переписанного в начале данного такта на регистр 4 порядка с регистра 6 порядка (на регистре 5 порядка записывается нулевая констата) ..

Результат сложения с сумматора- вычитателя 25 порядков записывается на регистр 6 порядка и является порядком окончательного результата.

В конце третьего такта с триггера 3 знака, с регистра 6 порядка с регистра 9 мантиссы выдается результат по выходу 68 результата устройства.;

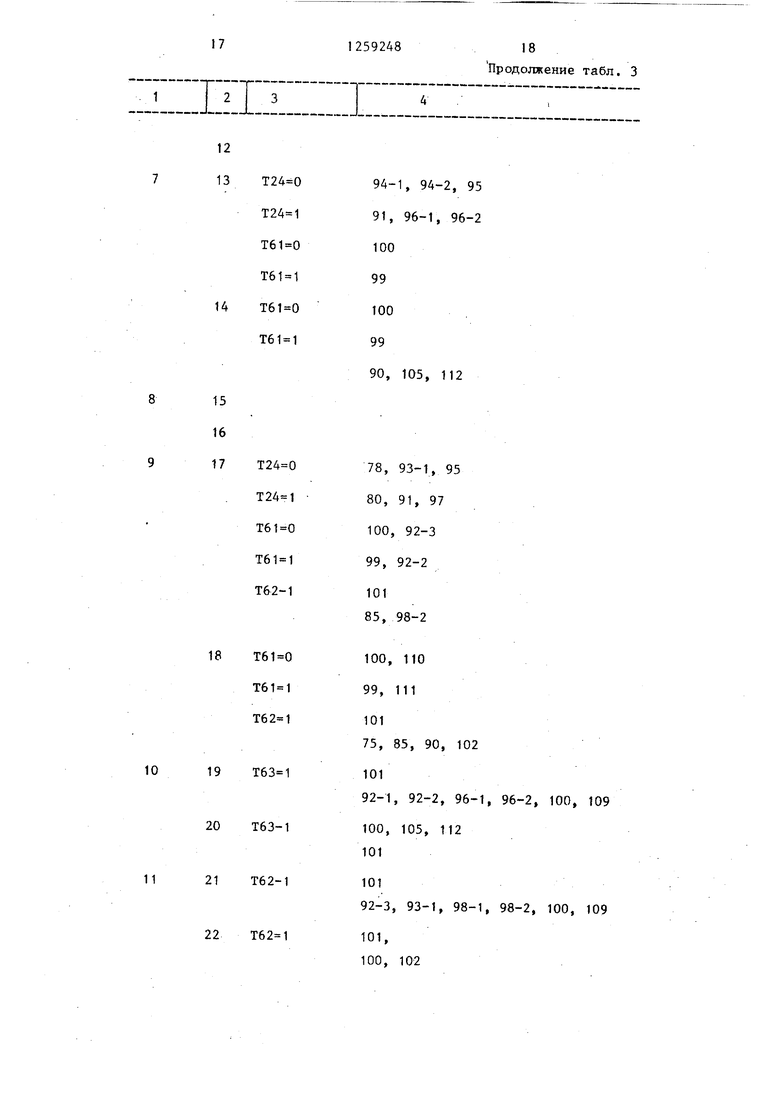

Функционирование арифметического устройства при выполнении операций сложения (вычитания) над расширенными операндами по действиям в каждом MainKHHOM такте.

Пример дешифрахщи управлянзщих сигналов для операций сложения (вычитания) над операндами расширенного формата приведен в табл. 3.

Т а б ли ц а 3

73, 74, 76, 79, 82, 84 86, 87, 88 82, 84, 86, 87, 88, 89, 107, 114

91, 95, 116 103, 116

91, 95, 116 ,103 116

75, 85, 90, 102

1019 101

92-1, 92-2, 96-1, 96-2, 100, 109

20 Т63-1 100, 105, 112

101

1121 Т62-1 101

92-3, 93-1, 98-1, 98-2, 100, 109

22 101,

100, 102

23 24 25

26

27 28 29 30

Операция сложения (вычитания) над расширеннь1ми операндами вьшолняется в следующей последовательности: определение разности порядков, вьфавнива ние первого операнда; выравнивание второго операнда} сложение младших частей, сложение старших частей; коррекция мпадшей части результата; коррекция старшей части результата} нормализация расширенного результата и вьщача старшей части результата} вьщача Лладшей части результата.

Каждое указанное действие вьтол- няется за один машинный такт. Но между действиями, связанными с приемом операндов по информационным входам 66 и 67, производится пропуск в один машинный такт. Вьщача результата по выходу 68 результата устройства осуществляется в нечетных тактах, поэтому перед каждой вьщачей производится также пропуск в один машинный такт. Таким образом, первые пять действий выполняются в первом, третьем, пятом, седьмом и девятом тактах (второй, четвертый, шестой и восьмой такты пропуска), а последние два действия - в тринадцатом и пят- надцатом тактах (двенадцатый и четырнадцатый такты пропуска).

93-1, 96-1, 96-2

77, 81, 84, 92-2, 94-1, 98-1, 98-2, 100 84, 86, 90, 100, 102

В алгоритме операций с расширенной разрядностью (фиг. 6-11) указываются номера тактов, в которых осуществляются перечисленные действия.

В первом такте для определения количества сдвигов при вьфавнивании порядков определяется разность порядков. В начале такта на триггеры 1 и 2 знака и регистры 4 и 5 порядка по информационным входам 66 и 67 со ответственно принимаются знаки и порядки первого и второго операндов, входящие в состав старших частей, операндов. Дальнейшие действия по вычислению разности порядков и формированию количества сдвигов для управления сдвигателем 27 организуются аналогично действиям при выполнении операций сложения (вычитания) над операндами длинного формата.

В данном такте формируется вид действий (сложение, вычитание) над мантиссами в сумматоре-вычитателе 30 мантисс аналогично формированию этих действий для операций сложения (вычитания) над длинными операндами в первом такте (выравнивание порядков) ,

В третьем и пятом тактах осуществляется выравнивание порядков. В начале третьего такта на регистры 7 и 8 мантиссы по информационным входам 66 и 67 принимаются соответственно старшая и младшая части первого операнда. По сигналу 116 управления передачей на Ьдвигатель 27 в операциях над расширенными операндами, который подается с дешифратора 35 управляющих сигналов через элементы ИЛИ 40 и 41 на оба управляющих входа коммутатора 23, старшая и младшая части первого операнда с выходов регистров 7 и 8 мантиссы через коммутатор 23 поступают соответственно на старшую и младшую части сдвига- теля 27 ДЛЯ сдвига вправо на количество сдвигов, определенное в первом такте. Старшая и младшая части р.езультата от сдвига вправо первого операнда записываются соответ- ственно на регистры 9 и 10 мантиссы (с учетом дополнительной .шестнадца- теричной цифры) независимо от знака разности порядков,

В начале пятого такта на регист- ры 7 и 8 мантиссы по информационным входам 66 и 67 принимаются соответственно старшая и младшая части второго опера-да. Далее действия на сдвигателе 27 в этом такте аналогич- .ны действия в третьем такте,

Старшая и младшая части результата от сдвига вправо второго операнда записываются соответственно на регистры 9 и 10 мантиссы при условии П1-П2 0. В случае П1-П2 0 на регистрах 9 и 10 мантиссы сохраняется результат от сдвига вправо первого операнда, полученный в предьщущем такте.

В седьмом такте осуществляется сложение (вычитание) младших частей мантисс первого и второго операндов. В случае выравнивания первого операнда (111-П2 0) в третьем такте в на- чале данного такта на входной регист 7 мантиссы (1-60) переписывается млашая, часть первого операнда с регистра 10 мантиссы, а на регистр 8 мантиссы по информационному входу 67 принимается младшая часть второго операнда. Информация с регистров 7 м 8 мантиссы поступает соответствен- ио на первый и второй информационные входы сумматора-вычитателя 30 мантис где осуществляется сложение (вычитание) младших частей. Мантисса результата младших частей запоминаете

на регистре 10 мантиссы. Перенос из старшего разряда сумматора-вычитателя 30 мантисс фиксируется на триггере 62 и используется в следующем такте для формирования сигнала 101 . прибавления единицы в младший .разряд сумматора-вычитателя 30 мантисс по цепи переноса на дешифраторе 35 уп- равляющих сигналов.

В случае выравнивания второго операнда (П1-П2 0) в начале данного такта младшая часть второго операнда переписывается с регистра 10 мантиссы на регистр 8 мантиссы (1-60), а младшая часть первого операнда принимается на регистр 7 мантиссы по информационному входу 66. Даль- шейшие действия в этом такте аналогичны действиям, описанным для случая выравнивания первого операнда.

В девятом такте производится сложение (вычитание) старших частей первого и второго операндов. В начале такта, если ранее выравнивается первый операнд, на регистр 7 мантиссы (1-56) переписьшается старшая часть первого операнда с регистра 9 мантиссы, а старшая часть второго операнда принимается на регистр 8 мантиссы по информационному входу 67. Старшие части операндов и промежуточных результатов расширенного формата имеют 56 разрядов. А действия сложения (вычитания) над ними выполняются на 60-разрядном сумматоре- вычитателе 30 мантисс. Поэтому перед вычитанием на регистры 7 и 8 мантиссы (57-60) записывается нулевая константа, пере,ц сложением на регист 8 мантиссы (57-60) записывается также нулевая константа, а на регистр 7 мантиссы (57-60) - константа 1, обеспечивающая прибавление единицы в младший (56-й) разряд результата старшей части по цепи переноса младшего (60-го) разряда сумматора-вычи- тателя 30 мантисс.

Далее информация с регистров 7 и 8 мантиссы подается соответственно на первьй и второй информационные входы сумматора-вычитателя 30 мантисс. Кр.оме того, по цепи переноса в младший разряд сумматора-вычита- теля 30 мантисс подается перенос, запомненньй на триггере 62 в предыдущем такте. Результат сложения (вычитания) старших частей запоминается на регистре 9 мантиссы.

231259248

В начале такта, если ранее выравнивался второй операнд, на регистр

7мантиссы принимается старшая часть первого операнда по информационному входу 66, а старшая часть второго операнда переписывается на регистр

8мантиссы (1-56) с регистра 9 мантиссы; Дальнейшие действия с мантиссами в данном такте аналогичны действиям при выравнивании первого операнда.

В случае действия сложения мантисс перенос из старшего разряда сум- матора-вьпштателя 30 мантисс характеризует переполнение мантиссы промежуточного результата. Этот перенос запоминается на триггере 60 и используется в дальнейших действиях аналогично его использованию в опе10

15

п с з мл ст ра ти ис ла ши ма та си

ет та во ча Дл

рациях над длинными операндами в так- 20 часть результата, полученная в девяте нормализации. В случае действия вычитания мантисс перенос из старшего разряда запоминается на триггере 63 и в следующем такте используется для формирования сигнала 101 прибавления единицы в младший разряд сумматора-вычитателя 30 мантисс по цепи переноса на дешифраторе 35 управляющих сигналов. Отсутствие переноса используется как условие преобразования мантиссы в прямой код

в последующих тактах.

В данном такте формируются знак результата с запоминанием на триггере 3 знака и порядок результата ,с запоминанием на регистре 6 порядка аналогично формированию знака результата и порядка результата для

операций сложения (вычитания) над операндами длинного формата во втором такте (сложение).

В десятом такте осуществляется коррекция младшей части результата на перенос из старшего разряда, возникающий при вычитании старших частей в предыдущем такте. С этой целью в начале данного такта младшая часть результата с регистра 10 мантиссы переписывается на регистр 8 мантиссы (1-60), на регистре 7 ман-. тиссы (1-60) устанавливается нулевая информация. Далее информация с обоих регистров 7 и 8 мантиссы поступает соответственно на первый и вто30

35

том такте, передается на регистр 7 м мантиссы (1-56) с регистра 9 мантиссы, на регистр 7 мантиссы (57-60)

записывается константа 1, а на jf

регистре 8 мантиссы (1-60) устанавливается нулевая информация. Далее в сумматоре-вьгаитателе 30 мантисс осуществляются действия, аналогичные действиям в предьщущем такте. Результат скорректированной старшей части записывается на регистр 9 мантиссы.

При вычитании мантисс старших частей в девятом такте при отсутствии переноса из старшего разряда в десятом такте осуществляется преобразование младшей части результата в прямой код, а в одиннадцатом - преобразование в прямой код старшей части результата. Реализация преобразования в прямой код старшей и младшей частей результата аналогична., выполнению преобразования при вычитании мантисс операндов длинного формата во втором такте (сложение).

В тринадцатом такте осуществляется нормализация или сдвиг вправо на одну щестнадцатеричную цифру промежуточного результата. В начале такта на регистр 7 мантиссы (1-56) и на регистр 8 мантиссы (1-60) соответственно с регистров 9 и 10 мантиссы передаются старшая и младшая части результата, причем на регистр 7 ман4Q

45

50

рой информационные входы сумматора- 55 тиссы (57-60) записывается нулевая

вычитателя 3- мантисс для сложения с переносом, запомненным на триггере 63 в предыдущем такте и поступающим

24

0

по цепи переноса в младший разряд сумматора-вычитателя 30 мантисс. Результат сложения скорректированной младшей части запоминается на регистре 10 мантисс. Перенос из старшего разряда сумматора-вычитателя 30 мантисс запоминается на триггере 62 и используется для формирования сигнала 101 прибавления единицы в младший разряд сумматора-вычитателя 30 мантисс по цепи переноса в следующем такте на дешифраторе 35 управляющих сигналов.

Б одиннадцатом такте осуществляется коррекция старшей части результата на перенос из старшего разряда, возникающий при коррекции младшей части результата в предьщущем такте. Для этого в данном такте старшая

0

5

том такте, передается на регистр 7 м мантиссы (1-56) с регистра 9 мантиссы, на регистр 7 мантиссы (57-60)

записывается константа 1, а на jf

регистре 8 мантиссы (1-60) устанавливается нулевая информация. Далее в сумматоре-вьгаитателе 30 мантисс осуществляются действия, аналогичные действиям в предьщущем такте. Результат скорректированной старшей части записывается на регистр 9 мантиссы.

При вычитании мантисс старших частей в девятом такте при отсутствии переноса из старшего разряда в десятом такте осуществляется преобразование младшей части результата в прямой код, а в одиннадцатом - преобразование в прямой код старшей части результата. Реализация преобразования в прямой код старшей и младшей частей результата аналогична., выполнению преобразования при вычитании мантисс операндов длинного формата во втором такте (сложение).

В тринадцатом такте осуществляется нормализация или сдвиг вправо на одну щестнадцатеричную цифру промежуточного результата. В начале такта на регистр 7 мантиссы (1-56) и на регистр 8 мантиссы (1-60) соответственно с регистров 9 и 10 мантиссы передаются старшая и младшая части результата, причем на регистр 7 манQ

5

константа. Дальнейшие действия в данном такте аналогичны действиям, выполняемым в третьем такте (нормаизация) при действии над операндаи длинного формата. Тринадцатьй акт заканчивается выдачей знака езультата, порядка старшей части реультата и мантиссы старшей части 5 езультата на вькод 68 результата стройства,

В пятнадцатом такте осуществляется передача мантиссы младшей части езультата с регистра. 10 на регистр Ю 9 мантиссы через сзгмматор-вычитатель 30 мантисс, сумматор 31 по модулю два и коммутатор 21. Передача через сум- матор-вычитатель 30 мантисс производится путем сложения мантиссы мпад- 15 шей части результата, переписанной в начале такта на регистр 7 мантиссы с регистра 10 мантиссы и нулевой информации, записанной на регистр 8 мантиссы также в начале так- 20 та. В этом такте формируется младшей части результата из порядка старшей части результата путем уменьшения его на 14. В начале данного такта порядок старшей части результата передается с регистра 6 порядка на регистр А порядка, а на регистр 5 порядка записывается константа 14, Затем информация с регистров 4 и 5 порядка подается соответственно на 30 первый и второй информационные входы сумматора-вычитателя 25 порядков. Результат вычитания, т.е. порядок младшей части результата, записывается на регистр 6 порядка, Пятнад- 35 цатый такт и выполнение операции сложения (вычитания) над операндами расширенного формата заканчивается выдачей младшей части мантиссы результата и порядка младшей части результа- 40 та на выход 68 результата устройства,

Формула изобретения

1, Арифметическое устройство с 45 плавающей точкой, содержащее три триггера знака, три регистра поря,ц- ка, четыре регистра мантиссы, три коммутатора порядка, пять коммутаторов мантиссы, сумматор-вычитатель 50 порядков, сумматор-вычитатель мантисс, первый сдвигатапь, триггер переполнения, триггер переноса порядка, регистр команд, шесть элементов И, первьй и второй элементы SS ИСКЛЮЧАЩЕЕ ИЛИ, узел нормализации, первый триггер переноса мантисс, триггер вычитания, счетчик полутактов, первый элемент ИЛИ, причем установка разрядов входов первого и второго операндов устройства соединена соответственно с первыми входами пер- вого и второго элементов И, выходы которых соединены с входами соответствующих триггеров знака, выходы которых соединены соответственно с первым и вторым входами первого элемента ИСКЛЮЧАЩЕЕ ИЛИ, вькод первого триггера знака соединен с первым входом второго элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход которого соединен с первым входом третьего элемента И, выход которого соединен с входом третьего триггера знака, разряды порядка входов первого и второго операндов устройства соединены соответственно с первыми информационньп входами первого и второго коммутаторов порядка, выходы которых соединены с входами соответствующих регистров порядка, выход второго регистра порядка соединен с первым информационным входом третьего коммутатора порядка, вькоды первого регистра порядка и третьего коммутатора порядка соединены соответственно с первым и вторым входами сумматора- вычитателя порядков, разряды мантиссы входов первого и второго операндов устройства соединены соответственно с первыми информационными входами первого и второго коммутаторов мантиссы, выход которых соединен с входами соответствующих регистров мантиссы, вьшоды которых соединены соответственно с первьпч и вторым информационным входа1 ш сумматора-вычитателя мантисс, вторые и третьи информационные входы первого и второго коммутаторов мантиссы подключены к выходам третьего я четвертого регистров мантиссы соответственно, входы которых соединены с выходами тре-. тьего и четвертого коммутаторов мантиссы соответственно,, первые информационные входы которых подключены к выходу первого сдвигателя, информационный вход которого соединен с выходом пятого коммутатора мантиссы, первые и вторые информационные входы которого подключены к выходам первого и второго регистров мантиссы соответственно, выходы третьего триггера знака и третьих регистров порядка и мантиссы соединены с выходом результата устройства, выходы четвертоГО и пятого элементов И подключены к входам триггера переполнения и триггера переноса порядка соответственно вход регистра команд соединен с входом вида операций устройства, выход третьего регистра порядка соединен с вторым информационным входом первого коммутатора порядка, третий информационный вход первого коммутатора порядка, второй информационный вход второго коммутатора порядка, четвертые информационные входы первого и второго коммутаторов мантиссы подключены к входу логического нуля устройства f третий информационньш вход вторбго коммутатора порядка соединен с входом константы 14 устройства, пятый информационный вход первого коммутатора мантиссы подключен к входу логической единицы устройства, вход первого триггера переноса мантиссы соединен с выходом шестого элемента И, первый вход которого соединен с первым входом четвертого элемента И и с выходом переноса сум- матора-вычитателя мантиссы, младшие разряды выхода узла нормализации соединены с вторым информационным входом третьего коммутатора порядка, разряды выхода регистра команд соединены соответственно с входами первого элемента ИЛИ, выход которого соединен с входом счетчика полутактов, отличающеес я тем, что, с целью повьшения быстродействия, оно содержит второй сдвига- тель, сумматор по модулю два, вычи- татель порядков, четвертый и пятый коммутаторы порядка, дешифратор управляющих сигналов, дешифратор полутактов, второй триггер переноса мантиссы, элементы И с седьмого по четынадцатый, четыре элемента НЕ, эле-.;. менты ИЛИ с второго по седьмой и триггер преобразования, причем выг коды первого и второго регистров мантиссы соединены соответственно со старшими и младшими разрядами информационного входа второго сдвигатепя и входа узла нормализации, выход переноса сумматора-вычитателя мантисс соединен с первым входом седьмого элемента И и с входом первого элемента НЕ, информационный выход сумматора-вычитателя. мантисс соединен с Лервым входом сумматора по модулю два, выход которого подключен к вторым информационным входам тре

20

25

5

10

0

5

тьего и четвертого коммутаторов мантиссы, третьи информационные входы которых соединены с выходом второго сдвигателя, старшие и младшие разряды входа количества сдвигов которого соединены с соответствующими разрядами выхода узла нормализации, выходы первого и второго регистров порядка соединены соответственно с входами вычитаемого и уменьшаемого вычитателя порядков, информационный выход сумматора-вычитателя порядков соединен с первыми информационными входами четвертого и пятого комму- 15 таторов порядка, вторые информационные входы которых соединены соответственно с разрядным выходом пятого коммутатора порядка и с выходом вычитателя порядков, выход четвертого коммутатора порядка соединен с входом третьего регистра порядка, выход младшего разряда пятого коммутатора порядка соединен с первым входом второго элемента ИЛИ, выход которого и разряды, кроме младшего выхода пятого коммутатора порядка, соединены с входом количества сдвигов первого сдвигателя, первый уп- равляюш 1й вход пятого коммутатора порядка соединен с первым входом восьмого элемента И и с вькодом второго элемента НЕ, второй управляющий вход пятого коммутатора порядка соединен с первым входом пятого элемента И,и с вькодом девятого элемента И, первый вход которого подключен к выходу третьего элемента НЕ, второй вход девятого элемента И подключен к выходу переноса сумматора-вычитателя порядков, к первому входу десятого элемента Ник первому входу третьего элемента ИЛИ, выход которого соединен с.входом второго элемента НЕ, выход седьмого элемента И подключен к входу второго триггера переноса мантиссы, выходы первого и второго триггеров переноса мантиссы соединены соответственно с первым входом четвертого элемента ИЛИ и с вторым входом четвертого элемента ИЛИ, с входом четвертого элемента НЕ, выход которого подключен к первому входу одиннадцатого элемента И, выход которого соединен с входом триггера, преобразования, выход первого элемента НЕ соединен с первыми входами двенадцатого и тринадцатого элементов И, выход тринадцатого эле0

5

0

291

мента И соединен с вторьЕм входом вто рого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом четырнадцатого элемента И, выход которого подключен к входу триггера вьгчитания, выход которого соединен с вторым входом одиннадцатого элемента И и с первым входом дешифратора управляющих сигналов, второй, третий, четвертый и пятьш входы которого подключены к выходам четвертого элемента ИЛИ, триггера переполненияj дешифратора полутактов и триггера переноса порядка соответственно, шестой вход дешифратора управляющих сигналов под1 лючен к выходу регистра команд, выход счетчика полутактов подключен к входу дешифратора полутактов, первый и второй управляющие входы пятого коммутатора мантиссы соедине- |ны с выходами пятого и шестого элементов ИЛИ соответственно, первые входы которых подключены к выходам восьмого и девятого элементов И, соответственно, выходы двенадцатого элемента И и триггера преобразовани соединены соответственно с первым и вторым входами седьмого элемента ИЛИ, выход которого соединен с вторым входом сумматора по модулю два, выходы дешифратора управляюадах сигналов соединены соответственно с вторыми входами первого, второго и третьего элементов И, с первьш, вторым и третьим управляющими входами первого коммутатора порядка, с первым, вторым и третьим управляющими входами второго коммутатора порядка, с первым и вторым управляющими входами третьего коммутатора

порядка, с входами вычитания, сложения и переноса сумматора-вычита- теля порядков, с входами вычитания и переноса вычитатс ля порядковj с первым и вторым управляющими входами четвертого коммутатора порядка, с первым, вторым третьим и четвертым управляющими входами первого коммутатора мантиссы, с первым,вторым, третьим и четвертым управляющим входами второго коммутатора мантиссы, с вторым входом тринадцатого эле мента И и с входом вычитания сумма- тора-вычитателя мантисс, с входами сложения и переноса сумматора-вычи- тателя мантисс, с первым управляющим входом третьего коммутатора ман30

10

15

тиссы, с вторым управляющим входом третьего коммутатора мантиссы и с первым управляющим входом четвертого коммутатора мантиссы, с третьим управляющим входом третьего коммутатора мантиссы и с вторым управляющим входом четвертого коммутатора мантиссы, с третьим управляющим .входом четвертого коммутатора мантиссы, с третьим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с вторыми входами четьфнадцатого, двенадцатого,одиннадцатого, четвертого, седьмого и шестого элементов И, с входом вдвигаемого разряда первого сдвигатепя и с вторыми входами второго, третьего, пятого и шестого элементов ИЛИ и входом третьего элемента НЕ, с вторыми входами пятого, восьмого и 20 десятого элементов И и с третьими входами пятого и шестого элементов ИЛИ.

2, Устройство по п. 1, отличающееся тем, что узел норма5 лизации содержит группу элементов ИЛИ,, три элемента НЕ,, три элемента И, три элемента ИЛИ,; четыре шифратора и коммутатор, причем первый, второй, третий и четвертый информационные входы коммутатора соединены с информационными выходами первого, второго, третьего и четвертого шифраторов соответственно, первый управляющий вход ком1.1утатора соединен с выходом не-- равенства нулю первого пифратора и с входом первого элемента НЕ , второй управляющий вход коммутатора соединен с выходом первого элемента И и с первым входом первого элемента

0 ИЛИ, .третий управляющими вход коммутатора соедине.н с выходом второго элемента Икс первьгм входом второго элемента ШМ четвертый управля.ющий вход коммутатора соединен с вторыми

5 входами первого и второго элементов ИЛИ и с выходом третьего элемента И, первый вход которого подключен к в ыходу первого элемента НЕ и- к пер- вьм входам первого и второго эле50 ментов И второй вход третьего эле- мента И подключен к выходу второго элемента НЕ и к второму входу второго элемента И, третий и четвертый входы третьего элемента И подключены

55 к выходу третьего элемента НЕ и к выходу неравенства нулю четвертого шифратора соответственно, выходы неравенства нулю второго и третьего

0

5

1Ш1фраторов соединены с входом второго элемента НЕ, вторым входом первого элемента И и с входом третьего элемента НЕ, с третьим входом второго элемента И соответственно, входы с первого по патнадцатый элементов ИЛИ группы подключены к старшим разрядам входа узла нормализации, входы с шестнадцатого по тридцатьй элементов ИЛИ группы подключены к млад- юим разрядам входа узла нормализации выходы с первого по восьмой и с восемнадцатого по двадцать пятьм элементов ИЛИ группы соединены с соответствующими входами первого и треть го шифраторов соответственно, выходы с девятого по четырнадцатый элементов ИЖ группы соединены соответственно с входами с первого по шестой второго шифратора, выходы пят

надцатого и шестнадцатого элементов ИЛИ группы соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого подключен к седьмому входу второго шифратора, выход семнадцатого элемента i-UlPI группы соединен с восьмым входом второго шифратора, выходы с двадцать шестого, по тридцатый элементов ИЛИ группы соединены соответственно с входами с первого по пятый четвертого шифратора, выход неравенства нулю первого шифратора и выходы элементов И с первого по третий являются старшими разрядами выхода узла нормализации, выходы первого и второго элементов ИЛИ и выход коммутатора являются младшими разрядами выхода узла нормализации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для сложения и вычитания чисел с плавающей точкой | 1987 |

|

SU1481743A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

Изобретение относится к вычислительной технике и может быть использовано для работы в составе мультипроцессора быстродействующих ЭВМ. Цель изобретения - повышение быстродействия устройства, предназначенного для выполнения операций с плавающей точкой над числами короткого, длинного и расширенного форматов (за исключением операций умножения и деления) . Поставленная цель достигается тем, что в арифметическое устрой- ство, содержащее три триггера знака, триггер вычитания, три регистра порядка, четыре регистра мантиссы, три коммутатора порядка,, пять коммутаторов мантиссы, сумматор-вычитатель порядков, сумматор-вычитатель мантисс, узел нормализации, первый сдвигатель, счетчик полутактов, триггер переполнения мантиссы, триггер переноса порядка, регистр команд, элемент ИЛИ и шесть элементов И, введены второй сдвигатель, сумматор по модулю два, вычитатель порядков, четвертый и пятый коммутаторы порядка, дешифратор управляющих сигналов, дешифратор полутактов, два триггера переноса мантиссы, восемь элементов И, четьфе -элемента НЕ и шесть элементов ИЛИ. 1 з.п. ф-лы, 11 ил., 3 табл. с В (Л

7Т72

Начало

Приём 1-го и И-го операндоЙ Определение разности порядков П1-П2, П2-П1. nj - порядок операнда П2-порядок а-го Операнда Анализ действия для мантисс ВЧпр Jwv;© wV2®s, где Зн 41 - Man первого операнда Зн 42 знак, второю onefiatida ВЧ rip- Вычитание приведенное В - операция Вычитания

Сдвиг мантиссы Второго операнда

Порявак результата равен т

Сдвиг мантиссы первого операнда

Порявок овзуль- 1 тата равен П2

Фиг.З

вычитание ионтис

Анализ прео ралоЗания pfiy/ bmoma

мантиссы Пр

ПрН fJ-ВЧпр.

П- перенос CJ3 стари/его разрчда сумматора -Вычитотелр нонтисе fapMUpoaoHue знака резул -гпата нантиссы Зн Рез м,.

ЗнРез.М« ff-84np®3n I

наитие. Pop upefcнue 3fO- ко

MOHrtiUCCbt

Зн резм

3f, flejM JHVf

/ Переполнени /мантиссы

Да

ПреоЪразоВание мантлсы результата 8 /ippMou код

L

JJ

Х

1 ормализои:ия влево на К позиций. Уг еньшение порядков на К сдВигов.

L

С J

Сдвиг Впраоо нам- ну iuecmHa3nafrrepiN- нцю поз1Л4и/о промежуточного резд, та. Шеличение порядка на еЗимицу

Выдала реалмяютег

JJ

С

Начало

Прием знака и порядна

I-ZO и Л-го операндов.

Определение разности

порядков т-П2,П2-П1.

Анализ дейстВый для

мантисс.

В Чпр -ЗнШ®Знi/2e 8

Прием мантиссы 1-го операнда cmapujeu части

А и млади ей части а. Сдвиг AJ а вправо на

т-П2()

Запись pe3f/j bma/7ta со

сдвига „„ А,а

Прием мантиссы Его операнда старшей ти В и младшей частив. Сдвиг В,Ь Вправо на ПТ-П2{П2-П1)

}(ранение результата сдвига I го операнда

Прием младмвй части империи да в.

ФормироВан1 е слагаемы}

Сл1 . SS о Сл2 .- В

I

Фиг.

Запись pe3tiJ maii o cKuia М-ыоперанОа

вТ-

Приен nnaiKaeu час/пи Л-го операнЗа а.

Формирование слагаемы.

/

ФигЛ

г

у

К

Слтыние маннмхмлаО- шня частеа. 4% рмнда0А|м« трг/мяя Ь tanputsnj menu,.

вычианая миннисб млавинп Mtxwittf. Vef 4y oSanue мргтеа f emayiuytc «кяь.

де

Прием старшей части S-te огщюнЗа t cpi nMipa Ьатл елагаемык

СЛ1: - А CJfg: - В

пг

результата

6

чх

Фи.8

Ji

Сложение мантисс стар- iWi/x частей с учетом переноса 8 старшую часть. Формирование знака результата мантиссы Зн -ез.м Зн Рез М

Вычитание мантисс старики к частей с учетом переноса 8 старшую часть.

Анализ преобразования результата мантиссы ПрМ

Сддиг вправо на одну шестнадцатиричнун} по-- 3ift4UH) промежуточного результата.

ИВе.пичение породна на единицу

ПрМ П-ВЧпр.

Формирование знака результата Зн РезМ

Зн Рез Н П-вЧПР ФЗн ffr

V

Фиг. 9

ПреобразоУание мантиссы результата младшей части в прямоИ код.

I

преобразование мантиссы рез1}льтвта стар

шей юсти 8 прямой код

У

Определение к количеег етва сдВагоВ Влево, нормализаи ля резильта- та на К uiecmnaiKtfline- puttibfx позиций. Яменьиамл nopaftto на К сЗвиеав

Выдача стари/еи части результата

JP

г./0

Редактор О. Юрковецкая

Составитель А. Клюев Техред И Попович

Заказ 5122/46Тираж 671

ВНИИ1Ш Посударственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

flodzomoSffci млад и/ей части pestjJ bma- fna. Bbidava мл од и/ей части -езу.пьтата

Фиг.П

Корректор В. Бутяга

Подписное

| Арифметическое устройство | 1980 |

|

SU885993A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Регулятор для вертикальных ветряных двигателей | 1925 |

|

SU2060A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

Авторы

Даты

1986-09-23—Публикация

1985-03-21—Подача