С54) ИНТЕРПОЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Нелинейный интерполятор | 1984 |

|

SU1265809A1 |

| Интерполятор | 1978 |

|

SU765821A1 |

| Интерполятор | 1981 |

|

SU987634A1 |

| Линейный интерполятор | 1980 |

|

SU883925A1 |

| Интерполятор | 1981 |

|

SU991445A1 |

| Линейный интерполятор | 1982 |

|

SU1042038A1 |

| Генератор функций | 1980 |

|

SU962995A1 |

| Интерполятор | 1986 |

|

SU1345217A1 |

| Функциональный преобразователь | 1983 |

|

SU1145353A1 |

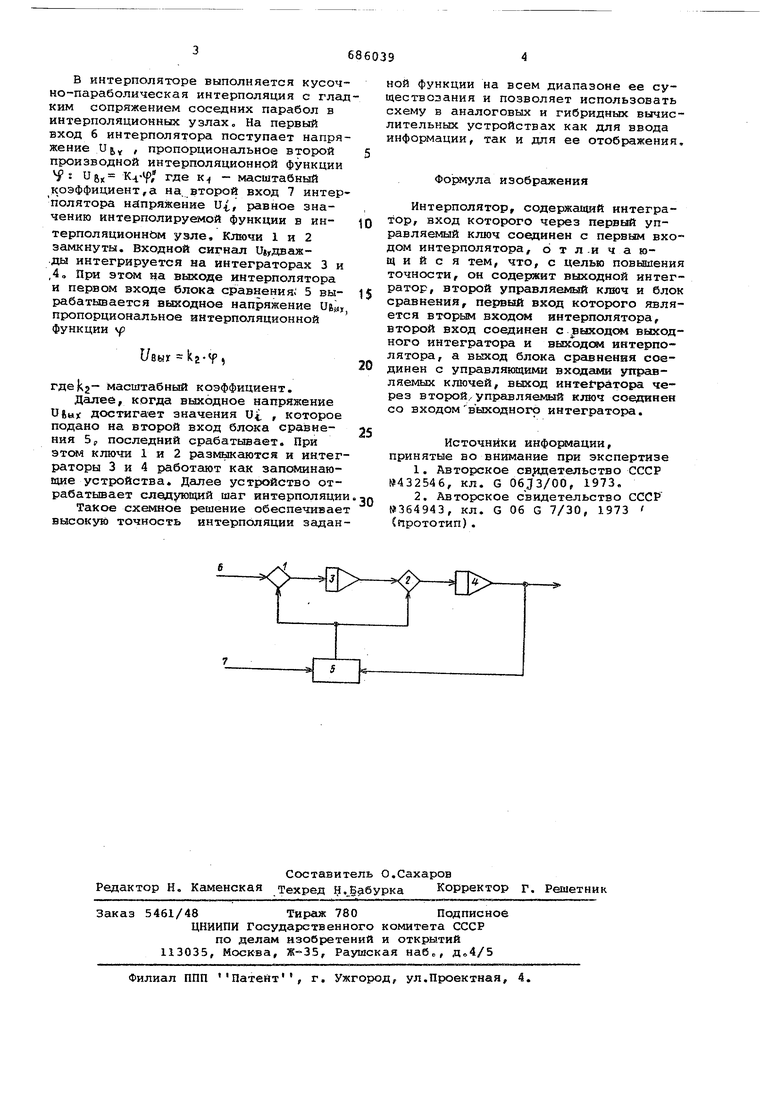

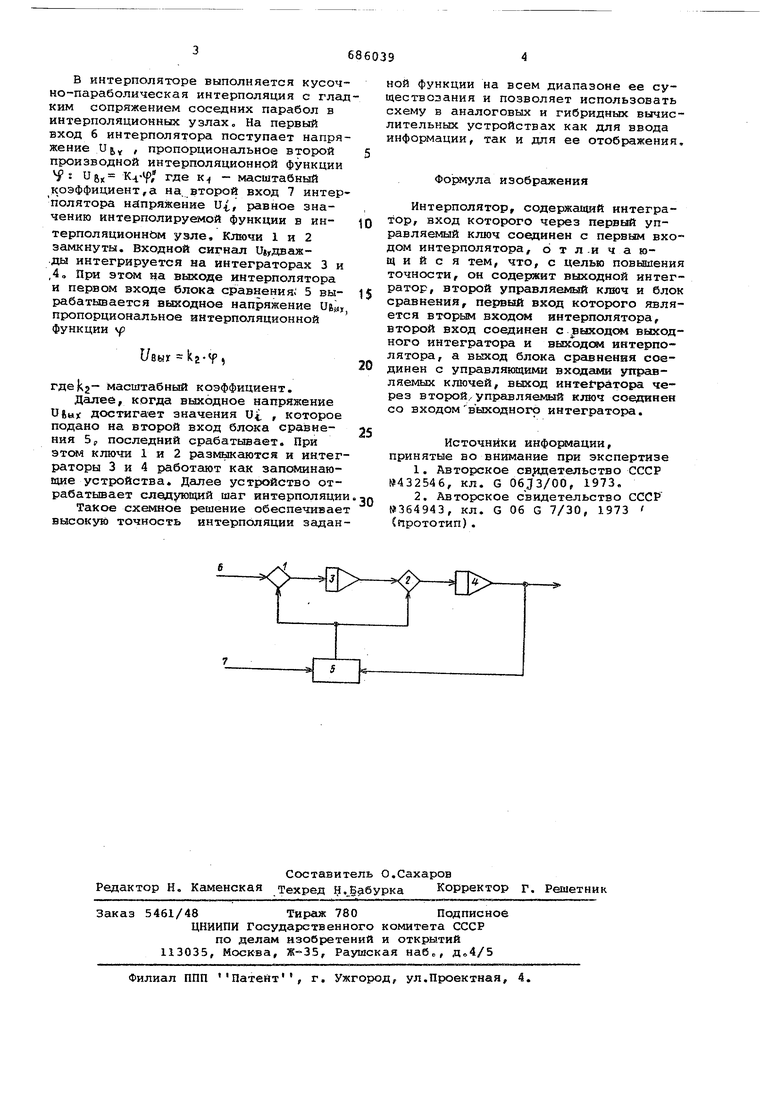

Изобретение относится к аналоговой и гибридной вычислительной технике. Известно устройство для интерполирования функций 1 по заданньш табличным значениям. Такое устройст во содержит цифроаналоговые блоки, цифроаналоговые преобразователи, бл вычисления полиномов и блок задержк Неяостатксяу1 такого интерполятора являются ограниченные функциональные возможности, так как в нем нет возможности прерывать процесс интерполяции и корректировать вид функции. Наиболее близким техническим решением к данному изобретению является интерполятор 2, который содержит сумматор, ключ, аналоговое запоминающее устройство и интегратор, соединенные последовательно, С выхода интегратора на второй вход сумматора заведена цепь обратной связи позволяющая корректировать значения функции в узлах интерполирювания. Однако вне узлов интерполирования функция воспроизводится недостаточно точно, так как она имеет кусочнолинейный вид. Кроме того это устройство не содержит элементов, обеспечивающих прерывание, которое необходимо для периодической коррекции входных данньк и запоминания функции в заданной точке. Целью изобретения является повышение точности. Поставленная цель достигается тем, что интеряюлятор, содержащий интегратор, вход которого через первый управляшллй KJD04. соединен с первым входсял интерполятора, дополнительно содержит выходной интегратор, второй управляемый ключ и блок сравнения, первый вход которого является вторьи входом интерполятора, второй вход соединен с выходе выходного интегратора и выходе интерполятора, а выход блока сравнения соединен с управляющими входами управляемых ключей, выход интегратора через второй управляемый ключ соединен со входом выходного интегратора. Схема предлагаемого интерполятора приведена на чертеже. Интерполятор содержит управляемые ключи 1 и 2, интегратор 3, выходной интегратор 4, блок сравнения 5. Первый вход интерполятора обозначен цифрой 6, второй - цифрой 7.

В интерполяторе выполняется кусочно-параболическая интерполяция с гладким сопряжением соседних парабол в интерполяционных узлах. На первый вход 6 интерполятора поступает напряжение и5, , пропорциональное второй производной интерполяционной функции f г U6x где к - масштабный коэффициент,а на, второй вход 7 интерполятора напряжение и., равное значению интерполируемой функции в интерполяционнЬм узле. Ключи 1 и 2 замкнуты. Входной сигнал и«,дважды интегрируется на интеграторах 3 и ,4, При этом на выходе интерполятора и первом входе блока сравнения. 5 вырабатывается выходное напряжение Ua, пропорциональное интерполяционной функции vf

1/выу l(,

где масштабный коэффициент.

Далее, когда выходное напряжение и&и)г достигает значения и. , которое подано на второй вход блока сравнения 5р последний срабатывает. При этсш ключи 1 и 2 размыкаются и интеграторы 3 и 4 работают как запслшнаюадие устройства. Далее устройство отрабатывает след(ующий шаг интерполяции

такое схемное решение обеспечивает высокую точность интерпелляции заданной функции на всем диапазоне ее существозания и позволяет использовать схему в аналоговых и гибридных вьлчислительных устройствах как для ввода информации, так и для ее отображения.

Фо:рмула изображения

Интерполятор, содержащий интегратор, вход которого через первый управляемый ключ соединен с первым вхо дом интерполятора, 6 т л .и ч а ющ и и с я тем, что, с целью повьндения точности, он содержит выходной интегратор, второй управляемый ключ и блок сравнения, первый вход которого является вторым входом интерполятора, второй вход соединен с выход 1 выходного интегратора и выхЪдс интерполятора, а выход блока сравненяя соединен с управляющими входами управляемых ключей, выход интегратора через второй,управляемый ключ соединен со входомвыходного интегратора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-09-15—Публикация

1978-04-17—Подача