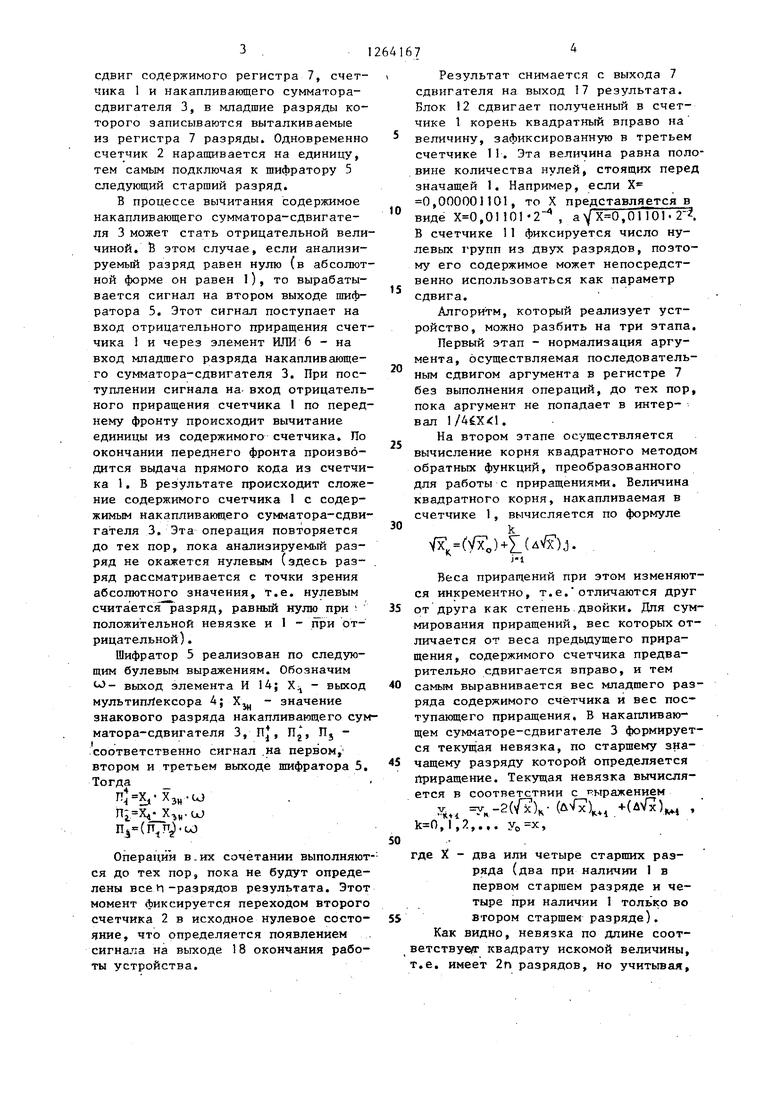

; . 7l Изобретение относится к вычислительной технике иможет быть использовано в вычислительных машинах. Цель изобретения - повышение быст родействия устройства за счет уменьшения числа суммирований. На чертеже показана структурная схема устройства. Устройство содержит первый счетчик 1, второй счетчик 2, накапливаюшлй сумматор-сдвигатель 3, мультиплексор 4, шифратор- 5, элемент ИЛИб, регистр 7, элемент 8 сравнения, триг гер 9, элемент И 10, третий счетчик 11, сдвигатель 12, элемент 2ИИЛИ 13, вход 14 аргумента, вход 15 .последовательного считывания, вход, 16 начальной установки устройства, выходы 17 результата и выход 18 приз нака окончания работы устройства. Устройство работает следующим образом. Аргумент, поступающий на вход 14, по сигналу с входа 16 С записывается в регистр 7, Одновременно этот сигнал сбрасывает в нуль счетчики П и триггер 9. Затем на вход 15 поступает серия сигналов С. Так как триг . гер 9 находится в нулевом состоянии, то сигнал с входа 15 через элемент 2И-ИЛИ 13 поступает на вход сдвига регистра 7. Старшие два разряда аргумента анализируются элементом .-8 сравнения. Если оба разряда нулевые, то сигнал появляется на выходе признака равенства нулю.элемента сравнения. Этот сигнал наращивает на 1 содержимое счетчика 11. Следующий сигнал повторяет указанную операцию. Это происходит до тех пор, пока хотя бы один из текущих двух разрядов не будет отличен от нуля. В этом случае сигналпоявляется на выходе призрака неравенства нулю эле мента сравнения, который перебрасывае триггер 9 в единичное состояние. Открывается элемент И 10, и сигнал с входа 15 поступает на шифратор 5. Так как второй счетчик 2 содержит нуль, входы мультиплексора отключены и на его выходе фиксируется состояние нуля. В соответствии с алгоритмом работы шифратора 5 сигнал появляется на его третьем, выходе. По это му сигналу происходит сдвиг содержимого накапливающего сумматора-сдвигателя 3 на два разряда с одновремен ной записью двух разрядов из регист17 ра 7 по последовательному информационному входу в два младших разряда сумматора-сдвигателя. Кроме того, происходит сдвиг содержимого первого счетчика 1 и увеличение содержимого второго счетчика 2 на единицу. Переход триггера 9 в единичное состояние блокирует элемент 8 сравнения. На этом текущая операция заканчивается , По следующему сигналу от второго, счетчика мультиплексор 4 пропускает содержимое второго разряда сумматора-сдвигателя 3 на вход пгафратора 5, Здесь возможны два случая ; значение предыдущих двух разрядов равно (Ol); значение предыдущих двух разрядов равно (Ю). В первом случае сигнал появляется на третьем выходе шифратора 5 и происходит сдвиг содержимого регистра 7, счетчика 1 и накапливающего сумматора-сдвигателя 3, в младшие освободившиеся разряды которого записьгеается следующие два разряда из регистра 7. Одновременно содержимое счетчика 2 увеличивается на 1, что приводит к подключению на следующем шаге к выходу мультиплексора 4 третьего разряда накапливающего сумматорасдвигателя 3,. Во втором случае на выходе мультиплексора 4 с}юрмируется единичный сигнал, что ведет к появлению сигнала на первом выходе шифратора 5. Этот сигнал поступает на вход положительного приращения счетчика 1 и через элемент ИЛИ 6 - на первый разряд накапливающего сумматора-сдвигателя 3. По сигналу, поступающему на вход положительного приращения первого счетчика 1, происходит вычитание содержимого счетчика 1 из содержимого накапливающего сумматорасдвигателя 3. По заднему фронту сигнала на входе положительного приращения счетчика 1 его содержимое увеличивается на 1. На этом операция заканчивается. По следукацему сигналу вновь анализируется разряд накапливающегося сумматора-сдвигателя 3,. Если он не нулевой, то повторяется операция вычитания И наращивание счетчика на единицу. Это продолжается до тех пор, пока анализируемый разряд не окажется нулевым. Если он нулевой, то вырабатывается сигнал на третьем выходе шифратора 5 и происходит

сдвиг содержимого регистра 7, счетчика 1 и накапливающего сумматорасдвигателя 3, в младшие разряды которого записываются выталкиваемые из регистра 7 разряды. Одновременно 2 наращивается на единицу, тем самым подключая к шифратору 5 следующий старший разряд,

В процессе вычитания содержимое накапливающего сумматора-сдвигателя 3 может стать отрицательной величиной. В этом случае, если анализируемый разряд равен нулю (в абсолютной форме он равен 1), то вырабатывается сигнал на втором выходе шифратора 5. Этот сигнал поступает на вход отрицательного приращения счетчика 1 и через элемент ИЛИ 6 - на вход младшего разряда накапливающего сумматора-сдвигателя 3. При поступлении сигнала на- вход отрицательного приращения счетчика 1 по переднему фронту происходит вычитание единицы из содержимого счетчика. По окончании переднего фронта производится выдача прямого кода из счетчика 1 . В результате происходит сложение содержимого счетчика 1 с содержимым накапливающего сумматора-сдвигателя 3. Эта операция повторяется до тех пор, пока анализируемый разряд не окажется нулевым (здесь разряд рассматривается с точки зрения абсолютного значения, т.е. нулевым счита ется азряд, равный нулю при положительной невязке и 1 - при отрицательной) .

Шифратор 5 реализован по следующим булевым выражениям. Обозначим W- выход элемента И 14; Х; - выход мультиплексора Д; Xj - значение знакового разряда накапливающего сум3, п;, п;, п, матора-сдвигателя

.1

.соответственно сигнал ,на первом, втором и третьем выходе шифратора 5. Тогда

Хзц -ю

,.и

n()

Операции в. их сочетании выполняют-ся до тех пор, пока не будут определены все и-разрядов результата. Этот момент фиксируется переходом второго счетчика 2 в исходное нулевое состояние, что определяется появлением . сигна.па на выходе 18 окончания работы устройства.

Результат снимается с выхода 7 сдвигателя на выход 17 результата. Блок 12 сдвигает полученный в счетчике 1 корень квадратный вправо на величину, зафиксированную в третьем счетчике 1I. Эта величина равна половине количества нулей, стоящих перед значащей 1, Например, если Х 0,000001101, то X представляется в виде ,ОП012 , ау ,оГ101. 24 В счетчике 11 фиксируется число нулевых групп из двух разрядов, поэтому его содержимое может непосредственно использоваться как параметр сдвига.

Алгоритм, который реализует устройство, можно разбить на три этапа.

Первый этап - нормализация аргумента, осуществляемая последовательным сдвигом аргумента в регистре 7 без выполнения операций, до тех пор, пока аргумент не попадает в интервал 1/44Х 1.

На втором этапе осуществляется вычисление корня квадратного методом обратных функций, преобразованного для работы с приращениями. Величина квадратного корня, накапливаемая в счетчике 1, вычисляется по формуле

Vx.№)+I()JJ-1

Веса приращений при этом изменяются инкрементно, т.е.отличаются друг

от друга как степень.двойки. Для суммирования приращений, вес которых отличается от веса предыдущего приращения, содержимого счетчика предварительно сдвигается вправо, и тем

самым выравнивается вес младшего разряда содержимого счё-тчика и вес поступающего приращения, В накапливающем сумматоре-сдвигателе 3 формируется текущая невязка, по старшему значащему разряду которой определяется Приращение, Текущая невязка вычисляется в соответствии с т ыpaжeниeм

у. y,-2(fk),-( /-(ANHJ), ,,l,.,.,. ,

где Х - два или четыре старших разряда (два при наличии 1 в первом старшем разряде и четыре при наличии 1 только во втором старшем разряде).

Как видно, невязка по длине соответствуед квадрату искомой величины, т.е. имеет 2п разрядов, но учитывая.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Вычислительное устройство | 1985 |

|

SU1260946A1 |

Изобретение относится к вычислительной технике и позволяет сократить время вычисления квадратного корня за счет уменьшения числа сумми-. рований. Устройство содержит счетчики 1, 2, W, накапаливающий сумматор-сдвиг атель 3, мультиплексор 4, шифратор 5, элемент ИЛИ 6, регистр 7, элемент 8 сравнения, триггер 9, элемент И 10, сдвигатель 12, элемент 2И-Ш1И 13, вход 14 аргумента, вход 15 последовательного считывания, вход 16 начальной установки устройства, выход 17 результата и выход 18 признака окончания работы устройства. Вычисление проводится в три этапа: норма- о лизация аргумента, вьиисление квад(Л ратного корня методом обратных функций, денормализация и выдача результата 1 ил.

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 0 |

|

SU362297A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР ,N«611208, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1125618A2 |

Авторы

Даты

1986-10-15—Публикация

1984-12-04—Подача