Изобретение относится к цифровой вычислительной технике и может быть использовано при построении преобразователей в координатных пультах ввода информации.

Известно устройство для .преобразования последовательного комбинированного кода в параллельный двоичный код, содержащее элементы И, счетчик, дешифраторы, контрольный счетчик, генератор иЛШульсов, выходы которого через элемент И соединены с входом счетчика и контрольнего счетчика, а выходы счетчика соединены с входами дешифратора 1 ,

Недостаток известного устройства - ограниченные функциональные воможности, поскольку оно не вырабатывает систем импульсов синхронизации для сопряженного устройства.

Наиболее близким по технической сущности к предлагаемому является устройство для преобразования последовательного комбинированного кода в параллельный двоичный код, содержащее регистры, элемент И, контрольный счетчик, дешифраторы, генератор импульсов, первый и второй выходы которого подключены соответственно к счетному входу счетчика и управляющему входу первого дешифратора, первые, вторые, третьи выходы счетчика подключены соответственно к входам первого, второг третьего дешифраторов, первые выходы которых подключены к входам первого элемента И, выход которого подключен к входам установки нуля первого, второго, третьего регистров и контрольного счетчика. 2.

Однако такое устройство имеет никую надежность преобразования, так как на его выходах фор шруется двоичный код только для одной координаты, и не имеет возможности вырабатывать опросные импульсы для источника последовательного кода, что затрудняет синхронизацию информационных Сигналов.

Цель изобретения - расширение функциональных возможностей за счет возможности реализации преобразования двухкоординатного последовательного комбинированного кода.

Поставленная цель достигается тем, что в преобразователь посл овательного комбинированного кода в параллельный двоичный код, содержащий первый, второй и третий регисры, контрольный счетчик, первый элемент И, первый, второй и третий дешифраторы, счетчик и генератор импульсов, Первый и второй выходы которого подключены соответственно к счетному входу счетчика и управляющему входу первого дешифратора, первая, вторая, третья группы выход:1ов счетчика подключены соответственно к группам входов первого , второго, третьего дешифраторов, первые выходы которых подключены к входам первого элемента И, выход которого подключен к входам установки нуля первого, второго, третьего регистров и контрольного счетчика, введены KoivtMyTaTop, второй элемент 1|, первый и второй элементы сравнения и четвертый дешифратор, выход которого подключен к управляющему входу третьего дешифратора и первому входу второго элемента И, второй вход которого подключен к второму выходу первого дешифратора, третий выход .которого и выход второго элемента И являются соответственно прямым и инверсным управляющими В1лходами преобразователя, информационный вход которого подключен к входу коммутатора управляющие входы которого подключены к выходам третьего дешифратора, а первый, второй, третий выходы коммутатора подключены соответственно к входам синхронизации первого, второго, третьего регистров, группа информационных входов первого регистра соединена соответственно с группой выходов второго дешифратора, вторая группа выходов счетчика соединена с группами информационных входов второго и третьего регистров, четвертая группа выходов счетчика соединена с группой входов четвертого дешифратора, выходы первого и второго разрядов первого регистра соединены с входами первого элемента сравнения, выход которого, выход первого разряда первого регистра, группа выходов второго регистра являются выходами первой координаты преобразователя, выходом ошибки преобразования является выход контрольного счетчика, счетный вход контрольного счетчика соединен с четвертым выходом коммутатора, выходы третьего и четвертого разрядов первого регистра соединены с входами второго элемента сравнения выход которого совместно с выходом третьего разряда первого регистра и группой выходов третьего являются выходами второй коор-. динаты преобразователя.

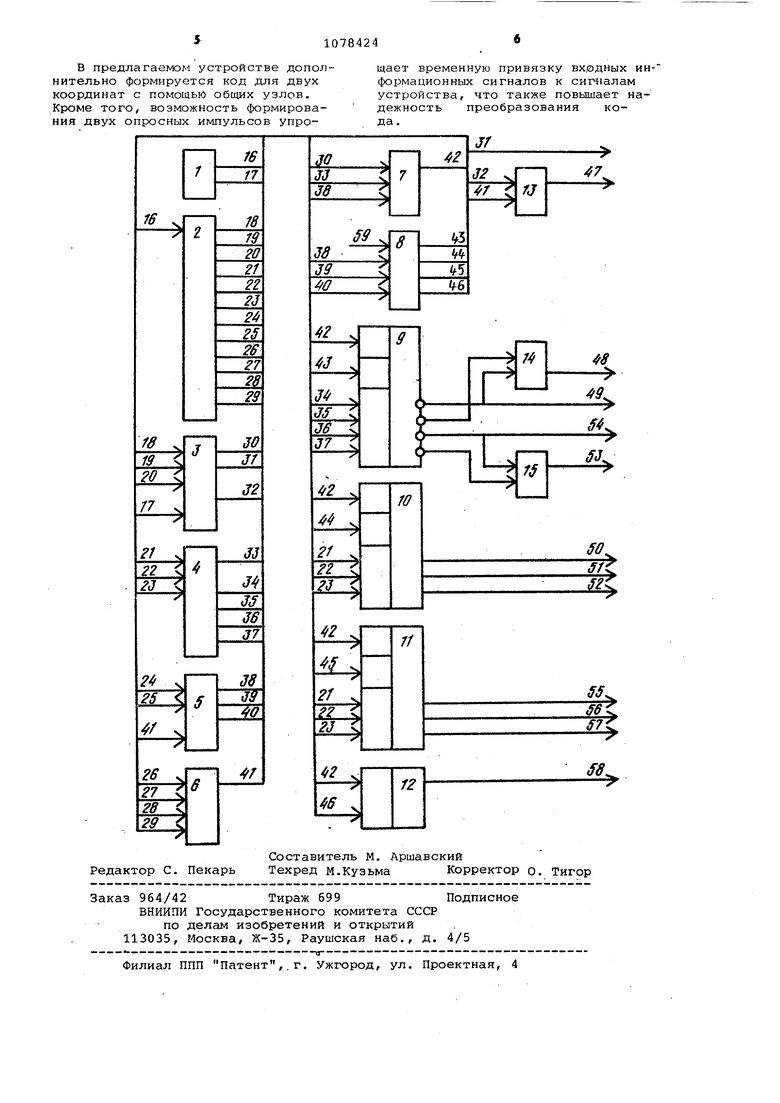

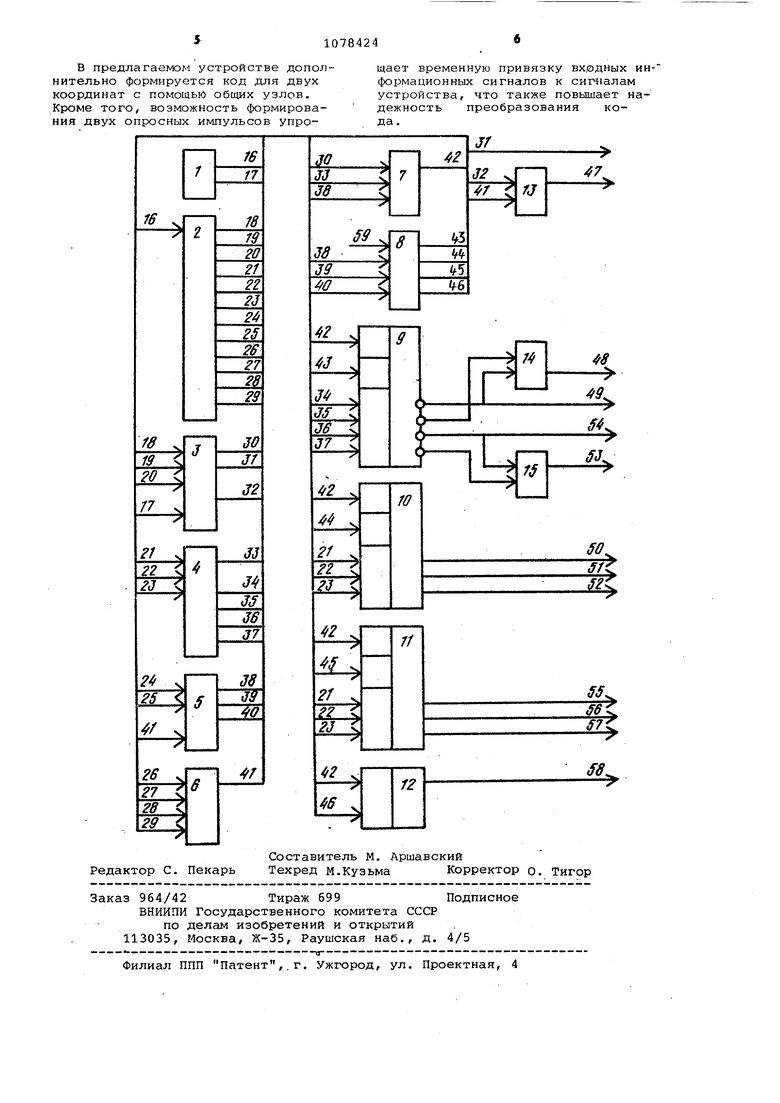

На чертеже приведена блок-схема предлагаемого преобразователя.

В состав преобразователя входят генератор 1 импульсов, счетчик 2, первый, второй, третий, четвертый дешифраторы 3-6, первый элемент И коммутатор 8, первый, второй, третий регистры 9-11, контрольный .счетчик 12, второй элемент И 13, |первый и второй элементы 14 и 15 сравнения. Позициями 16-46 обозначе ны выходы и входы преобразователя: 47-58 - выходьл ггреобразователя, 59 - информационный вход преобразователя . Вход 16 является счетным входом счетчика 2, а входы 17 и 41 - управ ляющими входами дешифраторов 3 и 5 соответственно. Выход 42 элемента И 7 соединен с входами сброса регистров 9-11 и контрольного счетчи|ка 12. Выходы 43-45 коммутатора сое динены с входами синхронизации регистров 9-11, а выход 46 коммутатора соединен со счетным входом контрольного счетчика 12. Выходы 31 и 47 являются управляющими вы одами преобразователя, выходы 48-52 и 53являются соответственно выходами первой и второй координаты преобразователя. Преобразователь работает следующим образом. Дешифраторы 3 и 4 работают непре рывно, а дешифратор 5 работает толь ко при наличии сигнала на вьаходе 4 дешифратора 6. Непрерывная работа ,счетчика 2 вызывает циклическую работу всего устройства. В начале каждого цикла работы появляются сигналы на выходах 30, 33, 38 и 41 дешифраторов 3-6, а вырабатываемый при этом на выходе 42 элемента И 7 сигнал производит установку в О регистров 9-11 и контрольного счетчика 12. После этого на входе 59 в результате воздействия опросных -. сигналов на выходах 31 и 47 устройства Появляются сигналы двух пос .ледовательных комбинированных кодов по числу координат. Комбинированный код составлен из 2 -разрядного и унитарного кодов. Кодовые комбина ции О и 1 2 -разрядного кода при в порядке возрастания имеют вид: 1000, 1100, 1110, 1111, 0111, ООН, 0001, 0000. Соответствующие им комбинации обычного двоичного кода имеют вид: 000, 001, 010, 01 100, 101, 110, 111. При п 2 разрядный код имеет избыточные комбинации, а их наличие является признаком неправильного считывания информации. При п 1 комбинации 2 -разрядного кода имеют вид: 10, 11, 01, 00, а соответствующие им комбинации в обычном двоичном коде имеют вид: 00, 01, 10, 11. Код левого разряда кодовых комбинаций 2 -ра зря дно го кода поступает на вход 59 первым, для приведенного на чертеже примера реализации преобразователя п равно 1. 2 -разрядный код преобразуется в код младших разрядов. Код старших разрядов на выходе преобразователя получается при преобразовании унитарного кода, комбинации которого имеют вид: 10000000, 01000000, 00100000, 00010000, 00001000, 00000100, 00000010, 00000001. Соответствующие им комбинации обычного двоичного кода имеют вид: ООО, 001, 010, 011, 100, 101, 110, 111. Остальные комбинации унитарного кода являются избыточными и появля|ются только при неправильном считывании информации. Код левого разряда кодовых комбинаций унитарного j кода поступает на вход 59 также первым.. В момент действия импульсов на выходе 38 дешифратора 5 и выходах 34 и 35 дешифратора 4 на вход 59 поступает разрядный код X, его единичные сигналы проходят через коммутатор Вис его выхода 43 воздействуют на вход синхронизации регистра 9, пропуская в первые два триггера код с выходов 34 и 35 дешифратора 4. В момент действия импульсов на выходе 38 дешифратора и выходах 36 и 37 дешифратора 4 на вход 59 поступает 2 -разрядный ко его единичные сигналы также появляются на выходе 43 коммутатора 8, но пропускают в третий и четвертый триггеры регистра 9 код с выходов 36 и 37 дешифратора 4. В момент действия импульса на выходе 39 дешифратора 5 на вход 59 поступает унитарный код X, его единичный сигнал проходит через коммутатор Вис его выхода 44 воздействует на вход синхронизации регистра 10, пропуская в него соответствующий код с выходов 21, 22 и 23 счетчика 2. В момент действия импульса на выходе 40 дешифратора 5 на вход 59 поступает унитарный код У, его единичный сигнал проходит через коммутатор Вис его выхода 45 поступает на вход синхронизации регистра 11, пропуская в него соответствующий код с выходов 21, 22 и 23 счетчика 2. Единичные сигналы обоих унитарных кодов с выхода 46 коммутатора 8 поступают на счетный вход ,кЬнтрольного счетчика 12. При правильном преобразовании код на его выходе принимает значение, соответствующее числу 2. Сигнал на выходе 58 используется для подтверждения достоверности информации. К выходу 58 может быть подключен элемент индикации. . Введение в предлагаемое устройство новых узлов и связей приводит по сравнению с известным устройством к повышению надежности преобразова- ния кода и расширению функциональных возможностей.

В предлагаемом устройстве дополнительно формируется код для двух координат с помощью общих узлов. Кроме того, возможность формирования двух опросных импульсов упрощает временную привязку вх.одных информационных сигналов к сигналам устройства, что также повышает надежность преобразования кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования последовательного комбинированного кода в параллельный двоичный код | 1976 |

|

SU613319A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1208582A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Устройство для ввода графичес-КОй иНфОРМАции | 1979 |

|

SU798916A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1089624A1 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1049966A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Устройство для ввода информации | 1979 |

|

SU798913A1 |

ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОМБИНИРОВАННОГО КОДА В ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ КОД, содержащий первый, второй и третий регистры, контрольный счетчик, первый элемент И, первый, второй и третий дешифраторы, счетчик и генератор импульсов, первый и второй выходы которого подключены соответственно к счетному входу счетчика и управляющему входу первого дешифратора, первая, вторая, третья группы выходов счетчика подключены соответственно к группаь5 входов первого, второго и третьего дешифраторов, первые выходы которых под-, ключены к входам первого элемента И, выход которого подключен к входам установки нуля первого, второго, третьего регистров и контрольного счетчика, отличающийся тем, что, с целью расширения функциональных возможностей за счет возможности реализации преобразования двухкоординатного последовательного комбинированного кода, в него введены коммутатор, второй элемент И первый и второй элементы сравнения и четвертый дешифратор, выход которого подключен к управляющему входу третьего дешифратора и первому входу второго элемента И, второй вход которого подключен к второму выходу первого дешифратора, третий выход которого и выход второго элемента И являются соответственно прямь м и инверсным управляющими выходами преобразователя, информационный вход которого подключен к входу коммутатора, управляющие входы которого подключены к выходам третьего дешифратора, а первый, второй, третий выходы коммутатора подключены соответственно к входам синхронизации первого, второго и третьего регистров, группа информационных входов первого регистра соединена с группой выходов второго дешифратора, вторая группа выходов счетчика соединена с груп(Л пами информационных входов второго и третьего регистров, четвертая группа вььчодов счетчика соединена с группой входов четвертого дешифратора, выходы первого и второго разрядов первого регистра соединены с входами первого элемента сравнения, выход которого, выход перво-4j го разряда первого регистра, группа выходов второго регистра явэо ляются выходами первой координаты 4: преобразователя, выход контрольного счетчика является выходом ю ошибки преобразователя, счетнЫй 4 вход контрольного счетчика срединен с четвертым выходом коммутатора, выходы третьего и четвертого разрядов первого регистра соединены с входами второго элемента сравнения, выход которого, выход третьего разряда первого регистра и группа выходов третьего регистра являются выходами вто-. рой координаты преобразователя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ГРАФИЧЕСКОР ИНФОРМАЦИИВСЕСОЮЗНАЯ | 0 |

|

SU326606A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для преобразования последовательного комбинированного кода в параллельный двоичный код | 1976 |

|

SU613319A1 |

Авторы

Даты

1984-03-07—Публикация

1982-12-27—Подача