1

Изобретение касается электросвязи и может использоваться в системах передачи данных методом фазовой манипуляции .

Известно устройство для устранения- обратной работы в системах передачи дискретных сообщений с фазовой .манипуляцией, содержащее блок памяти, коммутатор и элемент НЕ, а в каждом блоке преобразования . сигнала - элемент И и реристр сдвига, причем сигнальный вход регистра сдвига одного блока преобразования сигнала соединен со входом элемента НЕ, выход которого подключен к сигнальному входу регистра сдвига другого блока преобразования сигнала, а тактовые входы регистров сдвига объединены flj .

Однако помехоустойчивость такого устройства невелика.

Цель изобретения - повьпиение помехоустойчивости устройства.

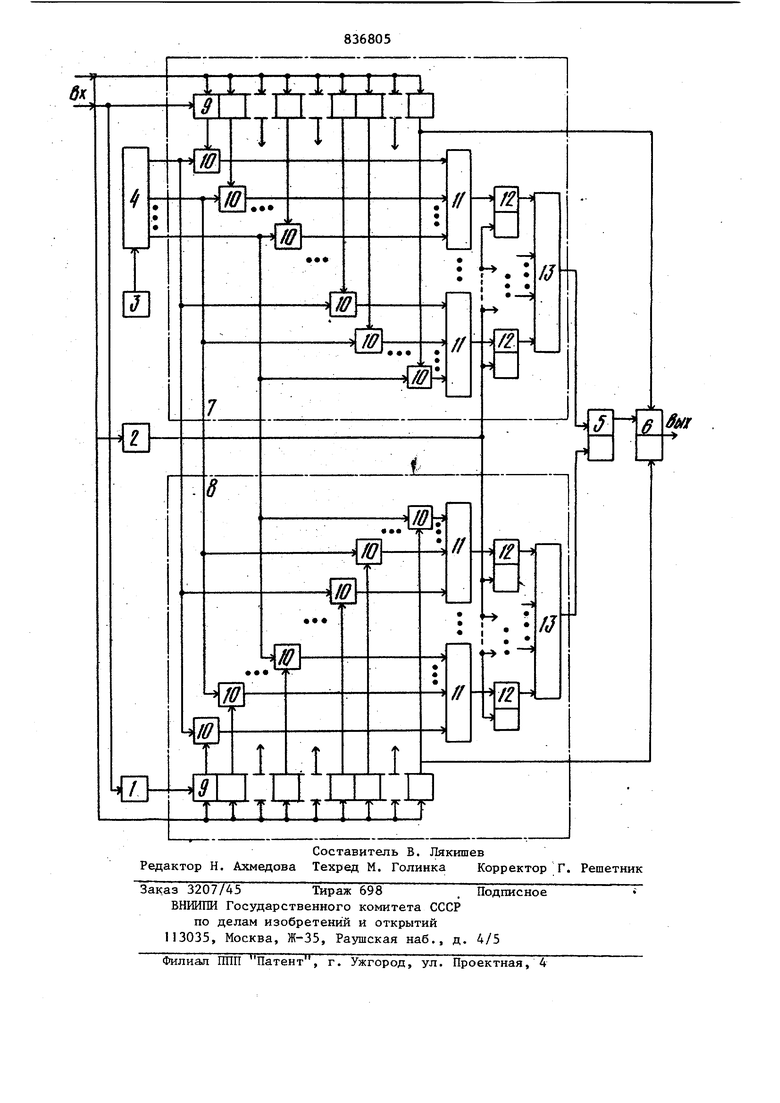

. Для этого в устройство для устранения, обратной работы в системах передачи дискретных сообщений с фазовой манипуляцией, содержащее блок памяти, коммутатор и элемент НЕ, а в каждом блоке преобразования сигнала - элемент И и регистр сдвига, причем сигнальный вход регистра сдвига одного блока преобразования сигнала соединен со входом элемента НЕ, выход которого подключен к сигнальному входу регистра сдвига другого блока преобразования сигнала, а тактовые входа регистров сдвига объединены, введены блок управления, формирователь импульсов и управляющий триггер, а в каждый блок преобразования сигнала - элементы ИЛИ-НЕ, триггеры и сумматоры, выходы которых подключены ко входам элементов ИЛЙ-НЕ, выходы которых соединены с первыми входами соответствующих триггеров, выходы которых подключены, ко входам элемента И, ыход которого соединен с со3ответствующим входом управляющего триггера, выход которого подключен к управляющему входу коммутатора, си нальный вход которого соединен с одним из выходов регистра сдвига, другие выходы которого подключены к пер вым входам соответствующих сумматоров, вторые входы которых соединены с выходами блока памяти, ко входу которого подключен выход блока управ ления, при этом тактовые входы регистров сдвига соединены со входом формирователя импульсов, выход которого подключен ко вторым входам соответствующих триггеров. На чертеже представлена структурная электрическая схема описываемого устройства. Устройство для устранения обратной работы содержит элемент НЕ 1, формирователь 2 импульсов, блок 3 уп равления, блок 4 памяти, управляющий триггер 5, коммутатор 6, блоки 7 и 8 преобразования сигнала, каждый из которых содержит регистр 9 сдвига, сумматоры 10, элементы ИЛИ-НЕ 11, триггеры 12, элементы И 13. Устройство работает следующим образом. При отсутствии обратной работы двоичные элементы информации со входа устройства поступают в регистр 9 сдвига блока 7 преобразования сигнала в прямом коде, а в регистр 9 сдви га блока 8 - в инверсном вследствие их инвертирования элементом НЕ 1. При этом каждый блок 7 и 8 преобразо вания сигнала производит обнаружение сигнала в прямом коде и работает сле дующим образом. Поступающие с регистра 9 сдвига viGl элементов информации в параллель ном коде непрерывно сравниваются на сумматорах 10 с соответствующими раз рядами кодовых слов, поступающих последовательно в параллельном коде с блока 4 памяти. При этом непрерыв.ное периодическое считывание кодовых слов из блока 4 памяти, обесп чиваемое блоком 3 управления, производится с частотой , превьщгающей частоту Г следования импульсов тактово синхронизации регистров 9 сдвига более, чем в m раз, т.е. , где m - общее число разрешенных кодовых комбинаций принимаемого кода, записанных в блоке 4 . ТаКИМ образом, за каждый тактовый ин5тервал регистров сдвига на вторые входы каждых 3 сумматоров 10, соответствующих разрядным выходам регистра 9 сдвига с номерами, определяемыми вьфажением j-f kn (где j - по- рядковый номер группы из Q сумматоров, ,1,...,и-1 при каждом j), последовательно подается соответствующий j -ый разряд каждого кодового слова блока 4 памяти. При поэлементном совпадении какого-либо п .-разрядного кодового слова (одного из 3) регистра сдвига с одним из кодовых слов блока 4 памяти на соответствующих и сумматорах 10, на входе соответствующего элемента ИЛИ-НЕ 11 появится сигнал, который установит соответствующий триггер 12 в единичное состояние. При установке всех триггеров в единичное состояние в течение тактового интервала, что возможно только при накоплении в регистре 9 сдвига Q правильно принятых в прямом коде м -разрядных слов принимаемой информации, на выходе элемента И 13 появится сигнал, кототорый установит управляющий триггер 5 в такое состояние, при котором коммутатор 6 подключит на выход устройства последний разрядный выход регистра 9 сдвига рассматриваемого блока. Таким образом, при отсутствии обратной работы установка управляющего триггера 5 будет производиться вы-. ходным сигналом блока 7 преобразования сигнала и на выход устройства будет подключен последний разрядный выход регистра сдвига этого блока. В начале каждого тактового интервала производится сброс всех триггеров 12 обоих блоков в нулевое состояние выходным импульсом формирователя 2 импульсов. Формирователь 2 импульсов по каждому переднему фронту тактовых импульсов формирует импульс, длительность Т которого определяется следующим соотношением где :-сч . т - длительность элементарной посылки; Tj,- пери.од считывания кодовых слов из блока 4 памяти; m - общее число разрещенных кодовых слов принимаемого кода, записанных в блоке 4 памяти; минимальная длительность импульса, необходимая для надежной установки триггеров запоминания в нулевое состояние. 5 Это необходимо для того, чтобы по окончании действия импульса форми рователя 2 импульсов каждая кодовая комбинация блока памяти хотя бы один раз поступила в блоки 7 и 8 до начала следующего тактового интервала. При возникновении обратной работы сигналы на переключение управляющего триггера 5 не будут поступать до тех пор, пока все разряды регистра 9 сдвига блока 8 не заполнятся вторично инвертированными элементами инфор ма.ц«и. За это зремяпО элементов информации в прямом коде, оставшиеся в регистре 9 сдвига блока 7, будут последовательно подаваться на выход устройства. Как только все разряды регистра 9 сдвига блока 8 заполнятся вторично инвертированными элементами информации и произойдет обнаружение прямого кода этим блоком, управляющий триггер 5 опрокинется, и коммут тор 6 подключит на выход устройства последний разрядный выход регистра 9 сдвига блока 8. При самоустранении обратной работы, когда на вход устройства вновь будет поступать информация в прямом коде, сигнал на переключение управляющего триггера 5 будет снова поступать с блока 7 после того, как разряды его регистра 9 сдвига заполнятся информацией в прямом коде. За это время, аналогично рассмотренному случаю, оставшиеся vnQ элементов информации в прямом коде в регистре 9 сдвига блока 8 будут подаваться на выход устройства. В результате, если кодовые комбинации не были искажены помехами, то в среднем устранение обратной работы будет производиться за время приема п/2 посылок информа ции, т.е. в данном случае увеличение длины (разрядности) регистров 9 сдви .га, с целью повышения устойчивости блоков 7 и 8 от ложного срабатывания на время устранения обратной работы влияния не оказывает. Устойчивость блока 7 или 8 от. ложного срабатывания характеризуется вероятностью ложного срабатывания Рд и определяется величиной QL , которая в свою очередь определяет разрядность регистра 9 сдвига, количество сумматоров 10, элементов ИЛИ-НЕ 11, триггеров 12 и число входов элемента И 13, т.е. структуру блока. 5 Полагая, что все кодовые комбинации, .поступающие с каждым тактом на сумматоры 10 блока, принимающего информацию в инверсном коде, равновероятны, а также, полагая, что искажение двоичного элемента 1 или О является независимым и равновероятным событием, то вероятность ложного срабатывания Рд блока будет, определяться выражением ), где vri - общее число разрешенных кодовых слов, записанных в блоке 4 памяти; п - разрядность кода. Из приведенного Bbmie выражения величина Q определяется в следующем виде НЛ/2% -Ч где 3 означают операцию округления до ближайшего целого числа. При -известных значениях тип величину Q выбирают из требуемой вероятности ложного срабатывания Рд блоков 7 и 8, чем обеспечивается требуемая помехоустойчивость устройства. Блок4 памяти позволяет производить перезапись алфавита кодовых комбинаций принимаемого кода и тем самым обеспечить работоспособность устройства при приеме любого н- разрядного корректирующего кода при соответствующем выборе структуры блоков 7 и 8. При этом работа устройства не зависит от помехоустойчивости системы цикловой синхронизации, которая в данном устройстве исключена, и устранение обратной работы в принимаемом сигнале может производиться при любой скорости передачи данных. Формула изобретения Устройство для устранения обратой работы в системах передачи дискетных сообщений с фазовой манипуляией, содержащее блок памяти, коммуатор и элемент ПЕ, а в каждом блоке реобразования сигнала - элемент И регистр сдвига, причем сигнальный ход регистра сдвига одного блока реобразования сигнала соединен со входом элемента НЕ, выход которого подключен к сигнальному входу регист ра сдвига другого блока преобразования сигнала, а тактовые входы регист ров сдвига объединены, отлича ющееся тем, что, с целью повышения помехоустойчивости , введены блок управления, формирователь импульсов и управлякиций триггер, а в каждый блок преобразования сигнала элементы ИЛИ-НЕ, триггеры и сумматоры, выходы которых подключены ко вхо дам элементов ШШ-НЕ, выходы которых соединены с первыми входами соответствующих триггеров, выходы которых подключены ко входам элемента И, выход которого соединен с соответствую щим входом управляющего триггера, выход которого подключен к управляю 58щему входу коммутатора, сигнальный вход которого соединен с одним из выходов регистра сдвига, другие выходы которого подключены к первым входам соответствующих сумматоров, вторые входы которых соединены с выходами блока памяти, ко входу которого подключен выход блока управле1шя, при этом тактовые входы регистров сдвига соединены со входом формирователя импульсов, выход которого подключен ко вторым входам соответствующих триггеров. Источники информации, принятые во внимание при экспертизе 1. Мартынов Е.М. Синхронизация . в системах передачи секретных сообщений. М., Связь, 1972, с.182-184.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для регенерации биимпульсных сигналов | 1989 |

|

SU1688413A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство для синхронизации по циклам | 1983 |

|

SU1172052A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство для приема сигналов относительной фазовой телеграфии | 1983 |

|

SU1138954A1 |

| Устройство для исправления отказов линейных преобразователей кодов | 1989 |

|

SU1702531A1 |

Авторы

Даты

1981-06-07—Публикация

1979-07-17—Подача