1

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах, процессоры которых имеют более высокое быстродействие, чем память, с которой они непосредственно взаимодействуют.

Цель изобретения - повышение быстродействия работы устройства.

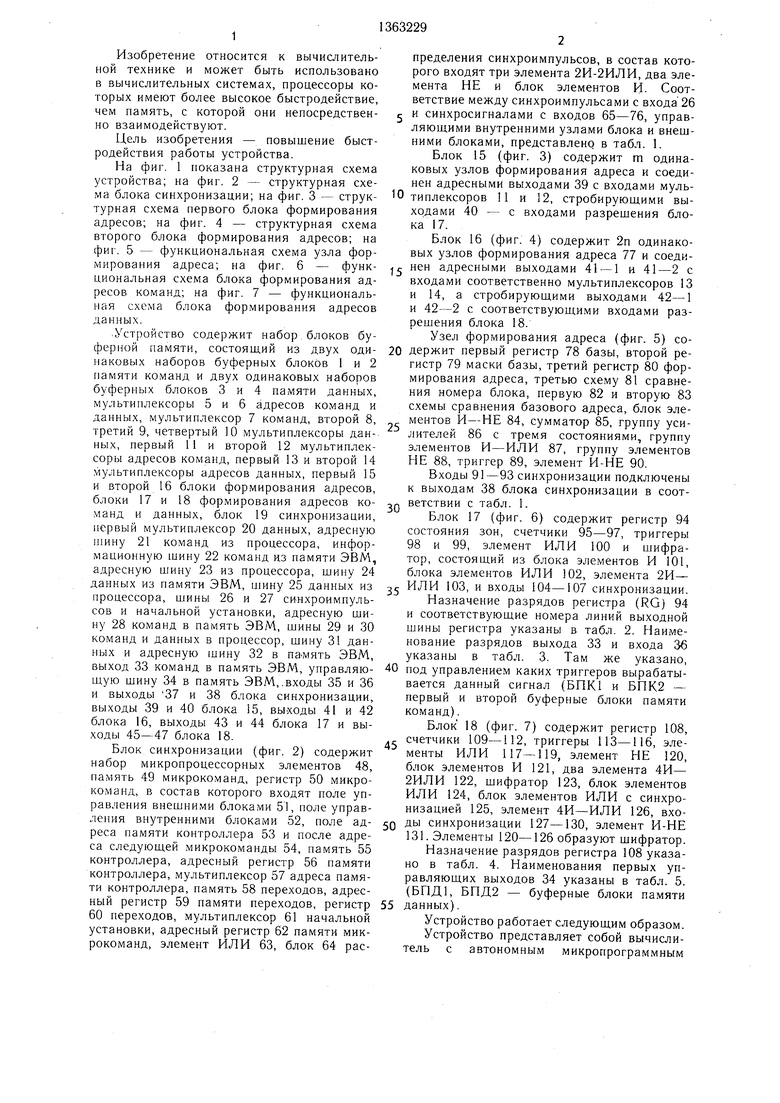

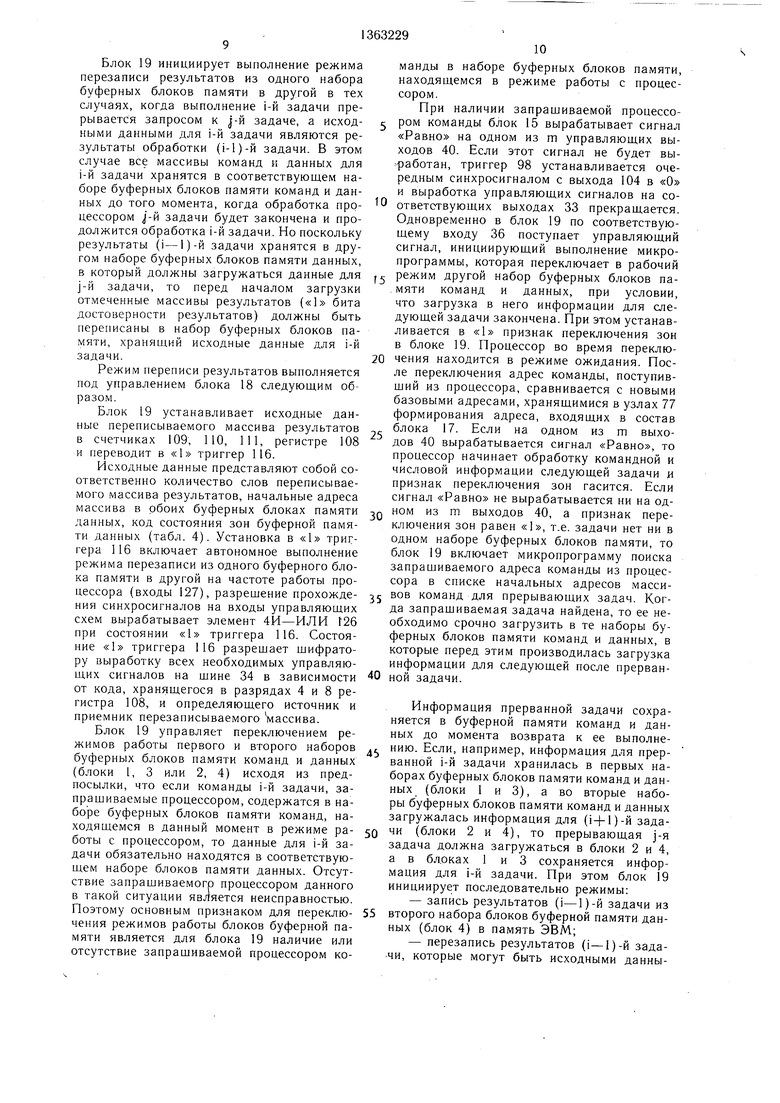

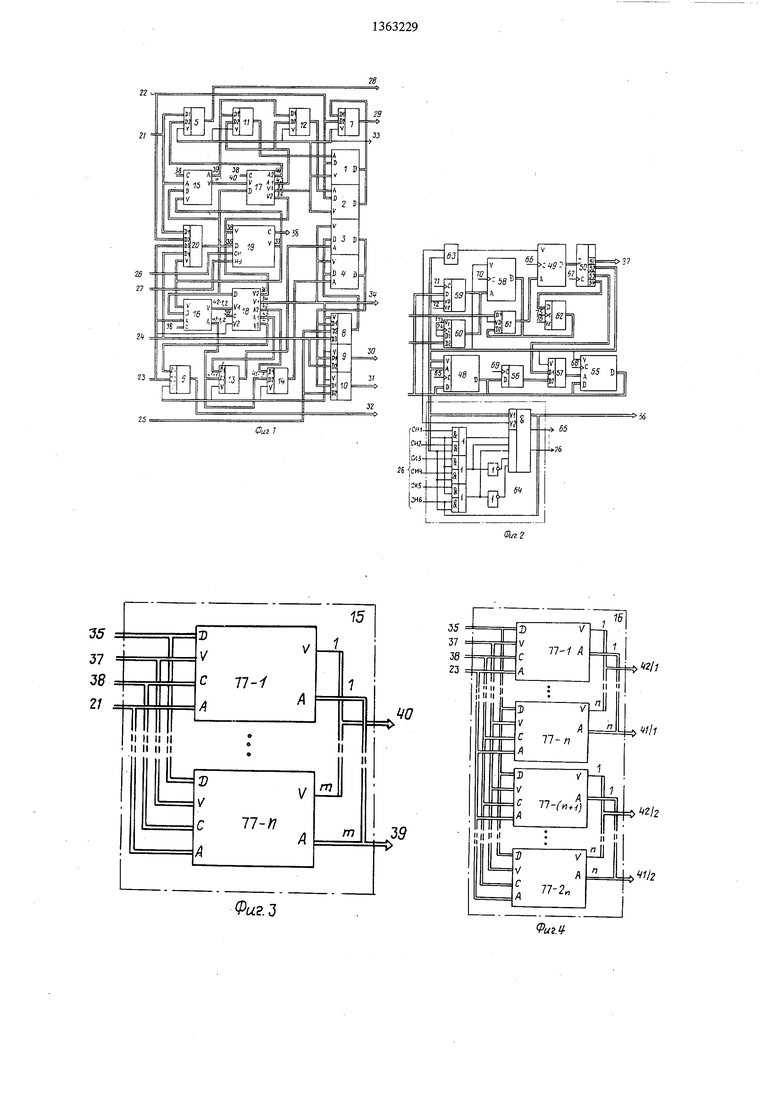

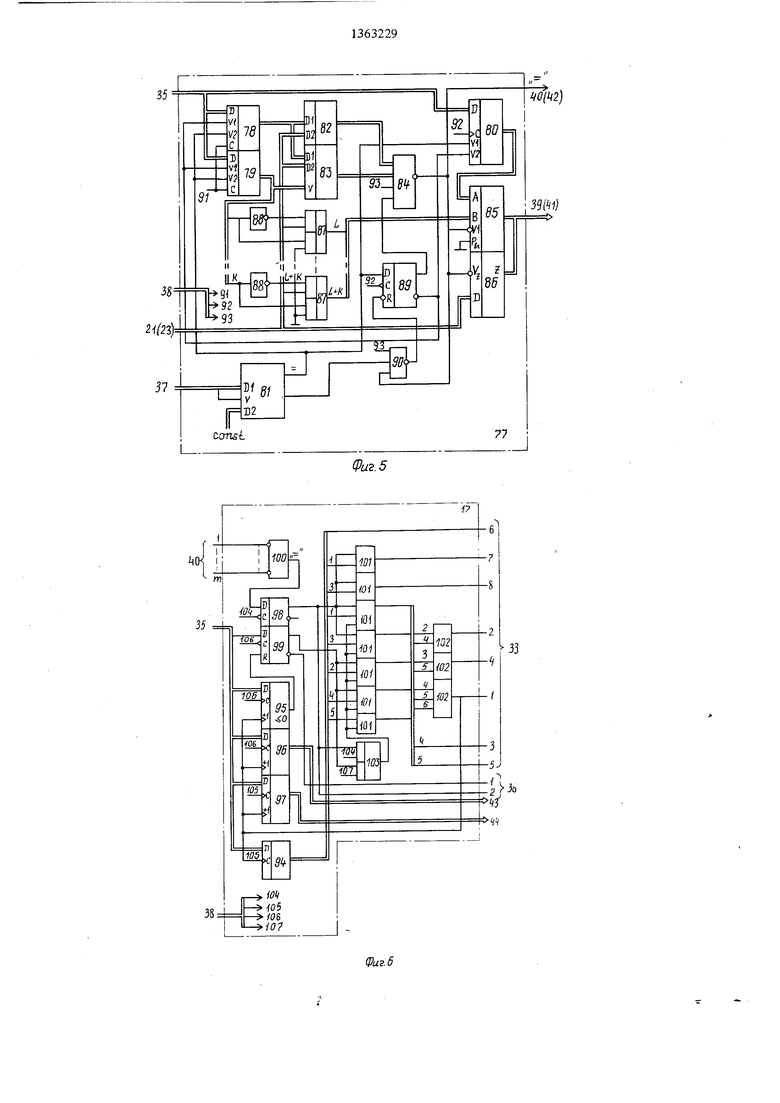

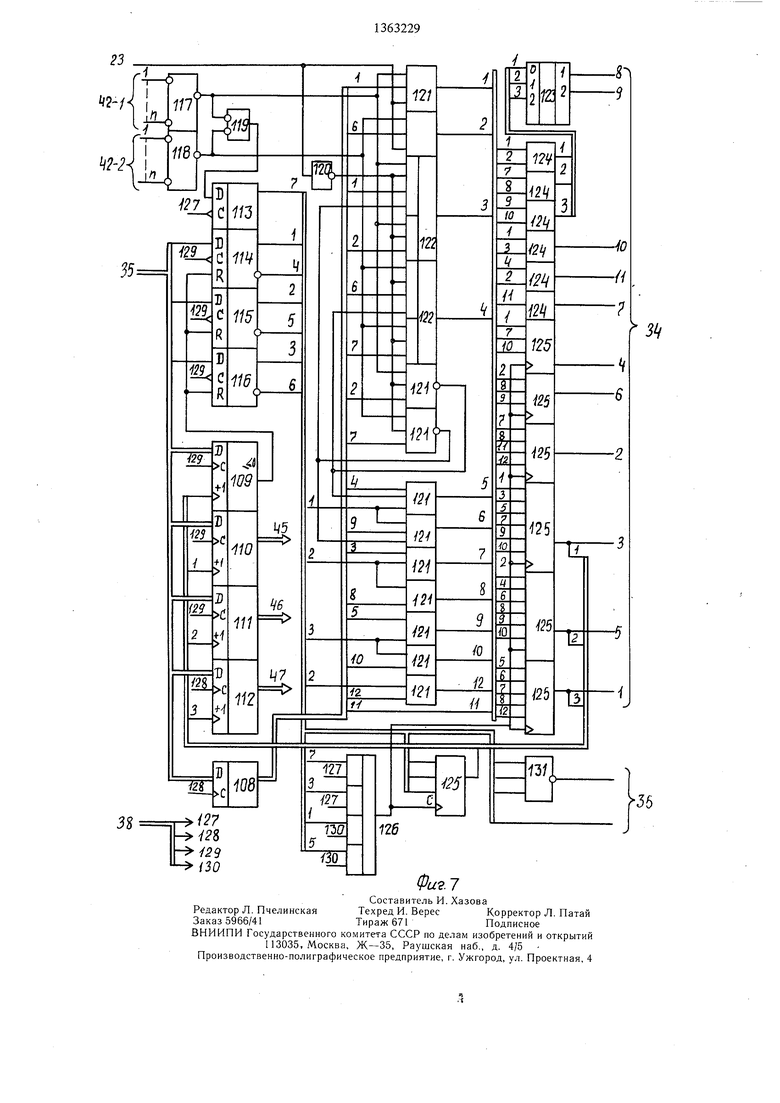

На фиг. 1 показана структурная схема устройства; на фиг. 2 - структурная схе1363229

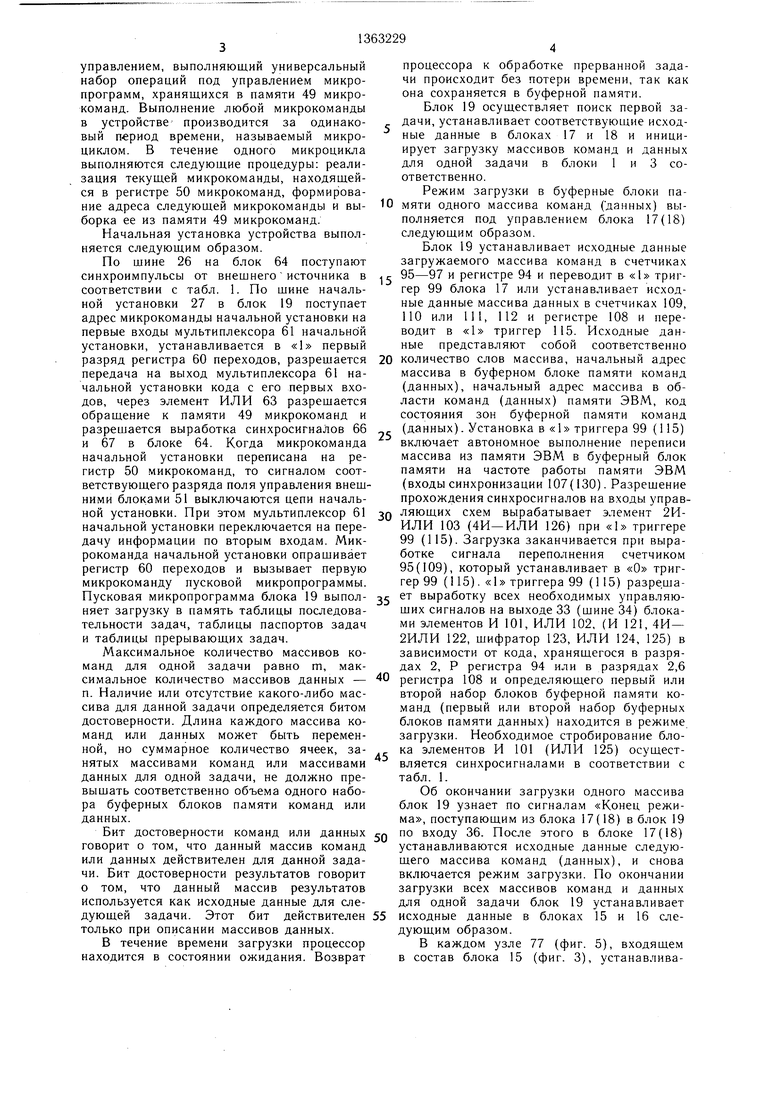

пределения синхроимпульсов, в состав которого входят три элемента 2И-2ИЛИ, два элемента НЕ и блок элементов И. Соответствие между синхроимпульсами с входа 26 5 и синхросигналами с входов 65-76, управляющими внутренними узлами блока и внешними блоками, представлено в табл. 1.

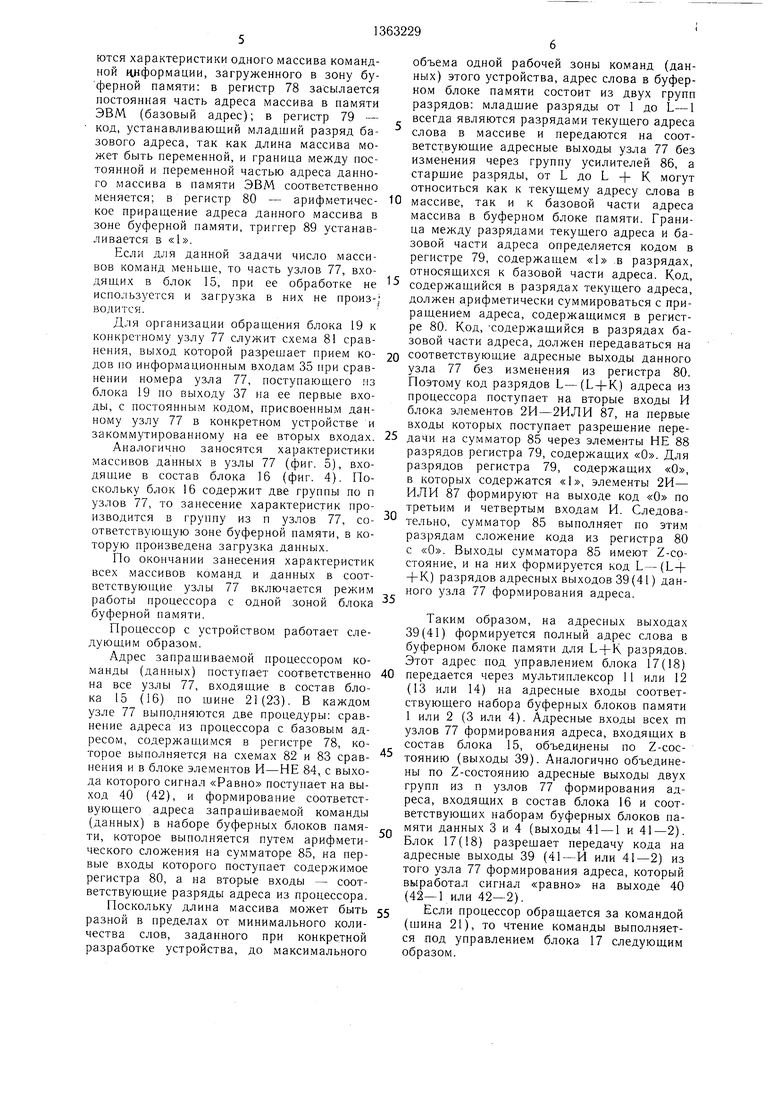

Блок 15 (фиг. 3) содержит m одинаковых узлов формирования адреса и соединен адресными выходами 39 с входами муль25

ма блока синхронизации; на фиг. 3 - струк- О типлексоров И и 12, стробирующими вы- турная схема первого блока формирования ходами 40 - с входами разрешения блока 17.

Блок 16 (фиг. 4) содержит 2п одинаковых узлов формирования адреса 77 и соеди- с нен адресными выходами 41 - 1 и 41-2 с входами соответственно мультиплексоров 13 и 14, а стробирующими выходами 42-1 и 42-2 с соответствующими входами разрешения блока 18.

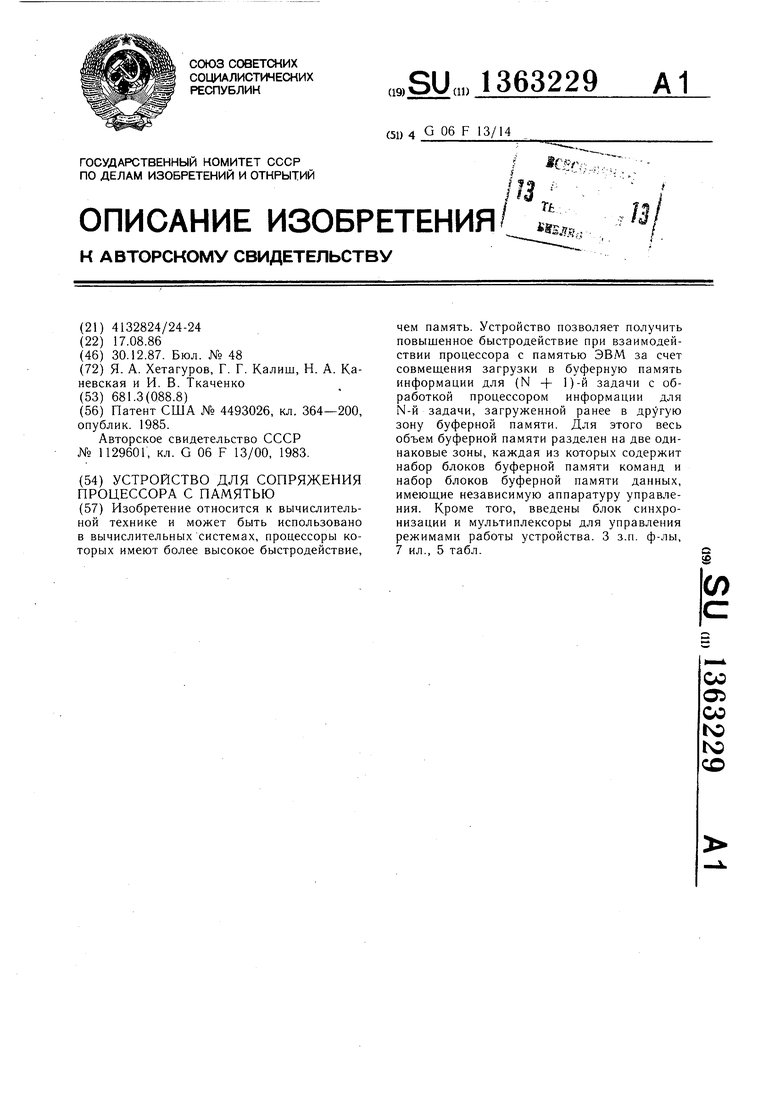

Узел формирования адреса (фиг. 5) соферной памяти, состоящий из двух оди- 20 держит первый регистр 78 базы, второй ре- наковых наборов буферных блоков 1 и 2 гистр 79 маски базы, третий регистр 80 фор- памяти команд и двух одинаковых наборов мирования адреса, третью схему 81 сравнения номера блока, первую 82 и вторую 83 схемы сравнения базового адреса, блок элементов И - НЕ 84, сумматор 85, группу усилителей 86 с тремя состояниями., группу элементов И-ИЛИ 87, группу элементов НЕ 88, триггер 89, элемент И-НЕ 90.

Входы 91-93 синхронизации подключены к выходам 38 блока синхронизации в соответствии с табл. 1.

Блок 17 (фиг. 6) содержит регистр 94 состояния зон, счетчики 95-97, триггеры 98 и 99, элемент ИЛИ 100 и шифратор, состоящий из блока элементов И 101, блока элементов ИЛИ 102, элемента 2И-

данных из памяти ЭВМ, шину 25 данных из 5 - З, и входы 104-107 синхронизации, процессора, шины 26 и 27 синхроимпуль-Назначение разрядов регистра (RG) 94

и соответствующие номера линий выходной шины регистра указаны в табл. 2. Наименование разрядов выхода 33 и входа 36 указаны в табл. 3. Там же указано,

выход 33 команд в память ЭВМ, управляю- 40 под управлением каких триггеров вырабаты- щую шину 34 в память ЭВМ,.входы 35 и 36 вается данный сигнал (БПК1 и БПК2 -

адресов; на фиг. 4 - структурная схема второго блока формирования адресов; на фиг. 5 - функциональная схема узла формирования адреса; на фиг. 6 - функциональная схема блока формирования адресов команд; на фиг. 7 - функциональная схема блока формирования адресов данных.

-Устройство содержит набор, блоков бубуферных блоков 3 и 4 памяти данных, мультиплексоры 5 и 6 адресов команд и данных, мультиплексор 7 команд, второй 8, третий 9, четвертый 10 мультиплексоры данных, первый 11 и второй 12 мультиплексоры адресов команд, первый 13 и второй 14 .мультиплексоры адресов данных, первый 15 и второй 16 блоки формирования адресов, блоки 17 и 18 формирования адресов ко- on манд и данных, блок 19 синхронизации, первый мультиплексор 20 данных, адресную тину 21 команд из процессора, информационную шину 22 команд из памяти ЭВМ, адресную шину 23 из процессора, шину 24

сов и начальной установки, адресную шину 28 команд в память ЭВМ, шины 29 и 30 команд и данных в процессор, шину 31 данных и адресную шину 32 в память ЭВМ,

и выходы 37 и 38 блока синхронизации, выходы 39 и 40 блока 15, выходы 41 и 42 блока 16, выходы 43 и 44 блока 17 и выходы 45-47 блока 18.

Блок синхронизации (фиг. 2) содержит набор микропроцессорных элементов 48, память 49 микрокоманд, регистр 50 микрокоманд, в состав которого входят поле управления внешними блоками 51, поле управ

первый и второй буферные блоки памяти команд).

Блок 18 (фиг. 7) содержит регистр 108, .г счетчики 109-112, триггеры 113-116, эле- менты ИЛИ 117-119, элемент НЕ 120, блок элементов И 121, два элемента 4И- 2ИЛИ 122, шифратор 123, блок элементов ИЛИ 124, блок элементов ИЛИ с синхронизацией 125, элемент 4И-ИЛИ 126, вхоления внутренними блоками 52, поле ад-50 синхронизации 127-130, элемент И-НЕ реса памяти контроллера 53 и после адре-131. Элементы 120-126 образуют шифратор, са следующей микрокоманды 54, память 55Назначение разрядов регистра 108 указа- контроллера, адресный регистр 56 памятино в табл. 4. Наименования первых уп- контроллера, мультиплексор 57 адреса памя-равляющих выходов 34 указаны в табл. 5. ти контроллера, память 58 переходов, адрес-(БПД1, БПД2 - буферные блоки памяти ный регистр 59 памяти переходов, регистр55 данных).

60 переходов, мультиплексор 61 начальнойУстройство работает следующим образом,

установки, адресный регистр 62 памяти мик-Устройство представляет собой вычислирокоманд, элемент ИЛИ 63, блок 64 рас-тель с автономным микропрограммным

1363229

пределения синхроимпульсов, в состав которого входят три элемента 2И-2ИЛИ, два элемента НЕ и блок элементов И. Соответствие между синхроимпульсами с входа 26 5 и синхросигналами с входов 65-76, управляющими внутренними узлами блока и внешними блоками, представлено в табл. 1.

Блок 15 (фиг. 3) содержит m одинаковых узлов формирования адреса и соединен адресными выходами 39 с входами мульО типлексоров И и 12, стробирующими вы- ходами 40 - с входами разрешения блока 17.

25

20

on

первый и второй буферные блоки памяти команд).

Блок 18 (фиг. 7) содержит регистр 108, счетчики 109-112, триггеры 113-116, эле- менты ИЛИ 117-119, элемент НЕ 120, блок элементов И 121, два элемента 4И- 2ИЛИ 122, шифратор 123, блок элементов ИЛИ 124, блок элементов ИЛИ с синхронизацией 125, элемент 4И-ИЛИ 126, вхоуправлением, выполняющий универсальный набор операций под управлением микропрограмм, хранящихся в памяти 49 микрокоманд. Выполнение любой микрокоманды в устройстве производится за одинаковый п«риод времени, называемый микроциклом. В течение одного микроцикла выполняются следующие процедуры: реализация текущей микрокоманды, находящейся в регистре 50 микрокоманд, формировачальной установки кода с его первых входов, через элемент ИЛИ 63 разрещается обращение к памяти 49 микрокоманд и

процессора к обработке прерванной задачи происходит без потери времени, так как она сохраняется в буферной памяти.

Блок 19 осуществляет поиск первой задачи, устанавливает соответствующие исходные данные в блоках 17 и 18 и инициирует загрузку массивов команд и данных для одной задачи в блоки 1 и 3 соответственно.

Режим загрузки в буферные блоки пание адреса следующей микрокоманды и вы- Ю мяти одного массива команд (данных) выборка ее из памяти 49 микрокоманд.полняется под управлением блока 17(18)

Начальная установка устройства выпол-следующим образом.

няется следующим образом.Блок 19 устанавливает исходные данные

По шине 26 на блок 64 поступают загружаемого массива команд в счетчиках синхроимпульсы от внещнего источника в г 95-97 и регистре 94 и переводит в «1 триг- соответствии с табл. 1. По щине началь-гер 99 блока 17 или устанавливает исходной установки 27 в блок 19 поступает ные данные массива данных в счетчиках 109, адрес микрокоманды начальной установки на110 или 111, 112 и регистре 108 и перепервые входы мультиплексора 61 начально й водит в «1 триггер 115. Исходные дан- установки, устанавливается в «1 первый ные представляют собой соответственно разряд регистра 60 переходов, разрешается 20 количество слов массива, начальный адрес передача на выход мультиплексора 61 на- массива в буферном блоке памяти команд

(данных), начальный адрес массива в области команд (данных) памяти ЭВМ, код состояния зон буферной памяти команд

разрещается выработка синхросигналов 66 „, (данных). Установка в «1 триггера 99 (115) и 67 в блоке 64. Когда микрокоманда включает автономное выполнение переписи начальной установки переписана на ре- массива из памяти ЭВМ в буферный блок гистр 50 микрокоманд, то сигналом соот- памяти на частоте работы памяти ЭВМ ветствующего разряда поля управления внещ- (входы синхронизации 107(130). Разрешение ними блоками 51 выключаются цепи началь- прохождения синхросигналов на входы управ- ной установки. При этом мультиплексор 61 зо схем вырабатывает элемент 2И- начальной установки переключается на пере- ИЛИ 103 (4И-ИЛИ 126) при «1 триггере дачу информации по вторым входам. Мик- 99 (115). Загрузка заканчивается при выра- рокоманда начальной установки опращивает ботке сигнала переполнения счетчиком регистр 60 переходов и вызывает первую 95(109), который устанавливает в «О триг- микрокоманду пусковой микропрограммы. гер 99 (115). «1 триггера 99 (115) разре.ща- Пусковая микропрограмма блока 19 выпол- 35 выработку всех необходимых управляю- няет загрузку в память таблицы последова- ших сигналов на выходе 33 (щине 34) блока- тельности задач, таблицы паспортов задач ми элементов И 101, ИЛИ 102, (И 121, 4И- и таблицы прерывающих задач.2ИЛИ 122, шифратор 123, ИЛИ 124, 125) в

Максимальное количество массивов ко- зависимости от кода, хранящегося в разря- манд для одной задачи равно т, мак-дах 2, Р регистра 94 или в разрядах 2,6

симальное количество массивов данных - 40 регистра 108 и определяющего первый или п. Наличие или отсутствие какого-либо мае- второй набор блоков буферной памяти ко- сива для данной задачи определяется битом достоверности. Длина каждого массива команд или данных может быть переменной, но суммарное количество ячеек, за- ка элементов И 101 (ИЛИ 125) осущест- нятых массивами команд или массивами вляется синхросигналами в соответствии с данных для одной задачи, не должно пре- табл. 1.

выщать соответственно объема одного набо-Об окончании загрузки одного массива

ра буферных блоков памяти команд или блок 19 узнает по сигналам «Конец режи- данных.ма, поступающим из блока 17(18) в блок 19

Бит достоверности команд или данных Q по входу 36. После этого в блоке 17(18) говорит о том, что данный массив команд устанавливаются исходные данные следую- или данных действителен для данной зада- щего массива команд (данных), и снова чи. Бит достоверности результатов говорит включается режим загрузки. По окончании о том, что данный массив результатов загрузки всех массивов команд и данных используется как исходные данные для еле- для одной задачи блок 19 устанавливает дующей задачи. Этот бит действителен 55 исходные данные в блоках 15 и 16 еле- только при описании массивов данных.дующим образом.

В течение времени загрузки процессорВ каждом узле 77 (фиг. 5), входящем

находится в состоянии ожидания. Возврат в состав блока 15 (фиг. 3), устанавливаманд (первый или второй набор буферных блоков памяти данных) находится в режиме загрузки. Необходимое стробирование блорегистра 108 и определяющего первый или второй набор блоков буферной памяти ко- ка элементов И 101 (ИЛИ 125) осущест- вляется синхросигналами в соответствии с табл. 1.

манд (первый или второй набор буферных блоков памяти данных) находится в режиме загрузки. Необходимое стробирование блоются характеристики одного массива командной информации, загруженного в зону бу- ферной памяти: в регистр 78 засылается постоянная часть адреса массива в памяти ЭВМ (базовый адрес); в регистр 79 - код, устанавливающий младший разряд базового адреса, так как длина массива может быть переменной, и граница между постоянной и переменной частью адреса данного массива в памяти ЭВМ соответственно

объема одной рабочей зоны команд (данных) этого устройства, адрес слова в буферном блоке памяти состоит из двух групп разрядов: младшие разряды от 1 до L-1 всегда являются разрядами текущего адреса слова в массиве и передаются на соответствующие адресные выходы узла 77 без изменения через группу усилителей 86, а старшие разряды, от L до L -f К могут относиться как к текущему адресу слова в

меняется; в регистр 80 - арифметичес- Ю массиве, так и к базовой части адреса

массива в буферном блоке памяти. Граница между разрядами текущего адреса и базовой части адреса определяется кодом в регистре 79, содержащем «1 .в разрядах, относящихся к базовой части адреса. Код, содержащийся в разрядах текущего адреса, должен арифметически суммироваться с приращением адреса, содержащимся в регистре 80. Код, содержащийся в разрядах базовой части адреса, должен передаваться на

кое приращение адреса данного массива в зоне буферной памяти, триггер 89 устанавливается в «1.

Если для данной задачи число массивов команд меньше, то часть узлов 77, входящих в блок 15, при ее обработке не испо.чьзуется и загрузка в них не произ-; водится.

Для организации обращения блока 19 к конкретному узлу 77 служит схема 81 сравнения, выход которой разрешает прием ко- 20 соответствующие адресные выходы данного дов по информационным входам 35 при срав- узла 77 без изменения из регистра 80. нении номера узла 77, поступающего из Поэтому код разрядов L-(L-j-K) адреса из блока 19 по выходу 37 на ее первые вхо- процессора поступает на вторые входы И ды, с постоянным кодом, присвоенным дан- блока элементов 2И-2ИЛИ 87, на первые ному узлу 77 в конкретном устройстве и входы которых поступает разрещение пере- закоммутированному на ее вторых входах. 25 дачи на сумматор 85 через элементы НЕ 88 Аналогично заносятся характеристики разрядов регистра 79, содержащих «О. Для

разрядов регистра 79, содержащих «О, в которых содержатся «1, элементы 2И- ИЛИ 87 формируют на выходе код «О по третьим и четвертым входам И. Следовательно, сумматор 85 выполняет по эти.м разрядам сложение кода из регистра 80 с «О. Выходы сумматора 85 имеют Z-co- стояние, и на них формируется код L-(L +

30

35

массивов данных в узлы 77 (фиг. 5), вхо- в состав блока 16 (фиг. 4). Поскольку блок 16 содержит две группы по п узлов 77, то занесение характеристик производится в группу из п узлов 77, соответствующую зоне буферной памяти, в которую произведена загрузка данных.

По окончании занесения характеристик всех массивов команд и данных в соответствующие узлы 77 включается режим работы процессора с одной зоной блока буферной памяти.

Процессор с устройством работает следующим образом.

Адрес запрашиваемой процессором команды (данных) поступает соответственно 40 на все узлы 77, входящие в состав блока 15 (16) по шине 21(23). В каждом узле 77 выполняются две процедуры: сравнение адреса из процессора с базовым адресом, содержащимся в регистре 78, которое выполняется на схемах 82 и 83 сравнения и в блоке элементов И-ПЕ 84, с выхода которого сигнал «Равно поступает на выход 40 (42), и формирование соответствующего адреса запрац иваемой команды (данных) в наборе буферных блоков памя- „ ти, которое выполняется путем арифметического сложения на сумматоре 85, на первые входы которого поступает содержимое регистра 80, а на вторые входы - соответствующие разряды адреса из процессора.

Поскольку длина массива может быть 55 разной в пределах от минимального количества слов, заданного при конкретной разработке устройства, до максимального

+ К) разрядов адресных выходов 39(41) данного узла 77 формирования адреса.

Таким образом, на адресных выходах 39(41) формируется полный адрес слова в буферном блоке памяти для L + K разрядов. Этот адрес под управлением блока 17(18) передается через мультиплексор И или 12 (13 или 14) на адресные входы соответствующего набора буферных блоков памяти 1 или 2 (3 или 4). Адресные входы всех гп узлов 77 фор.мирования адреса, входящих в состав блока 15, oбъeди eнь по Z-coc- тоянию (выходы 39). Аналогично объединены по Z-состоявию адресные выходы двух групп из п узлов 77 формирования адреса, входящих в состав блока 16 и соответствующих наборам буферных блоков памяти данных 3 и 4 (выходы 41 - 1 и 41-2). Блок 17(18) разрещает передачу кода на адресные выходы 39 (41-И или 41-2) из того узла 77 формирования адреса, который выработал сигнал «равно на выходе 40 (42-1 или 42-2).

Если процессор обращается за командой (шина 21), то чтение команды выполняется под управлением блока 17 следующим образом.

объема одной рабочей зоны команд (данных) этого устройства, адрес слова в буферном блоке памяти состоит из двух групп разрядов: младшие разряды от 1 до L-1 всегда являются разрядами текущего адреса слова в массиве и передаются на соответствующие адресные выходы узла 77 без изменения через группу усилителей 86, а старшие разряды, от L до L -f К могут относиться как к текущему адресу слова в

массиве, так и к базовой части адреса

массива в буферном блоке памяти. Граница между разрядами текущего адреса и базовой части адреса определяется кодом в регистре 79, содержащем «1 .в разрядах, относящихся к базовой части адреса. Код, содержащийся в разрядах текущего адреса, должен арифметически суммироваться с приращением адреса, содержащимся в регистре 80. Код, содержащийся в разрядах базовой части адреса, должен передаваться на

соответствующие адресные выходы данного узла 77 без изменения из регистра 80. Поэтому код разрядов L-(L-j-K) адреса из процессора поступает на вторые входы И блока элементов 2И-2ИЛИ 87, на первые входы которых поступает разрещение пере- дачи на сумматор 85 через элементы НЕ 88 разрядов регистра 79, содержащих «О. Для

разрядов регистра 79, содержащих «О, в которых содержатся «1, элементы 2И- ИЛИ 87 формируют на выходе код «О по третьим и четвертым входам И. Следовательно, сумматор 85 выполняет по эти.м разрядам сложение кода из регистра 80 с «О. Выходы сумматора 85 имеют Z-co- стояние, и на них формируется код L-(L +

5

+ К) разрядов адресных выходов 39(41) данного узла 77 формирования адреса.

0

5

Таким образом, на адресных выходах 39(41) формируется полный адрес слова в буферном блоке памяти для L + K разрядов. Этот адрес под управлением блока 17(18) передается через мультиплексор И или 12 (13 или 14) на адресные входы соответствующего набора буферных блоков памяти 1 или 2 (3 или 4). Адресные входы всех гп узлов 77 фор.мирования адреса, входящих в состав блока 15, oбъeди eнь по Z-coc- тоянию (выходы 39). Аналогично объединены по Z-состоявию адресные выходы двух групп из п узлов 77 формирования адреса, входящих в состав блока 16 и соответствующих наборам буферных блоков памяти данных 3 и 4 (выходы 41 - 1 и 41-2). Блок 17(18) разрещает передачу кода на адресные выходы 39 (41-И или 41-2) из того узла 77 формирования адреса, который выработал сигнал «равно на выходе 40 (42-1 или 42-2).

Если процессор обращается за командой (шина 21), то чтение команды выполняется под управлением блока 17 следующим образом.

Сигнал «Равно устанавливает в «1 по одному из m входов элемента ИЛИ 100 триггер 98, разрешающий выработку шифратором необходимых управляюших сигналов на выходах 33, в зависимости от кода, хра- няш,егося в разрядах 1 и 3 регистра 94 и определяюшего, первый или второй набор буферных блоков памяти команд находится в режиме работы с процессором (табл. 2 и 3). Необходимое стробирование осуш,ест- вляется синхросигналами в соответствии с табл. 1.

Работа осуществляется на частоте процессора (входы 104), разрещение прохождения синхросигналов на входы управляющих схем вырабатывает элемент 2И-ИЛИ 103 при состоянии «1 триггера 98.

Если процессор обращается к буферному блоку памяти данных (шина 23), то чтение исходного данного или запись результата выполняется под управлением блока 18 следующим образом.

Поскольку исходными данными может служить результат вычислений предыдущей задачи, то запрашиваемый адрес может находиться как в буферном блоке памяти данных, содержащем исходные данные для текущей задачи, так и в буферном бло-. ке памяти данных, хранящем результаты предыдущей задачи. Поэтому адрес данного из процессора поступает на две группы по п узлов 77 формирования адреса, входящих в состав блока 16, и сигнал «Равно может быть выработан любым из этих блоков (управляющие выходы 42-1 и 42-2). Этот сигнал устанавливает в «1 по одному из входов элемент ИЛИ 117 или 118 и через элемент ИЛИ 119 триггер 114, раз- рещающий щифратору выработку необходимых управляюших сигналов на шине 34, в зависимости от кода, хранящегося в разрядах 1 и 5 регистра 108, и определяющего, первый или второй набор буферных блоков памяти данных находится в режиме работы с процессором (табл. 4 и 5). Необходимое стробирование элементов И121, 4И-2ИЛИ 122 ИЛИ 125 осуществляется синхросигналами в соответствии с табл. 1. Работа осуществляется на частоте процессора X (вход 127), разрещение прохождения синхросигналов на входы управляющих схем вырабатывает элемент 4И-ИЛИ 126 при состоянии «1 триггера ИЗ.

Кроме описанных выще двух основных режимов (работа с процессором и загруз10

15

ферных блоков памяти данные для (1-|-1)-й задачи, необходимо переписать массивы результатов (i-1)-й задачи в память ЭВМ. При этом если какой-либо массив результатов (i-1)-й задачи может служить исходными данными для i-й задачи («1 соответствующего бита достоверности результатов), то исходные данные для () + 1)-й задачи не могут загружаться в область буферной памяти, в которой хранится данный массив.

Режим записи результатов выполняется под управлением блока 18 следующим образом.

Блок 19 устанавливает исходные данные переписываемого массива результатов в счетчиках 109, ПО или 111, 112, регистре 108 и переводит в «1 триггер 114. Исходные данные представляют собой соответственно количество слов массива результата, начальный адрес массива результатов в

20 буферном блоке памяти данных, начальный адрес массива результатов в области данных памяти ЭВМ, код состояния зон буферного блока памяти данных. Установка в «1 триггера 114 включает автономное выполнение переписи массива результатов из буферного блока памяти в память ЭВМ на частоте работы памяти ЭВМ (входы 130), разрещение прохождения синхросигналов на входы управляющих схем вырабатывает элемент 4И-ИЛИ 126 при состоянии «1

5Q триггера 114. Состояние «1 триггера 114 разрешает щифратору выработку всех необходимых управляющих сигналов на щине 34 в зависимости от кода, хранящегося в разрядах 3, 7, 1 и 5 регистра 108, и определяющего, какой набор буферных блоков памяти данных находится в состоянии записи результатов и какой в режиме работы с процессором (табл. 4 и 5). Второе обстоятельство влияет на выполнение переписи массива результатов в тех случаях, когда процессор может обратиться при обработке i-й задачи к массиву результатов (i-1)-й задачи за исходными данными. Тогда возможны одновременно два обращения к буферному блоку памяти, содержащему массив результатов: одно из процессора, другое из

дг блока 18. Для устранения конфликтной ситуации необходимые управляющие сигналы для чтения в процессор вырабатываются первым приоритетом, а управляющие сигналы для записи в память ЭВМ - вторым приоритетом, когда удовлетворен запрос про25

35

40

ка), устройство может работать в режи- о цессора и триггер 113 установлен в «О

ме записи результатов в память ЭВМ и в режиме перезаписи результатов из одного набора буферных блоков памяти в другой. Блок 19 инициирует выполнение режима записи результатов в память ЭВМ тогда.

Эту функцию реализуют элементы 4И - 2ИЛИ 122 и элементы И121 с третьего по щестой. При этом чтение исходного данного в процессор выполняется на частоте работы процессора, а запись в память ЭВМ -

когда закончена обработка процессором 55на частоте работы памяти ЭВМ. Необхо(i-1)-и задачи и произведено переключениедимое стробирование блока элементов

на обработку i-й задачи, так как прежде,ИЛИ 125 осуществляется синхросигналами

чем загружать в освободившийся набор бу-в соответствии с табл. 1.

0

5

ферных блоков памяти данные для (1-|-1)-й задачи, необходимо переписать массивы результатов (i-1)-й задачи в память ЭВМ. При этом если какой-либо массив результатов (i-1)-й задачи может служить исходными данными для i-й задачи («1 соответствующего бита достоверности результатов), то исходные данные для () + 1)-й задачи не могут загружаться в область буферной памяти, в которой хранится данный массив.

Режим записи результатов выполняется под управлением блока 18 следующим образом.

Блок 19 устанавливает исходные данные переписываемого массива результатов в счетчиках 109, ПО или 111, 112, регистре 108 и переводит в «1 триггер 114. Исходные данные представляют собой соответственно количество слов массива результата, начальный адрес массива результатов в

0 буферном блоке памяти данных, начальный адрес массива результатов в области данных памяти ЭВМ, код состояния зон буферного блока памяти данных. Установка в «1 триггера 114 включает автономное выполнение переписи массива результатов из буферного блока памяти в память ЭВМ на частоте работы памяти ЭВМ (входы 130), разрещение прохождения синхросигналов на входы управляющих схем вырабатывает элемент 4И-ИЛИ 126 при состоянии «1

Q триггера 114. Состояние «1 триггера 114 разрешает щифратору выработку всех необходимых управляющих сигналов на щине 34 в зависимости от кода, хранящегося в разрядах 3, 7, 1 и 5 регистра 108, и определяющего, какой набор буферных блоков памяти данных находится в состоянии записи результатов и какой в режиме работы с процессором (табл. 4 и 5). Второе обстоятельство влияет на выполнение переписи массива результатов в тех случаях, когда процессор может обратиться при обработке i-й задачи к массиву результатов (i-1)-й задачи за исходными данными. Тогда возможны одновременно два обращения к буферному блоку памяти, содержащему массив результатов: одно из процессора, другое из

г блока 18. Для устранения конфликтной ситуации необходимые управляющие сигналы для чтения в процессор вырабатываются первым приоритетом, а управляющие сигналы для записи в память ЭВМ - вторым приоритетом, когда удовлетворен запрос про5

5

0

о цессора и триггер 113 установлен в «О

цессора и триггер 113 установлен в «О

Эту функцию реализуют элементы 4И - 2ИЛИ 122 и элементы И121 с третьего по щестой. При этом чтение исходного данного в процессор выполняется на частоте работы процессора, а запись в память ЭВМ -

на частоте работы памяти ЭВМ. НеобхоБлок 19 инициирует выполнение режима перезаписи результатов из одного набора буферных блоков памяти в другой в тех случаях, когда выполнение i-й задачи прерывается запросом к j-й задаче, а исходными данными для i-й задачи являются результаты обработки (i-l)-fl задачи. В этом случае все массивы команд и данных для i-й задачи хранятся в соответствующем наборе буферных блоков памяти команд и данманды в наборе буферных блоков памяти, находящемся в режиме работы с процессором.

При наличии запращиваемой процессором команды блок 15 вырабатывает сигнал «Равно на одном из m управляющих выходов 40. Если этот сигнал не будет вы- работан, триггер 98 устанавливается очередным синхросигналом с выхода 104 в «О и выработка управляющих сигналов на соных до того момента, когда обработка про- 0 ответотвующих выходах 33 прекращается, цессором J-й задачи будет закончена и про-Одновременно в блок 19 по соответствуюдолжится обработка i-й задачи. Но поскольку результаты (i-1)-й задачи хранятся в другом наборе буферных блоков памяти данных.

щему входу 36 поступает управляющий сигнал, инициирующий выполнение микропрограммы, которая переключает в рабочий

в который должны загружаться данные для режим другой набор буферных блоков паj-й задачи, то перед началом затрузки отмеченные массивы результатов («1 бита достоверности результатов) должны быть переписаны в набор буферных блоков памяти, хранящий исходные данные для i-й задачи.

Режим переписи результатов выполняется под управлением блока 18 следующим образом.

Блок 19 устанавливает исходные данмяти команд и данных, при условии, что загрузка в него информации для следующей задачи закончена. При этом устанавливается в «1 признак переключения зон в блоке 19. Процессор во время переклю- 20 чения находится в режиме ожидания. После переключения адрес команды, поступив- щий из процессора, сравнивается с новыми базовыми адресами, хранящимися в узлах 77 формирования адреса, входящих в состав

ные переписываемого массива результатов . блока 17. Если на одном из ш выхо- в счетчиках 109, 110, 111, регистре 108 дов 40 вырабатывается сигнал «Равно, то и переводит в «1 триггер 116.процессор начинает обработку командной и

числовой информации следующей задачи и признак переключения зон гасится. Если

сигнал «Равно не вырабатывается ни на одИсходные данные представляют собой соответственно количество слов переписываемого массива результатов, начальные адреса массива в обоих буферных блоках памяти- Q ном из m выходов 40, а признак переданных, код состояния зон буферной памя-ключения зон равен «Ь, т.е. задачи нет ни в ти данных (табл. 4). Установка в «1 триг-одном наборе буферных блоков памяти, то гера 116 включает автономное выполнениеблок 19 включает микропрограмму поиска режима перезаписи из одного буферного бло-запращиваемого адреса команды из процес- ка памяти в другой на частоте работы про-сора в списке начальных адресов масси- цессора (входы 127), разрещение прохожде- 5 команд для прерывающих задач. Ког- ния синхросигналов на входы управляющихда запращиваемая задача найдена, то ее несхем вырабатывает элемент 4И-ИЛИ 126обходимо срочно загрузить в те наборы бу- при состоянии «1 триггера 116. Состоя-ферных блоков памяти команд и данных, в ние «1 триггера 116 разрещает щифрато-которые перед этим производилась загрузка ру выработку всех необходимых управляю-информации для следующей после прерван- щих сигналов на щине 34 в зависимости 0 ной задачи, от кода, хранящегося в разрядах 4 и 8 регистра 108, и определяющего источник иИнформация прерванной задачи сохра- приемник перезаписываемого Массива.няется в буферной памяти команд и дан- Блок 19 управляет переключением ре-ных до момента возврата к ее выполне- жимов работы первого и второго наборов., нию. Если, например, информация для прер- буферных блоков памяти команд и данныхванной i-й задачи хранилась в первых на(блоки 1, 3 или 2, 4) исходя из предпосылки, что если команды i-й задачи, за- пращиваемые процессором, содержатся в наборе буферных блоков памяти команд, находящемся в данный момент в режиме работы с процессором, то данные для i-й задачи обязательно находятся в соответствующем наборе блоков памяти данных. Отсутствие запращиваемогр процессором данного в такой ситуации является неисправностью.

борах буферных блоков памяти команд и данных (блоки 1 и 3), а во вторые наборы буферных блоков памяти команд и данных загружалась информация для (1+1)-и зада- 50 чи (блоки 2 и 4), то прерывающая j-я задача должна загружаться в блоки 2 и 4, а в блрках 1 и 3 сохраняется информация для 1-й задачи. При этом блок 19 инициирует последовательно режимы:

- запись результатов (i-1)-й задачи из

Поэтому основным признаком для переклю-55 второго набора блоков буферной памяти данчения режимов работы блоков буферной па-ных (блок 4) в память ЭВМ;

мяти является для блока 19 наличие или-перезапись результатов (i-1)-йзадаотсутстБие запращиваемой процессором ко- Чи, которые могут быть исходными данныманды в наборе буферных блоков памяти, находящемся в режиме работы с процессором.

При наличии запращиваемой процессором команды блок 15 вырабатывает сигнал «Равно на одном из m управляющих выходов 40. Если этот сигнал не будет вы- работан, триггер 98 устанавливается очередным синхросигналом с выхода 104 в «О и выработка управляющих сигналов на со ответотвующих выходах 33 прекращается, Одновременно в блок 19 по соответствуюответотвующих выходах 33 прекращается, Одновременно в блок 19 по соответствующему входу 36 поступает управляющий сигнал, инициирующий выполнение микропрограммы, которая переключает в рабочий

режим другой набор буферных блоков памяти команд и данных, при условии, что загрузка в него информации для следующей задачи закончена. При этом устанавливается в «1 признак переключения зон в блоке 19. Процессор во время переклю- 0 чения находится в режиме ожидания. После переключения адрес команды, поступив- щий из процессора, сравнивается с новыми базовыми адресами, хранящимися в узлах 77 формирования адреса, входящих в состав

числовой информации следующей задачи и признак переключения зон гасится. Если

сигнал «Равно не вырабатывается ни на одном из m выходов 40, а признак переключения зон равен «Ь, т.е. задачи нет ни в одном наборе буферных блоков памяти, то блок 19 включает микропрограмму поиска запращиваемого адреса команды из процес- сора в списке начальных адресов масси- команд для прерывающих задач. Ког- да запращиваемая задача найдена, то ее необходимо срочно загрузить в те наборы бу- ферных блоков памяти команд и данных, в которые перед этим производилась загрузка информации для следующей после прерван- ной задачи, Информация прерванной задачи сохра- няется в буферной памяти команд и дан- ных до момента возврата к ее выполне- нию. Если, например, информация для прер- ванной i-й задачи хранилась в первых наном из m выходов 40, а признак переключения зон равен «Ь, т.е. задачи нет ни в одном наборе буферных блоков памяти, то блок 19 включает микропрограмму поиска запращиваемого адреса команды из процес- сора в списке начальных адресов масси- команд для прерывающих задач. Ког- да запращиваемая задача найдена, то ее необходимо срочно загрузить в те наборы бу- ферных блоков памяти команд и данных, в которые перед этим производилась загрузка информации для следующей после прерван- ной задачи, Информация прерванной задачи сохра- няется в буферной памяти команд и дан- ных до момента возврата к ее выполне- нию. Если, например, информация для прер- ванной i-й задачи хранилась в первых наборах буферных блоков памяти команд и данных (блоки 1 и 3), а во вторые наборы буферных блоков памяти команд и данных загружалась информация для (1+1)-и зада- чи (блоки 2 и 4), то прерывающая j-я задача должна загружаться в блоки 2 и 4, а в блрках 1 и 3 сохраняется информация для 1-й задачи. При этом блок 19 инициирует последовательно режимы:

- запись результатов (i-1)-й задачи из

второго набора блоков буферной памяти данми для i-й задачи («1 бита достоверности результатов для данного массива) из блока 4 в блок 2;

-загрузка командной и числовой информации для j-й задачи в блоки 3 и 4 соответственно;

. - включение режима работы с процессором для вторых наборов буферных блоков памяти команд и данных (блоки 3 и 4). По окончании выполнения j-й задачи блок 19 .переключает в режим работы с процессором первые наборы буферных блоков памяти команд и данных (блоки 1 и 2) и процессор заканчивает обработку i-й задачи. Одновременно блок 19 инициирует для вторых наборов буферных блоков памяти команд и данных (блоки,3 и 4) следующие режимы:

-запись результатов вычислений j-й задачи в память ЭВМ;

-загрузка командной и числовой информации для (1-(-1)-й задачи.

Выполнение этих режимов совмещено по времени с обработкой процессором i-й задачи. Поэтому при переходе к обработке (1+1)-й задачи вся информация для нее находится в буферных блоках памяти и дополнительных затрат времени не требуется.

Формула изобретения

1. Устройство для сопряжения процессора с памятью, содержащее первые буферные блоки памяти данных и команд, блок синхронизации, первый мультиплексор данных, первые мультиплексоры адресов команд и адресов данных, блоки формирования адресов команд и адресов данных, мультиплексор команд; причем выход мультиплексора данных соединен с входом задания режима блока синхронизации и информационными входами блоков формирования адресов команд и адресов данных, информационные входы мультиплексора данных являются входами устройства для подключения к щине команд адресной щины процессора и информационной щины памяти, первый выход блока синхронизации соединен с синх- ровходами блоков формирования адресов команд и адресов данных, второй выход блока синхронизации соединен с управляющим входом мультиплексора данных, выход первого мультиплексора адресов команд соединен с адресным входом первого буферного блока памяти команд, выход первого мультиплексора адресов данных соединен с адресным входом первого буферного блока памяти данных, первый адресный выход блока формирования адресов команд соединен с первым информационным входом первого мультиплексора адресов команд, первый адресный выход блока формирования адресов данных соединен с первым информационным входом первого мультиплексора адресов данных, тактовый и установочный

5

входы блока синхронизации являются тактовым входом и входом начальной установки устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит г вторые буферные блоки памяти данных и команд, первый и второй блоки формирования адресов, вторые и третьи мультиплексоры адресов команд и адресов данных, второй, третий и четвертый мультиплексоры данных, причем информационные входы

0 первого и второго буферных блоков памяти команд и данных и первый информационный вход мультиплексора команд являются входами устройства для соединения с информационной щиной памяти, адресный вход вто, рого буферного блока памяти команд соединен с выходом второго мультиплексора адресов команд, первый информационный вход которого соединен с первым адресным выходом блока формирования адресов команд, вторые информационные входы перво0 го и второго мультиплексоров адресов команд соединены с адресным выходом первого блока формирования адресов, второй адресный выход блока формирования адресов данных соединен с первым информационным входом второго мультиплексора адресов данных, вторые информационные входы первого и второго мультиплексоров адресов данных соединены с адресным выходом второго блока формирования адресов, первый информационный вход которо, го и первый информационный вход первого блока формирования адресов соединены с выходом первого мультиплексора данных, синхровходы и входы разрешения первого и второго блоков формирования адресов соединены соответственно с первым и вторым

с выходами блока синхронизации, их вторые информационные входы являются входами устройства для соединения соответственно с щиной команд и адресной шиной процессора, а стробирующие входы - соответственно с входами разрещения блоков фор0 мирования адресов команд и адресов данных, второй адресный выход первого блока формирования адресов команд соединен с первым информационным входом третьего мультиплексора адресов команд, а первый , стробирующий выход соединен с управляющими входами первого, второго и третьего мультиплексоров адресов команд и мультиплексора команд и входами записи первого и второго буферных блоков памяти команд и является выходом устройстQ ва для подключения к входу команды памяти, а выходы первого и второго буферных блоков памяти команд соединены с вторым информационным входом мультиплексора команд, выход которого является выходом устройства д.тя соедине5 ния с щиной команд процессора, второй информационный вход третьего мультиплексора адресов команд является входом устройства для подключения к шине команд

процессора, а выход является выходом устройства для подключения к шине адреса команды памяти, третий адресный выход блока формирования адресов данных соединен с первым информационным входом третье- го мультиплексора адресов данных, а первый стробирующий выход соединен с управляющими входами первого, второго и третьего мультиплексоров адресов данных, второго, третьего и четвертого мультиплексоров данных, входами записи первого и второ- го буферных блоков памяти данных и является выходом устройства для подключения к управляющей шине памяти, второй информационный вход третьего мультиплексо- ра адресов данных является входом устройства для подключения к адресной шине процессора, а выход является выходом устройства для подключения к шине адреса данных памяти, выход второго мультиплексора адресов данных соединен с адресным входом второго буферного блока памяти данных, информационные входы первого и второго буферных блоков памяти данных соединены с выходом второго мультиплексора данных, а их информационные выходы соединены с первыми информационными входами второго, третьего и четвертого мультиплексоров данных, вторые и третьи входы которых образуют входы устройства для подключения соответственно к ши-нам данных процессора и памяти, выходы третьего и четвертого мультиплексоров данных являются соответственно выходами устройства для подключения к шинам данных процессора и памяти, вторые стробируюшие выходы первых блоков формирования адресов команд и адресов данных соединены с управляющим входом блока синхронизации, стробирующий вход блока формирования адресов данных является входом устройства для подключения к адресной шине процессора.

2. Устройство по п. 1, отличающееся тем, что блок формирования адресов команд содержит элемент ИЛИ, два триггера, три счетчика, регистр и шифратор, причем инверсные входы элемента ИЛИ образуют вход разрешения блока, а выход соединен с информационным входом первого триггера, единичный выход которого соединен с первым входом шифратора, выходы которого образуют первый стробирующий выход блока, единичный выход первого триггера и нулевой выход второго триггера образуют второй стробирующий выход блока, единичный выход и вход сброса второго триггера соединены соответственно с вторым входом щифратора и выходом первого счетчика, информационные входы второго триггера, первого, второго, третьего счетчиков и регистра образуют информационный вход бло- ка, а их синхровходы и третий, четвертый входы щифратора и синхровход первого триггера образуют синхровход блока, счет

5

5

, 0

0

0

5

5

0

ные входы первого, второго и третьего счетчиков соединены с выходом шифратора, выходы второго и третьего счетчиков являются первым и вторым адресными выходами блока.

3.Устройство по п. 1, отличающееся тем, что блок формирования адресов данных содержит три элемента ИЛИ, четыре триггера, четыре счетчика, регистр, щифра- тор и элемент И-НЕ, причем входы первого и второго элементов ИЛИ образуют вход разрешения блока, а выходы соединены с инверсными входами третьего элемента ИЛИ и первым, вторым входами щифратора, выходы которого образуют первый стробирующий выход блока, выход третьего элемента ИЛИ соединен с информационным входом первого триггера, информационные входы второго, третьего, четвертого триггеров, с первого по четвертый счетчиков и регистра образуют информационный вход блока, а их синхровходы, синхровходы первого триггера и шифратора образуют синхровход блока, нулевые выходы второго, третьего и четвертого триггеров соединены с входами элемента И- НЕ, выход которого и единичный выход первого триггера образуют второй стробирующий выход блока, счетные входы с первого по четвертый счетчиков соединены с соответствующими выходами шифратора, с третьего по десятый входы шифратора соединены соответственно со стробирующим входом блока, единичными выходами с первого по четвертый триггеров, нулевым выходом третьего триггера, вььходом регистра, синх- ровходом блока, выход первого счетчика соединен с входами сброса второго, третьего и четвертого триггеров, выходы второго, третьего и четвертого счетчиков являются первым, вторым и третьим адресными выходами блока.

4.Устройство по п. 1, отличающееся тем, что блок формирования адресов состоит из группы узлов формирования адреса, первые и вторые адресные входы, синхровходы и входы разрешения, адресные и стро- бирующие выходы которых образуют одноименные входы и выходы блока, причем каждый из узлов формирования адреса содержит три регистра, три схемы сравнения, группу элементов НЕ, группу элементов

ИЛИ-НЕ, блок элементов И-НЕ, элемент И-НЕ, триггер, сумматор и группу усилителей с тремя состояниями, причем информационные входы первого, второго и третьего регистров образуют первый информационный вход блока, выход первого регистра соединен с первыми информационными входами первой и второй схем сравнения, вторые информационные входы которых, первые входы элементов И-ИЛИ группы и информационные входы усилителей с тремя состояниями группы образуют второй информационный вход блока, выход второго регистра

соединен с входом разрешения второй схемы сравнения, а также непосредственно и через элементы НЕ группы с вторыми и третьими входами элементов И-ИЛИ группы, четвертые входы которых соединены с шиной нулевого потенциала, а выходы - с первым информационным входом сумматора, второй информационный вход которого соединен с выходом третьего регистра, выходы первой и второй схем сравнения соединены с первым и вторым входами блока элементов И-НЕ, третий вход которого соединен с единичным выходом триггера, нулевой вход которого соединен с первыми входами разрешения первого, второго и третьего регистров, вторые входы разреше- ния которых и информационный вход триггера соединены с выходом равенства третьей

74106, 128, 129

1 р 2 р 3 р 4 р 5 р

1

2 3 4 5

схемы сравнения, выход неравенства которой соединен с первым входом элемента И-НЕ, второй вход которого, управляющие входы усилителей с тремя состояниями группы и вход разрешения сумматора объединены и подключены к выходу блока элементов И-НЕ, который является стро- бируюшим выходом узла, выход элемента И-НЕ соединен с входом сброса триггера, выходы сумматора и усилителей с тремя состояниями группы образуют адресный выход узла, первый вход третьей схемы сравнения является входом разрешения узла, а второй вход соединен с шиной константы, синхровход триггера, первого, второго и третьего регистров, четвертый вход блока элементов И-НЕ, третий вход элемента И- НЕ образуют синхровход узла.

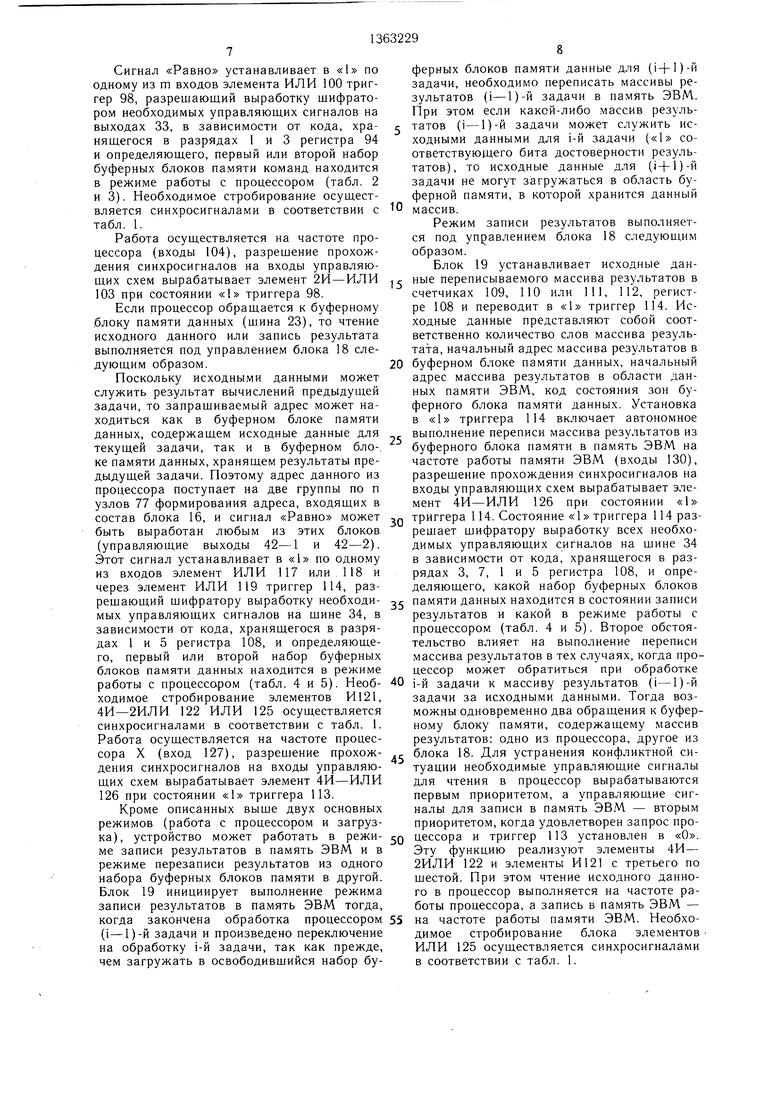

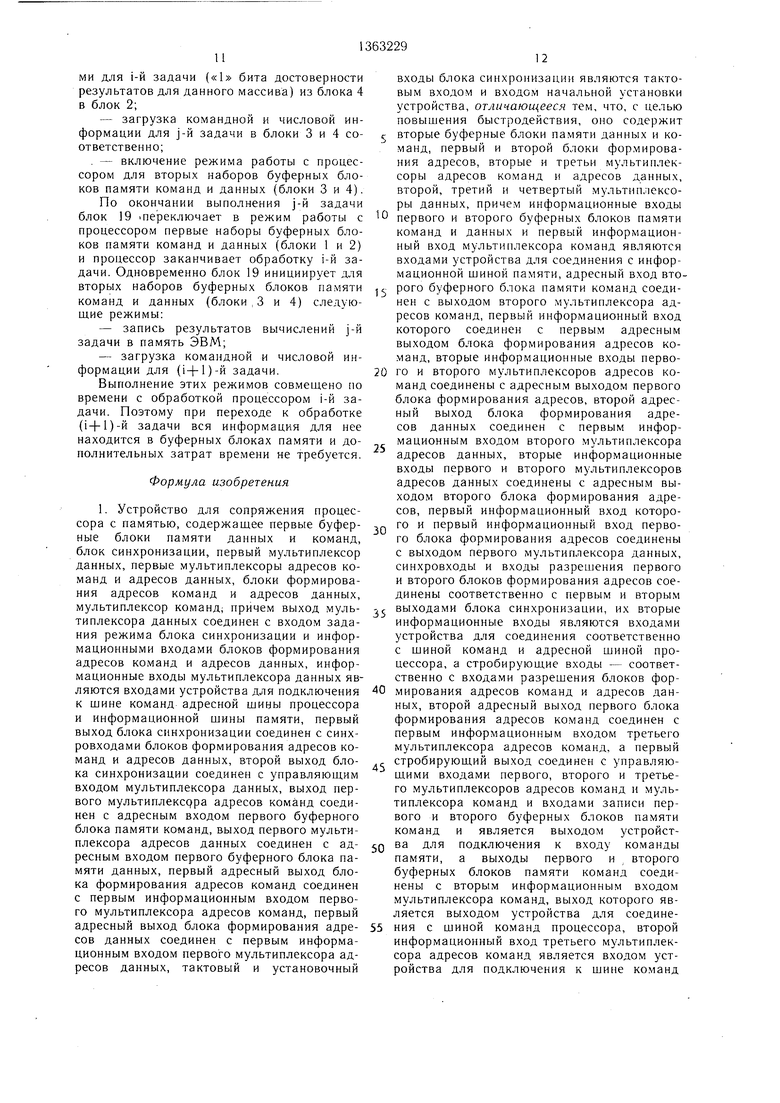

Таблица 1

Таблица 2

БПК1 работает с процессором БПК1 работает с памятью ЭВМ БПК2 работает с процессором БПК2 работает с памятью ЭВМ БПК1, БПК2 отключены

Процессор работает с памятью ЭВМ

17

Обращение к памяти ЭВМ

Обращение к БПК1

Запись в БПК1

Обращение к БПК2

Запись в БПК2

М5: D1 вьпсод М7: D2 выход

МП : D1 -.на выход

Ml 2: вина выход

Конец режима загрузки

Есть информация для процессора

1 4р

1 5р О 5р

6 7

1363229

18

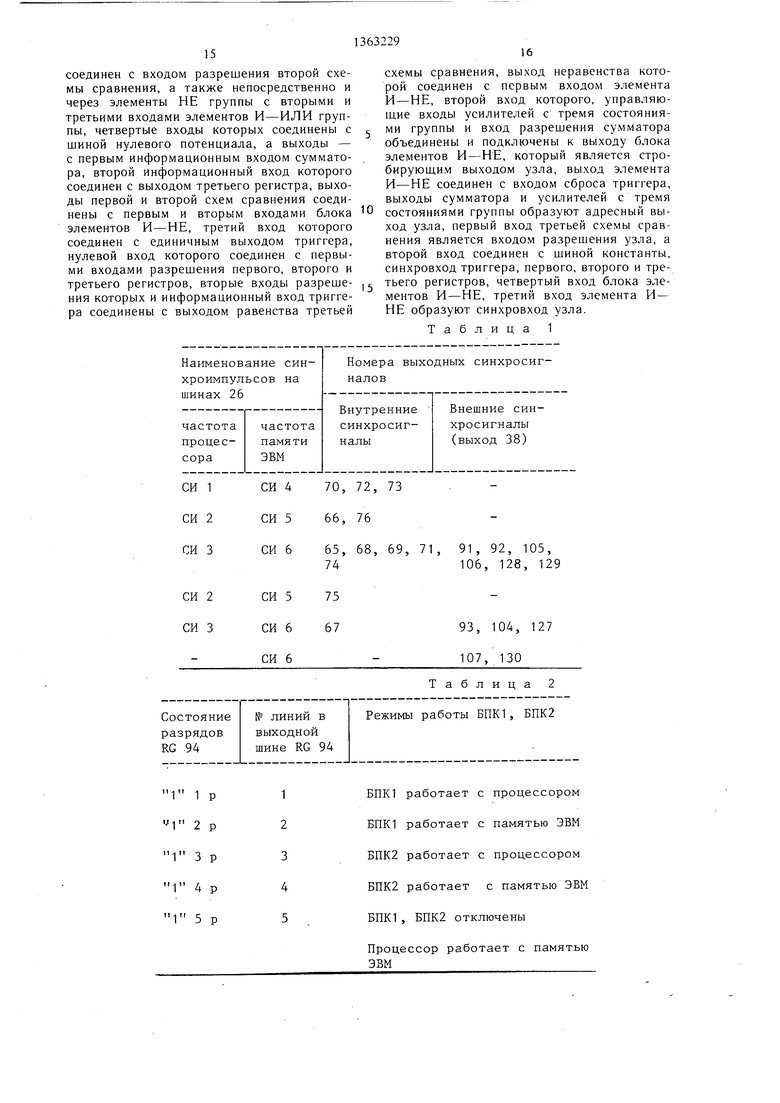

Таблица 3

2, 4, 5р RG 94 1, 2р RG 94 2р RG 94 3, 4р RG 94 4р RG 94 5р RG 94

1р RG 94 Зр RG 94 Т99

Т98

БПД1 работает с .процессором БПД1 не работает с процессором

Загрузка данных в БПД1 из памяти ЭВМ

Запись результатов из БПД1 в память ЭВМ

Перезапись результатов из БПД1 в БПД2

БПД2 работает с процессором БПД2 не работает с процессором

19

Обращение к памяти ЭВМ

Чтение из памяти ЭВМ Обращение к БПД1 Запись в БПД1 Обращение к БПД2 Запись в БПД2

1 2,3,6, 7, 9 RG 108

1 2,6,9, Юр

1 1,2,3, 4р R

1 1,2,8р RG 1

1 5,6,7, 8р R

1 5,6,7, 4pRG

Мб, М9, МЮ: В2-.на выход 1 9р RG 108

выход , 8р RG 108

М8:

выход 1 3,7р RG108

выход 1 2,6р RG108

М13: выход 1 1,Зр RGЮ8

Ml 4: выход 1 2,4р RG108 Есть информация для процессора

Конец режима загрузки, записи результатов, перезаписи

Ч Т 113

О Т 114,115,116

1363229

20

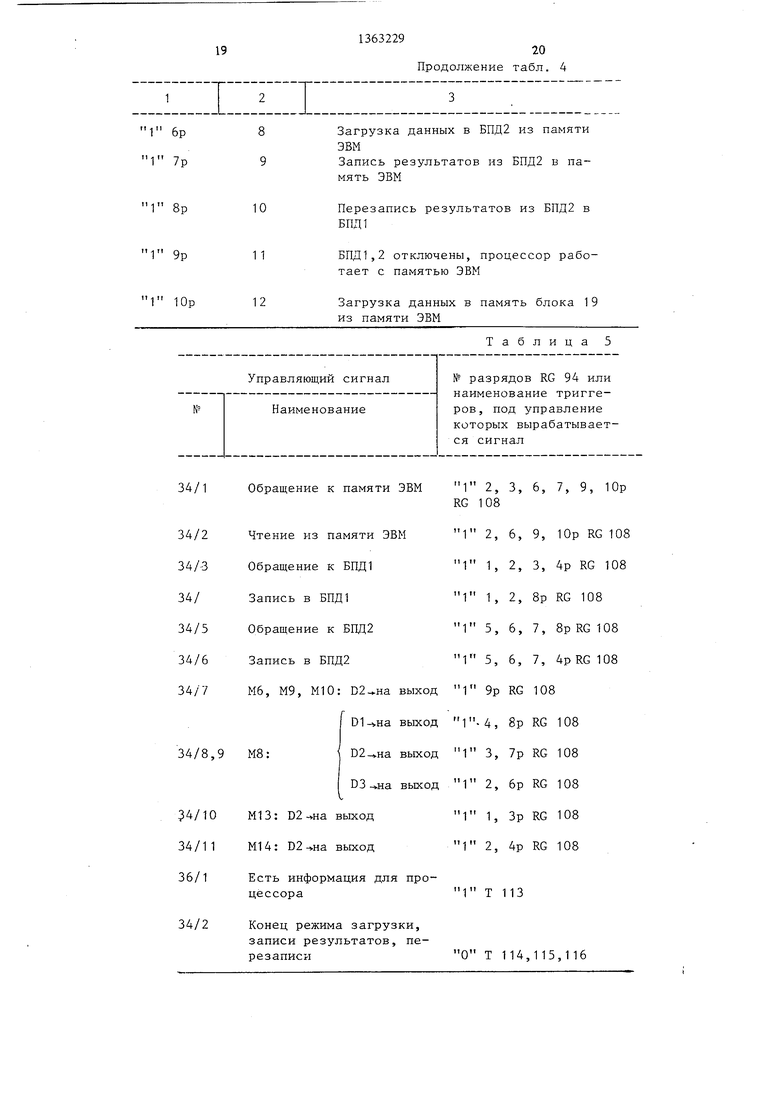

Продолжение табл. 4

Таблица 5

1 2,3,6, RG 108

1 2,6,9,

1 1,2,3,

1 1,2,8р

1 5,6,7,

1 5,6,7,

Ч Т 113

О Т 114,115,116

гг-

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для управления запуском программ | 1985 |

|

SU1287157A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Устройство для отладки управляющего комплекса сортировочной горки | 1984 |

|

SU1237528A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах, процессоры которых имеют более высокое быстродействие. чем память. Устройство позволяет получить повышенное быстродействие при взаимодействии процессора с памятью ЭВМ за счет совмещения загрузки в буферную память информации для (N + 1)-й задачи с обработкой процессором информации для N-й задачи, загруженной ранее в другую зону буферной памяти. Для этого весь объем буферной памяти разделен на две одинаковые зоны, каждая из которых содержит набор блоков буферной памяти команд и набор блоков буферной памяти данных, имеющие независимую аппаратуру управления. Кроме того, введены блок синхронизации и мультиплексоры для управления режимами работы устройства. 3 з.п. ф-лы, 7 ил., 5 табл. Q оо 05 00 ьо ю со

и II II II и II II II

ФигЗ

39

35

| Патент США № 4493026, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Диапазонный фазометр | 1957 |

|

SU112960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-08-17—Подача