рого являются выходами устройства, введены два триггера, причем первый и второй входы первого триггера подключены соответственно к выходу коммутатора и третьему выходу узла синхронизации, а выход - к информационному входу памяти и второму входу схемы сравнения, выходом соединенной с первым входом второго триггера, второй вход которого подключен ко второму выходу узла синхронизации, а выход и третий вход - соответственно к информационному входу и управляющему выходу ysfia согласования с электронной вычислительной машиной адресный вход которого соединен с выходом счетчика и адресным входом памяти, вход пуска узла синхронизации соединен с выходом второго триггера, а вход тактов является тактовым входом устройства.

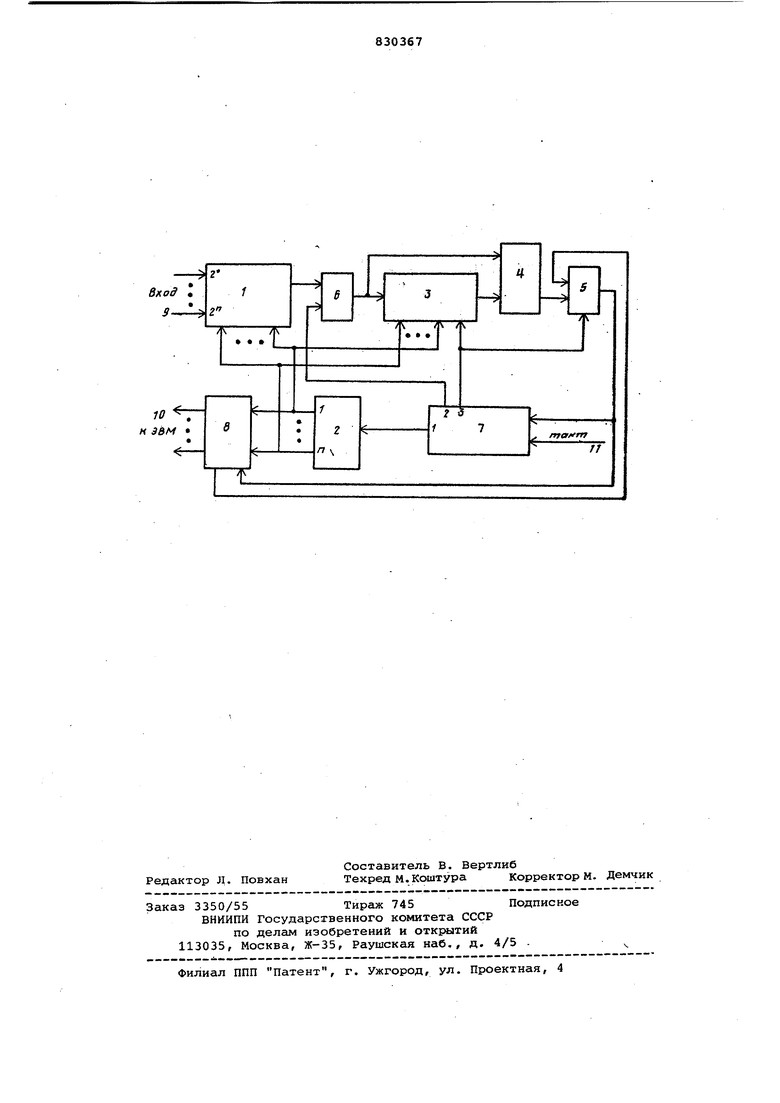

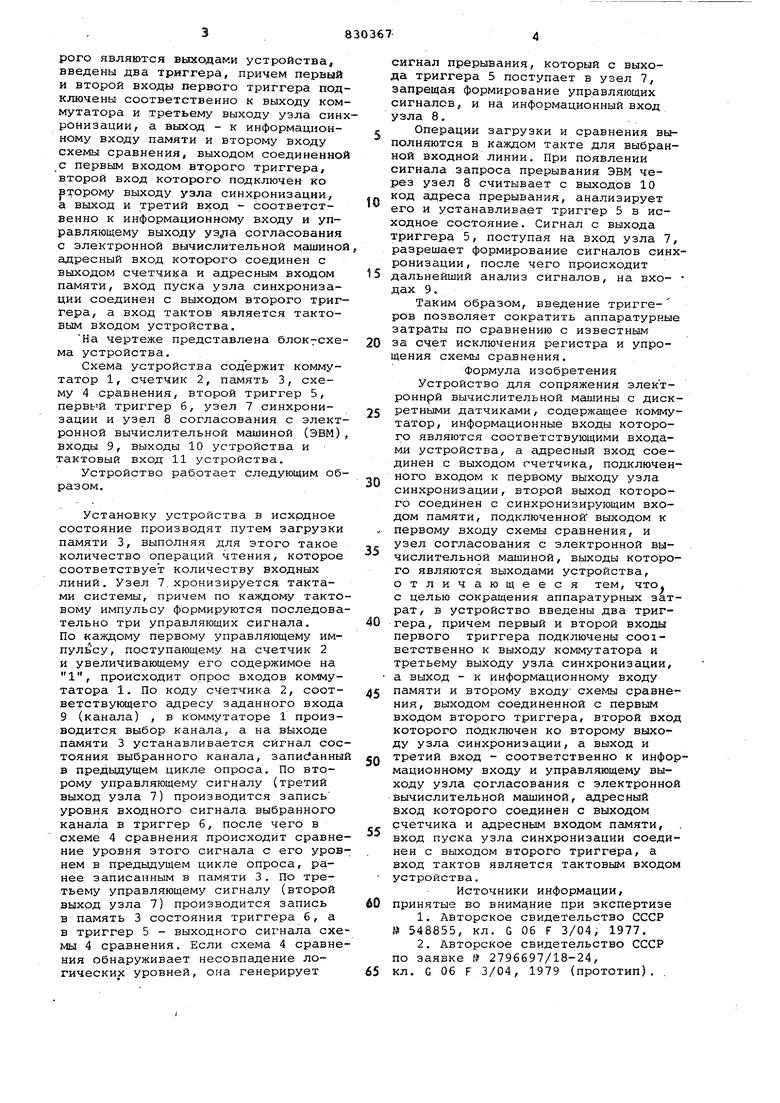

На чертеже представлена блокгсхема устройства.

Схема устройства содержит коммутатор If счетчик 2, память 3, схему 4 сравнения, второй триггер 5, первый триггер б, узел 7 синхронизации и узел 8 согласования с электронной вычислительной машиной (ЭВМ) входы 9, выходы 10 устройства и тактовый вход 11 устройства.

Устройство работает следующим образом.

Установку устройства в исхрдное состояние производят путем загрузки памяти 3, выполняя для этого такое количество операций чтения, которое соответствует количеству входных линий. Узел 7.хронизируется тактами сис;те2 1ы, причем по каждому тактовому импульсу формируются последовательно три управляющих сигнала. По каждому первому управляющему импулйсу, поступающему на счетчик 2 и увеличивающему его содержимое на 1, происходит опрос входов коммутатора 1. По коду счетчика 2, соответствующего адресу заданного входа 9 (канала) , в коммутаторе 1 производится выбор канала, а на выходе памяти 3 устанавливается сигнал состояния выбранного канала, запис анны в предыдущем цикле опроса. По второму управляющему сигналу (третий выход узла 7) производится запись уров.ня входного сигнала выбранного канала в триггер б, после чего в схеме 4 сравнения происходит сравнение уровня этого сигнала с его уровнем в предьщущем цикле опроса, ранее записанным в памяти 3. По третьему управляющему сигналу (второй выход узла 7) производится запись в память 3 состояния триггера 6, а в триггер 5 - выходного сигнала схемы 4 сравнения. Если схема 4 сравнения обнаруживает несовпадение логических уровней, она генерирует

сигнал прерывания, который с выхода триггера 5 поступает в узел 7, запрещая формирование управляющих сигналов, и на информационный вход узла 8.

Операции загрузки и сравнения выполняются в каждом такте для выбранной входной линии. При появлении сигнала запроса прерывания ЭВМ через узел 8 считывает с выходов 10 код адреса прерывания, анализирует его и устанавливает триггер 5 в исходное состояние. Сигнал с выхода триггера 5, поступая на вход узла 7, разрешает формирование сигналов синхронизации, после чего происходит дальнейший анализ сигналов, на входах 9.

Таким образом, введение триггеров позволяет сократить аппаратурные затраты по сравнению с известным за счет исключения регистра и упрощения схемы сравнения.

Формула изобретения Устройство для сопряжения электроннрй вычислительной машины с дискретными датчиками, содержащее коммутатор, информационные входы которого являются соответствующими входами устройства, а адресный вход соединен с выходом счетчика, подключенного входом к первому выходу узла синхронизации, второй выход которого соединен с синхронизирующим входом памяти, подключенной выходом к первому входу схемы сравнения, и узел согласования с электронной вычислительной машиной, выходы которого являются выходами устройства, отличаю а1ееся тем, что. с целью сокращения аппаратурных затрат, в устройство введены два триггера, причем первый и второй входы первого триггера подключены cooiветственно к выходу коммутатора и третьему выходу узла синхронизации, а выход - к информационному входу памяти и второму входу сравнения, выходом соединенной с первым входом второго триггера, второй вход которого подключен ко второму выходу узла синхронизации, а выход и третий вход - соответственно к информационному входу и управляющему выходу узла согласования с электронной вычислительной машиной, адресный вход которого соединен с выходом счетчика и адресным входом памяти, вход пуска узла синхронизации соединен с выходом второго триггера, а вход тактов является тактовым входом устройства.

Источники информации, принятые во внима,ние при экспертизе

1.Авторское свидетельство СССР № 548855, кл, G 06 F 3/04, 1977.

2.Авторское свидетельство СССР по заявке № 2796697/18-24,

кл. G 06 F 3/04, 1979 (прототип).

йкоЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Устройство для прерыванияпРОгРАММ | 1979 |

|

SU817716A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1987 |

|

SU1437870A2 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1986 |

|

SU1381523A2 |

| Устройство для сопряжения телеграфных каналов с электронной вычислительной машиной | 1982 |

|

SU1067494A1 |

| Вычислительное устройство для спектроаналитических приборов | 1975 |

|

SU527709A1 |

Авторы

Даты

1981-05-15—Публикация

1979-08-03—Подача