Изобретение относится к вычислительной технике и может быть использовано при делении п-разрядных чиС(1Л.

Цель изобретения - повьшение быстродействия устройства за счет формирования за один цикл точного К разрядного частного.

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - структурная схема первого шифратора; на фиг.З - структурная схема второго шифратора; на фиг, 4 - структурная схема блока управления; на фиг, 5 - временная диаграмма работы блока управления,

Блок-схема предлагаемого устройства (фиг.1) содержит регистр 1 делимого, регистр 2 делителя, блок 3 приближенного деления, умножитель 4 сумматор-вычитат ель 5, группу элементов И 6, S сумматоров 7, группу элементов И §, элемент НЕ 9, мультиплексор 10, 5 вычитателей 11, узел

12формирования кратных, шифраторы

13и 14, мультиплексор 15, группу элементов ИЛИ 16, группу элементов И 17, блок 18 управления, буферный регистр 19, группу элементов ИЛИ 20 сумматор-вычитатель 21, демультиплек сор 22, регистр 23 частного, группу элементов И 24, выход 25 Конец деления, вход 26 делимого, вход 27 делителя, вход 28 тактовых импульсов, вход 29 числа циклов деления, выход 30 частного.

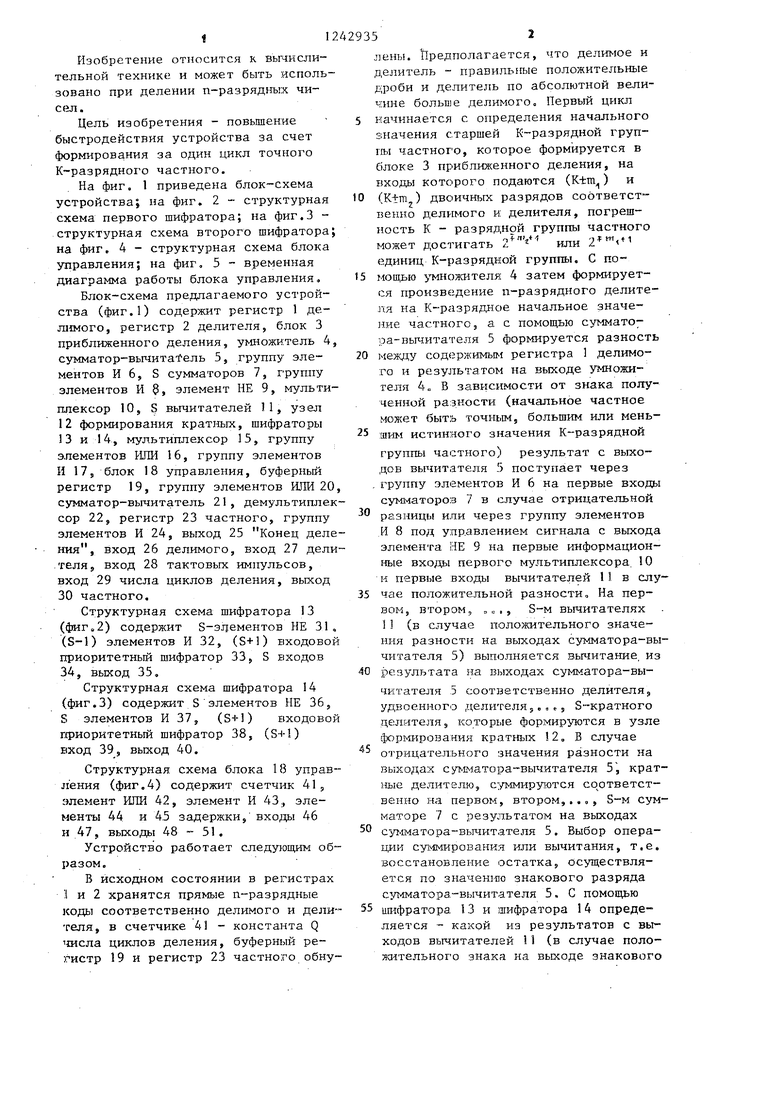

Структурная схема шифратора 13 (фиг«2) содержит S-элементов НЕ ЗК (S-1) элементов И 32, (S+1) входовой приоритетньй шифратор 33, S входов 34, выход 35,

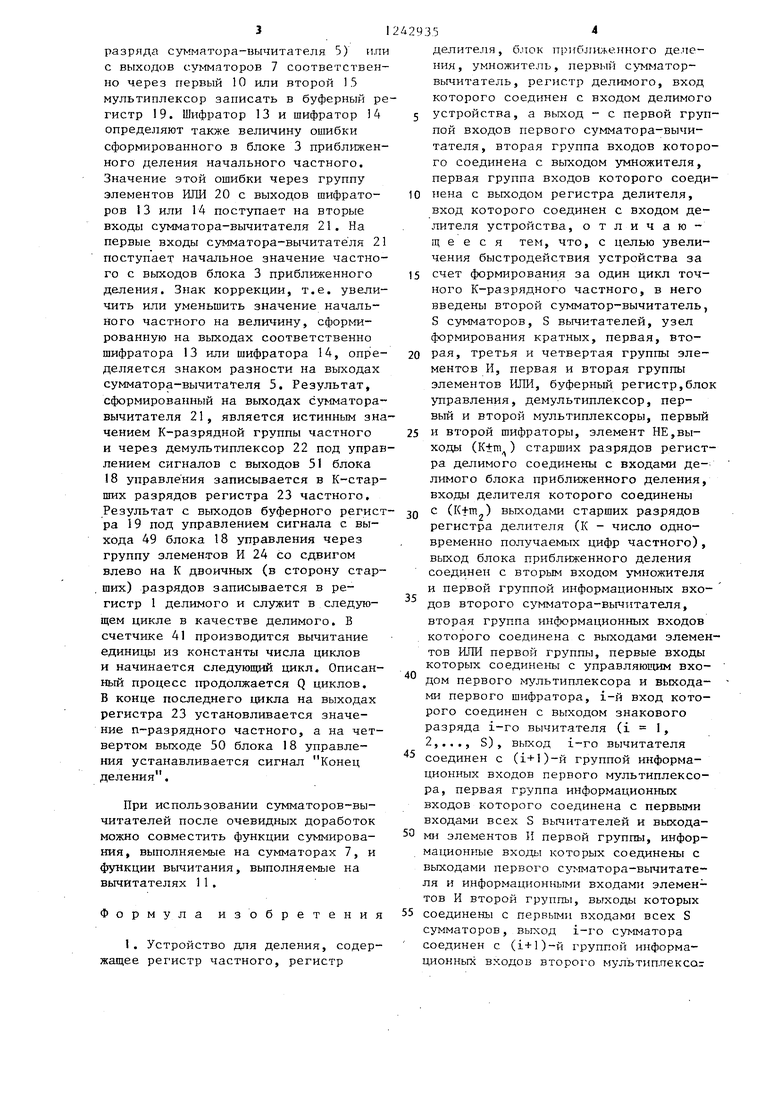

Структурная схема шифратора 14 (фиг.З) содержит.S элементов НЕ 36, S элементов И 37, () входовой приоритетный шифратор 38, (8н-1) вход 39, выход 40.

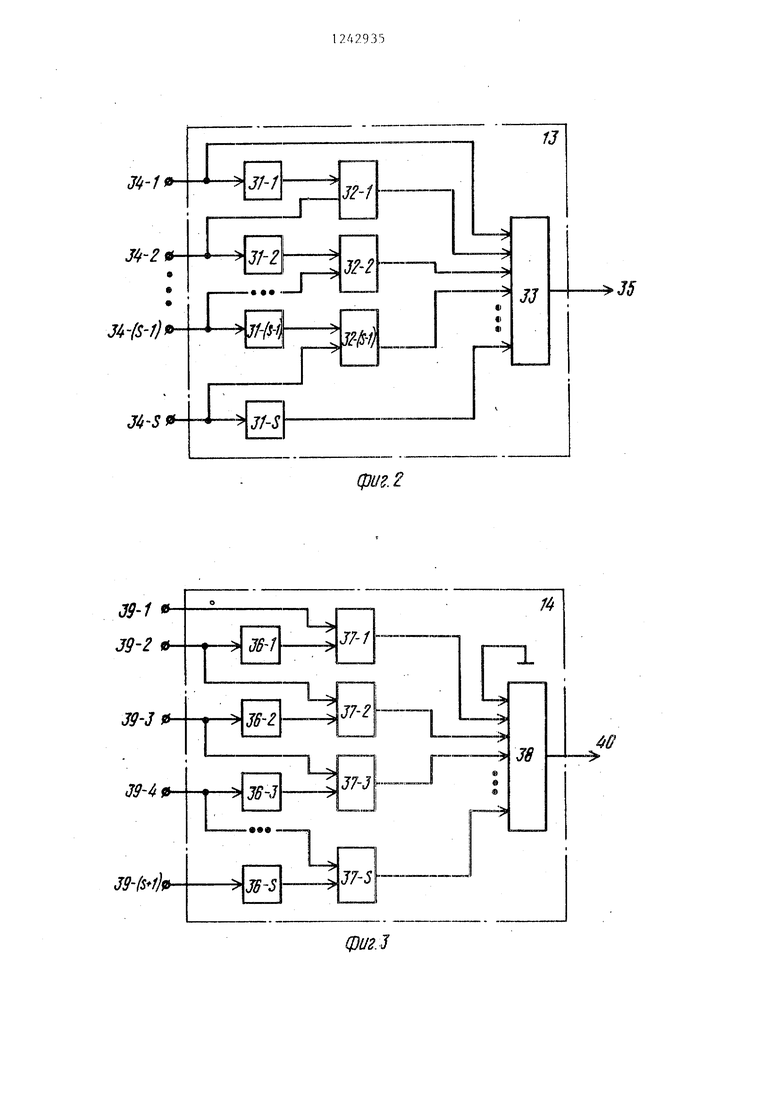

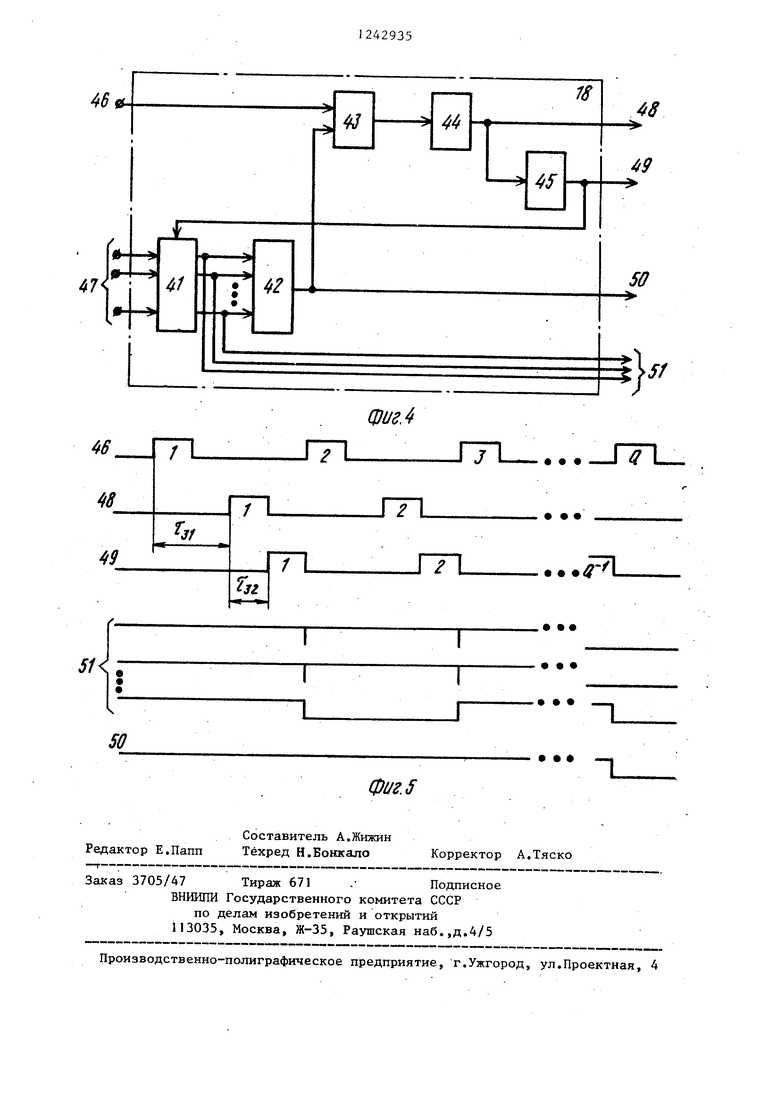

Структурная схема блока 18 управления (фиг,4) содержит счетчик 41, элемент ШШ 42, элемент И 43., элементы 44 и 4.5 задержки, входа 46 и 47, выходы 48-51,

Устройство работает следу ощим образом.

В исходном состоянии в регистрах 1 и 2 хранятся прямые п-разрядные коды соответственно делимого и делителя, в счетчике 41 - константа Q шсла циклов деления, буферный регистр 19 и регистр 23 частного обну

лены. Предполагается, что делимое и делитель правильные положительные дроби и делитель по абсолютной величине больше делимого, Нервый цикл

начинается с определения начального значения старшей К-разрядной группы частного, которое формируется в блоке 3 приближенного деления, на входы которого подаются (Ktm) и

(Ktm ) двоичных разрядов соответственно делимого и: делителя, погрешность К - разрядной группы частного

о 4 fl . t t У- НТ 1

может достигать Z или z единиц К-разрядной группы. С помошд ю т ножителя 4 затем формируется произведение п-разрядного делителя на К-разрядное начальное значение частного, а. с помощью суммато- :ра-вычитателя 5 формируется разность

между содержимым регистра 1 де.пимо- го и результатом на выходе умножителя 4„ В зависимости от знака полученной разности (начальное частное может быть точным, большим или мень:(И1;1м истинного значения К-разрядной

группы частного) результат с выходов вычитателя 5 поступает через группу элементов И 6 на первые входы сумматоров 7 в случае отрицательной

разницы или через группу элементов .И 8 под управлением сигнала с выхода элемента НЕ 9 на первые информационные входы первого мультиплексора, 10 и первые входы вычитателей 11 в слу

чае положительной разности. На первом, втором, „., S-M вычитателях 11 (в случае положительного значения разности на выходах сунматора-вы- читателя 5) выполняется вычитание, из

результата на выходах сумматора-вычитателя 5 соответственно делителя, удвоенного делителя,е«е, З-кратного делителя,, которые формируются в узле формирования кратных 2„ В случае отрицательного значения разности на вь5ходах сумматора-вычитателя 5, кратные делителю, с- гммируются cqoTBeTCT- венно на первом, втором,,.,, S-м сумматоре 7 с результатом на выходах

сумматора-вычитателя 5. Выбор операции су1.ч1чирования или вычитания, т.е. восстановление остатка, осуществляется по значение знакового разряда С1д.1матора.вычит.ателя 5. С помощью

ашфратора 13 и шифратора 14 определяется - какой из результатов с выходов вычитателей 11 (в случае положительного знака на выходе знакового

3

разряда сумматора-вычитателя 5) или с выходов сумматоров 7 соответственно через первый 10 или второй 15 мультиплексор записать в буферньш ре гистр 19. Шифратор 13 и шифратор 14 определяют также величину ошибки сформированного в блоке 3 приближенного деления начального частного. Значение этой ошибки через группу элементов ИЛИ 20 с выходов шифраторов 13 или 14 поступает на вторые входы сумматора-вычитателя 21. На первые входы сумматора-вычитателя 21 поступает начальное значение частного с выходов блока 3 приближенного деления. Знак коррекции, т.е. увеличить или уменьшить значение начального частного на величину, сформированную на выходах соответственно шифратора 13 или шифратора 14, определяется знаком разности на выходах сумматора-вычитателя 5, Результат, сформированный на выходах сумматора- вычитателя 21, является истинным значением К-разрядной группы частного и через демультиплексор 22 под управлением сигналов с выходов 51 блока 18 управления записывается в К-стар- пшх разрядов регистра 23 частного. Результат с выходов буферного регистра 19 под управлением сигнала с выхода 49 блока 18 управления через группу элементов И 24 со сдвигом влево на К двоичных (в сторону стар- , ших) разрядов записывается в регистр 1 делимого и служит в следующем цикле в качестве делимого, Б счетчике 41 производится вычитание единицы из константы числа циклов и начинается следующий цикл. Описанный процесс продолжается Q циклов. В конце последнего цикла на выходах регистра 23 установливается значение п-разрядного частного, а на четвертом выходе 50 блока 18 управления устанавливается сигнал Конец деления,

При использовании сумматоров-вы- читателей после очевидных доработок можно совместить функции суммирования, выполняемые на сумматорах 7, и функции вычитания, выполняемые на вьмитателях 11,

Формула изобретения

I. Устройство для деления, содержащее регистр частного, регистр

4293,5

делителя, блок 1трибл1икенного деления , умножитель, первый сумматор- вычитатель, регистр делимого, вход которого соединен с входом делимого 5 устройства, а выход - с первой группой входов первого сумматора-вычитателя, вторая группа входов которого соединена с выходом умножителя, первая группа входов которого соеди- 10 иена с выходом регистра делителя, вход которого соединен с входом делителя устройства, отличающееся тем, что, с целью увеличения быстродействия устройства за 15 счет формирования за один цикл точного К-разрядного частного, в него введены второй сумматор-вычитатель, S сумматоров, S вычитателей, узел формирования кратных, первая, вто- 20 рая, третья и четвертая группы элементов И, первая и вторая группы элементов ИЛИ, буферный регистр,блок управления, демультиплексор, первый и второй мультиплексоры, первый 25 и второй шифраторы, элемент НЕ,выходы (К±т) старших разрядов регистра делимого соединены с входами де- лимого блока приближенного деления, входы делителя которого соединены 2Q с (Kfm ) выходами старших разрядов регистра делителя (К - число одновременно получаемых цифр частного), выход блока приближенного деления соединен с вторым входом умножителя и первой группой информационных вхо- дов второго сумматора-вычитателя, вторая группа информационных входов которого соединена с выходами элементов ИЛИ первой группы, первые входы которых соединены с управляюпщм вхо- дом первого ryльтиплeкcopa и вькода- ми первого шифратора, i-й вход которого соединен с выходом знакового разряда i-ro вычитателя (, 2,..,, S), выход i-ro вычитателя соединен с (1+1)-й группой информационных входов первого мультиплексора, первая группа информационных входов которого соединена с первыми входами всех S вычитателей и выхода- 50 ми элементов И первой группы, информационные входы которых соединены с выходами первого сумматора-вычитателя и информационными входами элементов И второй группы, выходы которых 55 соединены с первыми входами всех S сумматоров, выход i-ro сумматора соединен с (iH)-й группой информационных входов второго мультиплексаг

35

40

pa, на первую группу информационных входов которого заведен сигнал логического нуля, а выход соединен с второй группой входов элементов ИЛИ второй группы, первая группа входов которых соединена с выходом первого мультиплексора, управляющие входы второго мультиплексора соединены с выходом второго шифратора и второй группой входов элементов ИЛИ первой группы, выход знакового разряда первого сумматора-вычитателя подключен к управляющим входам элементов И второй группы, управляющему входу сум- мирования второго сумматора-вычитателя, первому входу второго шифратора и к входу элемента НЕ, выход которого соединен с управляющими входами элементов И первой группы и управ- ляющим входом вычитания второго сумматора-вычитателя, выход которого соединен с информационными входами демультиплекгора, выход которого соединен с входами регистра частного, выход которого подключен к выходу частного устройства, вход узла формирования кратных соединен с выходом регистра делителя, а i-й выход узла формирования кратных соединен с вто- рыми группами входов i-x сумматоров и вычитателей, выходы элементов ИЛИ второй группы соединены с информационными входами элементов И третьей группы, управляющие входы которых соединены с первым выходом блока управления, второй выход которого соединен с управляющими входами элементов И четвертой группы, выходы кото- рых соединены с входом регистра дели мого со сдвигом на К разрядов в сторону старших, информационные входы элементов И четвертой группы соединены с выходом буферного регистра,входы которого подключены к выходам эле ментов-И третьей группы, третий выход блока управления соединен с управляющими входами демультиплексора, а четвертый выход соединен с выходом Конец деления устройства, вход тактовых импульсов которого соединен с первым входом блока управления, второй вход которого подключен к .входу числа циклов, деления устр ства.

2. Устройство по п.1, о т л и - чающееся тем, что первый шифратор содержит S элементов НЕ, S -1 элементов И; приоритетный шифратор, первый вход которого соединен с первым входом шифратора и через первый элемент НЕ с первым входом первого элемента И, i-й вход шифратора (i 2,3,,..,, S-1) соединен с вторым входом (;L-l)-ro элемента И и через i-й элемент НЕ - с первым входом i-ro элемента И, S-й вход шифратора соединен с вторым входом (S-l)-ro элемента И и через S-й элемент НЕ - с S-M входом приоритетного шифратора, i-й вход которого соединен с выходом i-ro элемента И, выход приоритетного шифратора соединен с выходом Еифратора,

3.Устройство поп.1,отли- чающееся тем, что второй шифратор содержит S элементов НЕ, S элементов И, приоритетный шифратор, на первый вход которого заведен сигнал логического нуля, i-й вход

(i 2,3,.,., S) приоритетного шифратора соединен с выходом i-ro элемента И, первый вход i-ro элемента И соединен с (i-l)-M входом шифратора, К-й вход шифратора (К 2,3,,,.,S+1) соединен через (К-1)-й элемент НЕ с вторьм входом (K-l)-ro элемента И, выход приоритетного шифратора соединен с выходом шифратора.

4,Устройство по п.1, о тли- чаю щ е е с я тем, что блок управления содержит счетчик, элемент И, первый и второй элементы задержки, элемент ИЛИ, первый вход элемента И соединен с первым входом блока управления, второй вход которого соединен с информационными входами счетчика, выход элемента И соединен через первый элемент задержки с первым выходом блока управления и входом второго элемента задержки, выход которого подключен к второму выходу блока управления и к входу вычитания единицы счетчика, выход которого соединен с входами элемента ИЛИ

и третьим выходом блока управления, выход элемента ИЛИ подключен к второму }зходу элемента И и четвертому выходу блока управления.

26

27

фиг.З

фи. 2

Составитель А.Жижин Редактор Е.Папп Техред Н.Бонкало Корректор А.Тяско

Заказ 3705/47 Тираж 671 - Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, Ж-35, Раушская наб.,д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

фиг.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1978 |

|

SU802962A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления | 1982 |

|

SU1086427A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

Изобретение относится к вычислительной технике и может быть использовано при делении п-разрядных чисел. Увеличение быстродействия устройства обеспечивается за счет формирования в каждом цикле начального значения К-разрядного частного и его последующей корректировки. Устройство Jсодержит регистры делимого и делителя, блок деления, умножитель, вьгчи- татель остатка, первый, второй, третий и четвертый узлы элементов И,S сумматоров, элемент НЕ, первый и второй мультиплексоры, S вычитателей, узел кратных, шифратор вычитателей, шифратор сумматоров, первый и второй узлы элементов ИЛИ, блок управления, буферный регистр, узел коррекции, демультиплексор, регистр частного и выход окончания работы устройства. Данное устройство может быть использовано в электронных вычислительных машинах различного назначения в качестве арифмети 1еского расширителя процессора. 3 з.п.ф-лы, 5 ил. с о сл 1C 4 1C QD 00 ел

| Папернов А.А | |||

| Логические осноj вы цифровой вычислительной техники.- М.: Советское радио, 1972 | |||

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-10-15—Подача