ляюпшй вход которого связан с третьим входом первого элемента И, управляюп(им входом первого счетчика импульсов и прямым выходом второго триггера, первым входом соединенного с выходом первого элемента И и первьгм управляющим входом генератора импульсов, второй управляющий вход которого подключен к шине Старт, а выход - к входу генератора стробимпульсов, входу первого счетчика импульсов и управляющему входу аналого-цифрового преобразователя, управляющим выходом подключенного к входу записи первого регистра, четвертому входу первого элемента И и входу записи блока памяти, вход считывания Которого связан с управляющим выходом блока вычислений, а адресный вход - с выходом коммутатора, первый вход которого соединен с выходом блока вычислений, второй вход с выходом первого счётчика импульсов а управляющий вход - с выходом первого элемента И, причем выход блока вычитания подключен к вхо-j ду четвертого блока сравнения кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой стробоскопический преобразователь периодических электрических сигналов | 1983 |

|

SU1260868A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ СО СЖАТИЕМ | 1984 |

|

SU1177836A1 |

| Цифровой согласованный фильтр для импульсных эхо-сигналов | 1981 |

|

SU964979A1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ПЕРИОДИЧЕСКОГО ЭЛЕКТРИЧЕСКОГО СИГНАЛА В КОД И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1989 |

|

SU1800927A1 |

| Цифровое устройство для измерения частоты | 1982 |

|

SU1114966A1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

1ЩФРОВОЙ СТРОБОСКОПИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДИЧЕСКИХ. ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ, содержащий смеситель, первый вход которого соединен с шиной входного сигнала, второй . вход - с выходом генератора стробимпульсов ,а выход - с входом усилйгеля-расширителя, выход которого подключен к входу аналого-цифрового преобразователя, выходом связанного с первым входом блока вычитания и .входом первого регистра, выход которого соединен с входом второго ре гистра и вторым входом блока вычита ния, выходом знака связанного с первым входом первого триггера и первым входом блока совпадений, второй вход которого соединен с выходом первого триггера, а выход - с первым в содом первого элемента И, второй вход которого подключен к выходу первого блока сравнения кодов, а выход - к управляющему входу блока вьмислений, первый информационный вход которого связан с выходом второго счетчика импульсов, а второй информационный вход - с выходом первого счетчика импульсов, причем выход второго регистра подключен к первому входу первого блока сравнения кодов, а вы ход блока памяти - к шине Выход, о тлич ающийс я тем, что, с целью з еньшения времени преобразования он снабжен генератором импульсов, вторым триггером, третьим регистром, вторым, третьим и четвертым блоками сравнения -.кодов, вторым и третьим элементами И, крммута тором и дешифратором нуля, вход которого соединен с информационным входом блока памяти, выходом перво-; го регистра и вторым входом первого блока сравнения кодов, а инверсный (Л выход - с первым входом второго элемента И, второй вход которого подключен к инверсному выходу второго триггера, третий вход - к выходу § четвертого блока сравнения кодов, а выход - к-второму входу первого триггера, входу записи второго ре гистра, второму входу второго триг-, о гера и входу записи третьего регист00 ра, управляющий вход которого свяvj зан с выходом знака блока вычитания 00 второй вход - с выходом аналого-цифрового преобразователя,первый вход-с со с выходом первого регистра и О5 первыми входами второго и тре-. тьего блоков сравнения кодов, а первый и второй выходы - с вторыми--входами второго и третьего блоков сравнения кодов, выходы кото;рых соединены с первым и вторым входами третьего элемента И, третий вход которого подключен к выходу блО ка совпадений, а выход - к входу второго счетчика импульсов, управ

1

Изобретение относится к электроиз мерительной технике и может быть использовано для исследования периоди|ческих электрических сигналов в цифровых измерительных системах,.

Известен цифровой стробоскопический преобразователь электрических сигналов, содержащий генератора тактовьпс импульсов и генератор ctpo6импульсов, смеситель, усилитель-расширитель, аналого-цифровой преобразователь, блок совпадений,сдвиговые ,регистры, формирователь импульсов, управляющий счетчик импульсов, элемент ИЛИ, формирователь периода расширенных импульсов,, дешифратор, два счетчика, блок памяти и блок вычислений IlJ .

Недостатком устройства является большое время получения преобразован ного сигнала, обусловленное большой длительностью этапа ожидания начальной границы инт-ервала преобразования .

Наиболее близким к изобретению по технической сущности является цифровой стробоскопический преобразователь периодических сигналов, содержавши смеситель, первый вход которого соединен с щиной входногр сигнала, второй вход - с выходом генератора строб-импуг.ьсоз, а выход с входом усилителя-расвшрителя, выход которого подключен к входу аналого-цифрового преобразователя, выходом связанного с первым входом блока вычитания и входом первого регистра, выход которого соединен с входом второго регистра и вторым входом блока вычитания, выходом знака связанного с первым входом трип5 гера и первым входом блока совпадений, второй вход которого соединен с выходом триггера, а выход с первым входом элемента И, второй вход которого подключен к выходу

0 блока сравнения кодов, а выход - к управляющему входу блока вычислений, перный информационный вход которого связан с выходом второго счетчика J импульсоо, а второй информационный

5 вход - с выходом первого счетчика импульсов, периый вход которого соединен с выходом генератора стробмпульсоз, а второй вход - с вторым входом триггера, выходом блока ана

0 лиза разности, вторым входом второго счетчика импульсов, вторым входом первого блока памяти и вторым входом второго регистра, выход которого подключенк первому входу блока .

сравнения кодов и третьему входу первого блока памяти, первым входом связанного с выходом аналого-цифрового преобразователя и BTopbs-i входом блока сравнения кодрв,причем выход :

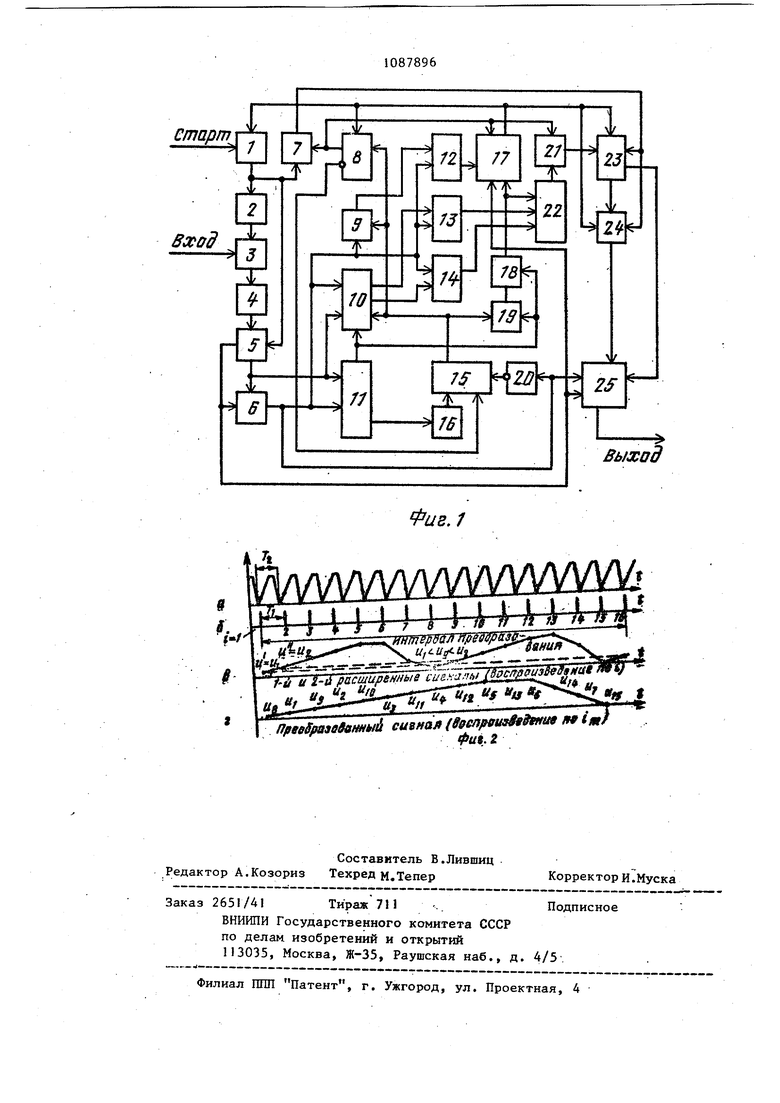

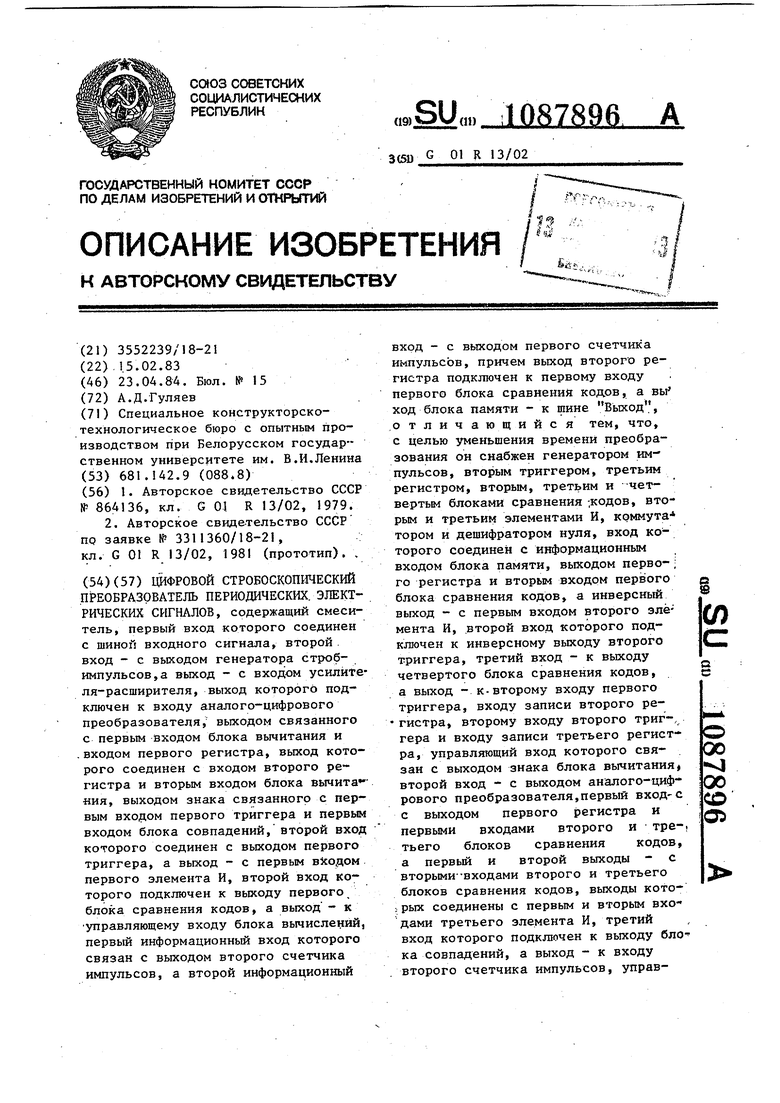

первого блока памяти соединен с первым вХбдом второго блока памяти, второй вход которого подключен к выходу блока вычислений, а выход к шине Выход, вход формирователя расширенных импульсов связан с выходом усилителя-расщирителя , а выход - с первым входом второго счетчика импульсов, выход блока вычитания соединен с входом блока : нализа разности, а выход элемента К - с .вторьм входом аналого -цифрового преобразователя, третий вход которого подкл счен к шине Старт L2J . Недостатком известного устройства является большое время получения преобразованного сигнала. Цель изобретения - уменьшение времени преобразования. Цель достигается тем, что цифровой стробоскопический преобразователь периодических электрических сигна лов, содержащий смеситель, первый вход которого соединен с шиной входного сигнала, вход - с выходом генератора строб-импульсов, а выход - с входом усилителя-расширителя, выход которого подключен к входу аналого-цифрового преобразователя, выходом связанного с первым входом блока вычитания и входом первого регистра, выход которо го соединен с входом второго регистра и вторым входом блока вычитания, выходом знака связанного с первым входом первого триггера и первым входом блока совпадений,второй вход которого соединен с выходом первого триггера, а выход - с первым входом первого элемента И,, второй вход которого подключен к выходу первого блока сравнения крдоб, а выход - к управляющему входу блока вычислений, первый инфор-; мационный вход которого связан с выходом второго счетчика импульсов, а второй информационный вход - с выходом первого счетчика импульсов, при чем выход второго регистра подключен к первому входу перйого блока сравнения КОД9В, а выход блока памяти - к шине Выход, снабжен генератором импульсов, вторым триггером, третьим регистром, вторым, третьим и четвертым блоками сравнения кодов, вторым и третьим элементами И, комму,татором и дешифратором нуля, вход ко торого соединен с информационным входом блока памяти,, рыходом первого регистра и вторым входом первого блока сравнения кодов, а инверсш 1й выход - с первым входом второго элемента И,вто- .; рой вход которого подключен к инверсному выходу второго триггера, третий входом - к выходу четвертого блока орав- ,, нения кодов,а выход - к второму входу первого триггера,входу записи второго регистра,второму входу второго трйг- 1 964 гераивходу записи третьего регистра, управляющий вход которого связан с зы ходом знака блока вычитания, второй вход - с выходом аналого-цифрового преобразователя, первый вход - с выходом первого регистра и первыми входами второго и третьего блоков сравнения кодов, а первый и второй выходы - с вторыми входами второго и третьего блоков сравнения кодов, выходы которых соединены с первым и вторым входами третьего элемента И, третий вход которого подключен к выходу блока совпадений, а выход к входу второго счетчика импульсов, управляющий вход которого связан с третьим входом первого элемента И управляющим входом первого счетчика импульсов и.прямым выходом второго триггера, первым входом соединенного с выходом первого элемента И и первым управлякмцим входом генератора импульсов, второй управляющий вход которого подключен к шине .Старт, а выход - к входу генерат.ора строб-импульсов, входу первого счетчика импульсов и управляющему входу аналого-цифрового преобразователя, управляющим выходом подклю-. ченного к входу записи первого регистра, четвертому входу первого элемента и входу записи блока памяти, вход считьшания которого связан с управляющим выходом блока вычислений, а адресный вход - с выходом коммутатора, первый вход которого соединен с выходом блока вычислений, второй вход - с выходом первого счетчика импульсов, а управляющий вход ,с выходом первого элемента И, причем выход блока вычитания подключен к входу четвертого блока сравнения кодов. .. На фиг, 1 показана структурная электрическая схема предлагаемого устройства на фиг. 2 - временные диаграммы. Устройство состоит из генератора 1 импульсов, генератора 2 строб-импульсов, смесителя 3, усилителя-расширителя 4, аналого-цифрового преобразователя (АЦП) 5, первого регист ра 6, первого счетчика 7 импульсов, второго триггера 8, второго регистра 9, третьего регистра 10, блока II i вычитания, первого 12,: второго 13 и третьего 14 блоков сравнения кодов, второго элемента И 15, четвертого блока 16 сравнения кодов, первого элемента И 17, блока 18 совпадений, первого триггера 19, дешифратора 20 нуля, второго счетчика 21 импульсов третьего элемента И 22 блока 23 вычи лений, коммутатора 24 и блока 25 па мяти. Первый вход смесителя 3 соединен с шиной входного сигнала, второй вход - с выходом генератора 2 стробимпульсов, а выход - с входом усилителя-расширителя 4, выход которого подключен к входу А1Щ 5, вьпсодом связайного с. первым входом блочка 11 вычитания и входом первого регист ра 6, выход которого соединен с входом второго регистра 9 и BToipbiM вход :блока II вычитания,выходом знака свя эаниого с первым входом первого, триг гера 19 и первым входом блока 18 совпадений,второй вход которого соединен выходом первого триггера 19,а выход - с первым входом первого элемента И 17, второй вход которого под ключен к выходу первого блока 12 сравнения кодов, а выход - к управляющему входу блока 23 вычисленийj первый, информационный вход которого связан с- выходом второго счетчика 21 импульсов, а второй информационный вход - с выходом первогосчетчика 7 импульсов,, причем выход второго регистра 9 подключен к первому входу первого блока 12 сравнения кодов, а выход блока 25 памяти - к шине Выход. Вход дешифратора 20 нуля соединен с информационным вхо. дом блока 25 памяти, выходом первого регистра 6 и вторым входом первого блока 12 сравнения кодов, а инверсный выход - с nepsbw входом второго элемента И 15, второй вход которого подключен к инверсному выходу второго триггера 8, третий вход - .к выходу четвертого блока 16 сравнения кодов, а выход - к второму входу первого триггера 19, входу зап си второго регистра 9, второму входу второго триггера 8 и входу записи третьего регистра 10, управляющий вход которого связан с выхо дом знака блока 11 вычитания, второй вход - с выходом АШ 5, первый входс выходом первого регистра 6 и первыми входами второго 13 и третьего 14 блоков сравнения кодов, а ое.рвый и второй вьпсоды - с вторыми входами второго 13 и третьего 14 блоков сравнения кодов, выходы которых соединены с периым и вторым входами третьего элемента И 22, третий вход |которого подключен к. выходу блока 18 совпадений, а выход - к входу JBToporo счетчика 21 импульсов, управЛЯЮП1ИЙ вход которого связан с тре:тьим входом первого элемента И 17, управляющим входом первого счетчика 7 импульсов .и прямым выходом второго триггера 8, первым входом соединенного с выходом первого элемента И I7 и первым управляющим входом генератора 1 импульсов, второй управляющий вход которого подключен к шине Старт, а выход - к входу . , генаратора 2 строб-импульсов,.входу первого счетчика 7 импульсов и управляющему входу АЦП 5, управляющим выходом подключенного к входу запи- . си первого регистра 6, четвертому входу первого элемента И 17 и входу записи блока 25 памяти, вход считывания которого связан управляющим выходом блока 23 вычислений, а адресный вход - с выходом коммутатора 24, первый вход которого соединен. с выходом блока 23 вычислений,второй вход - с выходом первого счетчика 7 им-, пульсов,а управля1та1ий вход - с выходом первого элемента И 17,при.чем выход 1I вычитания подключен к входу четвертого блока 16 сравнения кодов. Устройство работает следующим образом.. I . В исходном состоянии генератор 1 выключен, регистры 6, 9 и 10, триггеры 8 и 19, счетчик 21, аппаратура блока 23 вьтислений установлены в . О, счетчик 7 установлен в 1, работа счетчиков 7 и21 запрещена уровнем О с прямого выхода триггера 8. Адресный вход блока 25 памяти через коммутатор 24 подключен к выходу счетчика 7. . , , ; При поступлении на второй управляющий вход генератора 1 импульса Старт генератор 1 включается и на второй вход смесителя 3 начинают поступать строб-импульсы. На первый вход смесителя 3 подают входной исследуемый сигнал, и на выходе усилителя-расширителя 4 появляется усиленный расширенный сигнал. По заднему фронту каждого импульса генератора 1 включается АЦП 5. После кончания аналого-цифрового преобразования код выборки поступает на первый вход блока 11 вычитания и на вход регистра 6, в который он записывается по заднему фронту импульса Конец преобразования, поступающего с управляющего выхода АЦП 5. Поскольку выход регистра 6 подключен к второму входу блока 11 вычитания, на выходе последнего и момент действия импульса Конец преобразования имеется разность &U кодов амплитуд, двух следующих подря выборок: записанного в регистре 6 и имеющегося на выходе АЩ1 5. АЦП.5 регистр 6, блок II, элемент И 15, блок 16 и дешифратор 20 образуют схе му выбору начальной грашщы интервала преобразования,в качестве ко- торой используют ёыборку, взятую на монотонно изменяющемся участке первого же расширенного сигнала. Дешифратор 20 необходим для предотвращ ния ложного срабатьгоания элемента И 15 при взягии первой выборки. В момент времени, когда разность ди кодов амплитуд двух следующих подряд выборок превьщгает некоторую наперед заданную величину Л (блок I который осуществляет сравнение вели чин ли и , причем при ди Л ° выходе устанавливается уровень логической ), что является признаком того что последовательно взятые выборки лежат на монотонно изменяющемся участке расширенного сигнала, ка выходе элемента И 15 формируется пе репад уровней О .,.по которому в триггер 19 записьюается знак UU, в регистр 9 начальной границы интвервала преобразования записывае ся код амплитуды иначгшьной выбор в качестве которой принимают выборк код амплитуды которой записан в это момент времени в регистре 6, в регистр 10 записываются коды амплитуд U начальной и и следующей за ней выборок, причем в первый разряд регистра 10 записьгоается выборка с амплитудой U , а во второй - с амплитудой U2 при этом Ги, и п t II lu и если ди и - и О , Ги и tUj и если ди в.и - и О . Управление записью в регистр 10 производится уровнем, поступающим с выхода знакаДи блока II вычитания. Кроме того, перепад уровней на выходе элемента И 15 устанавливает.триггер 8 в 1. При этом уровень 1 с прямого выхода триггера 8 разрешает ра-г боту счетчиков 7 и 21, а также элемента И 17. Одновременно уровень с инверсного выхода триггера 8 блокиг рует выход смены выбора начальной границы интервала преобразования. Этим заканчивается этап I работы устройства - выбор начальной границы интер- вала преобразования и начинается ц накопления выборок и получения исход ных данньпс для воспройзведения преобразованного сигнала (фиг, 2qjS ). В интервале преобразования счетчик 7 считает число -взятых выборок, равное числу импульсов генератора 1 .По заднему фронту каждого импульса генератора I число в счетчике 7 увеличивается на единицу.. В это же время производится запуск АЦП 5 После окончания аналого-цифрового , преобразования на управляющем выходе АЦП 5 появляется импульс Конец преобразования, который своим передним фронтом записывает в бдок 25 памяти код выборки из регистра 6 в ячейку с адресом, определяемым состоянием счетчика 7, а задним фройтом производит запись в регистр 6 ; кода очередной выборки. Имеющего в это время на выходе АЦП 5. Таким образом, в ячейки бЛока 25 памяти с номерами (адресами ) i 1,2... будут поочередно записаны коды выборок с амплитудами U , U и следующих за ними в порядке поступления Регистр 10, блоки П, 13, 14 и : 18, триггер 19, счетчик 21 и Элемент И 22 образуют схему для подсчета числа расширенных сигналов в интервале преобразования. В основу работы этой схемы положен тот факт, что взятие выборки с амплитудой , , попадающей в интервал между амплитудами U и Ug и принадле жащей монотонно изменяющемуся участку расширенного сигнала с тем же наклоном (знаком 6 и, ), что и уучастка,на котором были взйты выборки с амплитудами Ц означает, что эта выборка принадлежит новому расширенному сигналу (фиг. 26). Подсчитав в интервале преобразования число выборок, удовлет воряющих вьщ1еназванным условиям, определяют число расширенных сигналов. Как уже указывалось, в регистре 10 хранятся коды выборок с амплитудами Ujj и Uj . Блок 13 сравнения кодов проверяет условие U 9 вьтолнении этого условия на его выходе появляется уровень 1. На выходе блока 14 уровень 1 появляется в случае, если U . U . Если знаки А.и к&и - и. -и. совпадают, на выходе блока 18 совпадений также йоявляется уровень 1. При одновременном поя1влении на входах элемента И 22 уровней 1 на его выходе появляется перепад уровней О по которому в счетчик 21 числа расти ренных сигналов в интервале преобразования добавляется 1. J Предлагаемое устройство работает до тех пор, пока выборки одного из следующих за первым расширенных сиг налов не станут попадать в те же места входного исследуемого сигнала что и выборки, по которым получен первый расширенный сигнал, т.е. поступление новой информации о форме исследуемого сигнала прекратится. Таким образом, признаком конца интервала преобразования является получение выборки с амплитудой Ujj Uj принадлежащей монотонно изменяющему;ся участку входного сигнала (копией которого ябляется расширенный сигнал с таким наклоном, что знак uUjj 0(1 + 4 - Uj совпадает со знаком &U. Условие Uji и проверяет блок 12 сравнения кодов, сЪвпадение 3rfa ков ли и uUjj проверяет блок 18, При вьтолнении вышеназванных условий на выходе элемента И 17 появляется перепад уровней О - 1, по которому выключается генератор 1, триггер 8 устанавливается в О, коммутатор 24 подключает адресный вход блока 25 памяти к выходу блока 23 вычислений,а также включается алпаратура блока 23 вычислений.В этот момент времени заканчивается этап II работы устройства и начинается этап Ш - воспроизведение преобразованного сигнала. При этом блок 23 вычислений счить вает из счетчика 7 число (N+1 ), где 10 610 N - число периодов 1ц генератора I в интервале преобразования, и из счетчика 21 число Р - число расширенных сигналов в интервале преобразования. По полученным данным N и Р блок 23 производит расчет той ячейки блока 25 памяти, в которой записан код амплитуды выборки, которую необходимо воспроизвести первой: - гЧ -Р где К 0,1 ... такое, что -це лое, i N. Расчитанный адрес t устанавлива- ется на выходе блока 23 и сопровождается импульсом, поступающим с управ.ляющего выхода блока 23 на вход считывания блока 25 памяти. При этом на выходе блока 25 появляется код пер- вой выборки преобразованного сигнала. Затем блок 23 вычислений производит расчет адресов ячеек блока 25 памяти по формуле . m Р-:-у где m 2,3,. .., N, К 0,1,... такое число, что - - целое, N . Каждый рассчитанный адрес через коммутатор 24 поступает на адресный вход блока 25 памяти и также сопров.ождается импульсом считывания. В результате на выходе блока 25 поочередно появляются коды выборок, формирующие преобразованный сигнал, верно отображающий форму входного исследуемого сигнала (фиг. 2г ). Для повторного воспроизведения преобразованного сигнала достаточно после расчета адреса произвести повторньй запуск блока 23 вычислений. Для автоматического возобновления работы устройства достаточно после расчета адреса «, подать импульс на установку аппаратуры устройства в исходное состояние в шину Старт. Предлагаемое устройство позволяет уменьшить время получения преобразованного сигнала путем исключения этапа расстановки выборок. Стар/77

Фиг.1 ВыхоВ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой стробоскопический преобразователь электрических сигналов | 1979 |

|

SU864136A1 |

| Насос | 1917 |

|

SU13A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР пр заявке № 3311360/18-21, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| , | |||

Авторы

Даты

1984-04-23—Публикация

1983-02-15—Подача