входами третьего и шестого элементов И второй группы, группы выходов первого и второго запоминающих блоков соединены соответственно с группами входов первого и второго регистров, первый и второй выходы блока формирования номера коммутации соединены с разрешающими входами соответственно нечетных и четных триггеров вто-. рой группы, -i-и нечетный ( i 1...п, где п - число входов коммутации) выход первого дешифратора соединен с

.входами установки в 1 i-ro и (i+l)-ro триггеров второй группы, -й четный выход первого дешифратора соединен с входами установки в О с 1-го и ( f-l)-ro триггеров второй группы, выходы триггеров второй,, первой и третьей групп соединены соответственно с управляющиг и входами первого, второго и третьего узлов электронных ключей, входы коммутируемых сигналов первого узла электронны ключей являются входами коммутируемьк сигналов устройства, выходы первого узла электронных ключей соединены с входами промежуточной линии второго узла электронных ключей, выходы кото

рого соединены с входами промежуточной линии третьего узла электронных ключей, выходы которого являются выходами коммутации устройства, группы входов первого и второго дешифратора соединены соответственно с группами выходов программного блока и второго регистра, пятый выход первого дешифратора соединен с первым входом схемы сравнения, второй вход которой является входом признака устройства, выход схемы сравнения является вторым выходом устройства, первый и второй выходы блока формирования, номера регистра соединены соответственно с разрешающими входами нечетных и четных триггеров третьей группы, i-и нечетный выход (,..| и,М - число выходов коммутации) второго дешифратора соединен с входами установки в 1 i-ro и (i+l)-ro триггеров третьей группы, л-й четный выход второго дешифратора соединен с входами установки в О i-ro и (t-l)-ro триггеров третьей группы, группа выходов блока формирования номера коммутации 1оединена с группой входов блока формирования номера регистра, третий выход которого и третьи выходы блока формирования номера стека, блока формирования номер

коммутации и четвертьш выход блока формирования номера разряда регистра являются соответственно с третьего по шестой выходами устройства, первый выход первого шифратора блока управления соединен с первыми входами блоков формирования номеров регистра, разряда регистра и коммутации, четвертый и пятый выходы первого шифратора блока управления соединены с третьим и четвертым входами программного блока соответственно, пятый вход которого соединен с первым выходом второго шифратора блока управления, второй, третий и четвертый выходы которого соединены соответственно с вторыми входами блоков формирования номеров коммутации, разряда регистра и регистра, с шестого по двенадцатый выходы первого шифратора блока управления соединены соответственно с третьим входом блока фомирования номера коммутации, с входо первого запоминающего блока, с третьим входом блока формирования номера регистра, с выходом невозможности установления соединений устройства, с третьим входом блока формирования номера разряда регистра, с входом второго запоминающего блока и с входом второго регистра, а в блоке управления управляющие входы первого и второго шифраторов, дешифратора и элемента И соединены с управляющими входами коммутатора, выходы первого шифратора соединены с входами третьего шифратора, группа выходов которого соединена с группой входов первого регистра, группа выходов которого соединена с группой входов элемента И, группа выходов которого сое динена с группой входов второго регистра, группа выходов которого соединена с группой информационных входов дешифратора, грзшпа выходов которого соединена с группами информационных входов первого и второго шиф раторов.

2. Устройство по п. 1, отличающееся тем, что блок форми рования номера стека содержит схему сравнения, счетчик и дешифратор, выходы которого являются первым и вторым выходами блока, группа входов дешифратора соединена с первой группой выходов счетчика, вторая группа выходов которого соединена с группой входов схемьь сравнения, выход кото рой соединен с третьим выходом блока.

первый и второй входы которого соединены соответственно с входом сброса и счетным входом счетчика.

3.Устройство по п. 1, отличающееся тем, что блок формирования номера коммутации содержит счетчик, схему сравнения и дешифратор, выходы которого являются первым и вторым выходами блока, первая группа выходов .счетчика соединена с группой входов дешифратора и группой выходов блока, первый, второй и третий входы которого соединены соответственно с первым и вторым входами сброса и со счетным входом счетчика, вторая группа выходов которого соединена с группой входов схемы сравнения выход которой соединен с третьим выходом блока.

4.Устройство по п. 1, о т л и чающееся тем, что блок формирования номера разряда регистра содержит счетчик, схек(у сравнения и дешифратор, выход которого соедашен с первым, вторым и третьим выходами

--блока, группа входов дешифратора соединена- с первой груцпой выходов счетчика, вторая груйпа выходо которого соединена с группой входов схемы. i сравнения, выход которой соединен с четвертым выходом блока, первый, второй и третий входы блока соединены соответствеяио с входом сброса и с первым и вторым счетными входами счетчика.

5.Устройство по п. 1, о т л и чающееся тем, что блок формирования иомера регистра содержит схему сравнения, счетчик и дешифратор, выходы которого соединены с.первым и вторым выходами блока, третий выход которого соединен с выходом схемы сравнения, группа.входов которой соединена с группой выходов счет|Чика и с группой входов дешифра тора, группа информационных входов счетчика соединена с группой входов блока, первый, второй и третий входы которого соединены соответственно с входом сброса, управляющим входом и счётным входом счетчика.

6. Устройство по п. 1, о т л и чающееся тем, что программный блок содержит четьфе элемента И, две стековые памяти и регистр стека, группавыходов которого является группой выходов блока, вход считывания регистра стека соединен с третьим входом блока, группа информационных входов регистра стека соединена с выходами первой и второй стековйх памятей, входы сдвига которых соединены соответствеиио с выходами первого и второго элементов И, nepBi входы которых соедияешд с четвертым входом блока, первый вяод блока соединен с вторым входом первого элемента И и первым входом третьего элемента И, второй вход блока соединен с вторым входом второго и первым входом четвертого элемента И, пятый вход блока соединен с вторыми входами третьего и четвертого элементов И, входы которых соединены соответственно с информационными входами первой и второй стековых памятей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разбиения графа на подграфы | 1982 |

|

SU1086434A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

I. УСТРОЙСТВО ДЛЯ ПГОГРАММНОГО УПРАВЛЕНИЯ, содержащее програм мный блок, дйа запоминающих блока И элемент ИЛИ, отличающееС я тем, что, с целью расширения функциональных возможностей за счет осуществления коммутации по комбинации, в него введены блок формирования номера стекла, два дешифратора, схема сравнения, три узла электронных ключей, три группы триггеров, две группы элементов И, блок регистров, блок формирования номера разряда регистра, два регистра, блок формирования номера коммутации, блок формирования номера регистра и блок управления, содержащий три шифратора, дешифратор, два регистра и элемент И, причем первый и второй входы блока формирования номера стека соединены соответственно с первым и вторым выходами первого шифратора блока управления, входы установки в 1 триггеров первой группы соединены с первым выходом блока формирования номера стека и с первым входом программного блока,.второй вход которого соединен с вторым выходом блока формирования VJ, ,..-,, |. -li, .. .г. чл.,. iKiitMtiii-cfA номера стека и с входами установки в О триггеров первой группы, разрешающие входы которых соединены с соответствующими разрядными выходами блока регистров и с первыми входами элементов И первой группы, первые входы элементов .И второй группы соединены с третьим выходом первого шифратора блока управления, вторые входы элементов И первой половины первой и второй групп соединены с первым выходом блока формирования номера регистра, второй выход которого соединен с вторыми входами элементов И второй половины первой и второй групп, выходы элементов И первой группы соединены с соответствующими входами элемента ИЛИ, выход которого является (Л первым выходом устройства, выходы с: элементов И второй группы соединены с соответствующими входами блока регистров, первый выход блока формирования номера разряда регистра соединен с третьими входами первых и четвертых элементов И первой и второй групп, 00 второй выход блока формирования номера разряда регистра соединен с третьи :о ми входами вторых и пятых элементов И первой и второй групп, третий о ход блок формирования номера разряда регистра -соединен с третьими входами третьих и шестых элементов И первой и второй групп, первый разрядный выход первого регистра соединен с четвертыми входами первого и чет-вертого элементов И второй группы, второй разрядный выход первого регистра соединен с четвертыми входами второго и пятого элементов И второй группы, третий разрядный выход первого регистра соединен с четвертыми

Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных сетей, специализированных вычислительных структур и коммутаторов связи.

Известны коммутаторы и устройству управления ключами коммутаторов пpи кодовом избирании коьв утируемого Kai нала, содержащие регистр, дешифратор и натрещу управляющих триггеров fl

Недостатком этих устройств являются ограниченные возможности. Устройства не могут быть мтрименены при числе точек коммутации более 50-100,

так как резко возрастает число триггеров управления в матрице.

При числе точек коммутации более 100 применяются трехзвенные коммутационные поля со специальными автома. управления.

Наиболее близким к изобретению является коммутатор, состоящий из программного блока, датчика коммутируемых сигналов, приемного блока, элементов ИЛИ, запоминающих устройст регистра сдвига, счетчика С 23. Недостатком известного устройстве являются узкие функциональные возможности коммутации только бинарных двоичных)сигналов, невозможностью коммутации одного л-го входа одновременно с несколькими выходами. Целью изобретения является расширение функциональных возможностей коммутатора за счет осуществления коммутации по кодовой комбинации. Поставленная цель достигается тем, что в устройство для программно го управления, содержащее программны блок, два запоминающих блока и элемент ШИ, введены блок формирования номера стека, два дешифратора, схема сравнения, три узла электронных ключей, три группы триггеров, две груп1ш элементов И, блок регистров, блок формирования номера разряда регистру два регистра, блок формирования номера коммутации, блок формирования немера регистр и блок управления, содержащий три шифратора, дешифратор два регистра и элемент И, причем пер аый и второй входы блока формирования номера стека соединены соответCtBeHHo с первым и вторым выходами первого шифратора блока управления, «коды установки в триггеров первой группы соединены с первым выходо блока формирования номера стека и с первым входом программного блока, второй вход которого соединён с вторым выходом блока формирования номера, стека и с входами установки в О триггеров первой группы, разрешающие входы которых соединены с соответствующими разрядными выходами блока регистров и с первьми входами элемен тов И первой группы, первые входы элементов И второй группы соединены с третьим выходом первого шифратора блока управления, вторые входы элементов И. первой половины первой и вт рой групп соединены с первым выходом блока формирования номера регистра, второй выход которого соединен с вто рыми входами элементов И второй поло вины первой и второй групп, выходы элементов И первой группы соединены с соотвстствующимицвходами элемента ИЛИ, выход которого является первым выходом устройства, выходы элементов И рторой группы соединены с -соотвётсп :утощими входами блока регистров, первьй выход блока формирования номера разряда регистра соединен с третьими входами первых и четвертых элементов И первой и второй групп, второй выход блока формирования номера разряда регистра соединен с третьими входами вторых и пятых элементов И первой и второй групп, третий выход блока формирования номе ра разряда регистра соединен с третьими входами третьих и шестых элементов И первой и второй групп, первый разрядный выход первого регистра соединен с четвертыми входами первого и четвертого элементов И второй группы, второй разрядный выход первого регистра соединен с четвертыми входами второго и пятого элементов И второй группы, третий разрядный выход первого регистра соединен с четвертыми входами третьего и шестого элементов И второй группы, группы выходов первого и второго запоминающих блоков соединены соответственно с группами входов первого и второго регистров, первый и второй выходы блока формирования номера коммутации соединены с разрешающими входами соответственно нечетных и четных триггеров второй группы,. 1-й нечетный С i 1...п, где п - число входов коммутации) выход первого дешифратора соединен с входами установки в 1 п-го и ( i +1)-го триггеров второй группы, i-и четный выход первого дешифратора соединен с входами установки в О с i-го и ( i -1)-го триггеров второй группы, выходы триггеров второй, первой и третьей групп соединены соответственно с управляющими входами первого, второго и третьего узлов электронных ключей, входы коммутируемых сигналов первого узла электронных ключей являются входами коммутируемых сигналов устройства, эыходы первого узла электронных ключей соединены с входами промежуточной линии второго узла электронных ключей, выходы которого соединены с входами промежуточной линии третьего узла электронных ключей, выходы которого являются выходами коммутации устройства, группы входов первого и второго дешифратора соединены соответственно с группами выходов программного блока и второго регистра, пятый выход первого дешифратора соединен с первым входом схемы сравнения, второй вход которой является входом признака устройства, выход схемы сравнения является вторым выходом устройства, первый и второй выходы блока формирования номера регистра соединены соответственно с разрешающими входами нечетных и четных триггеров третьей группы, t -и нечетный выход ( 1 1... М , М - число выходов коммутации) второго дешифратора соединен с вх.одами установки в 1 t-ro и ( i+l)-ro триггеров третьей группы, t-и четный выход второго дешифратора, соединен с входами установки в О -го и ( i-l)-ro триггеров, третьей группы, группа вькодов. блока формирования номера коммутации соединена с группой входов блока формирования номера регистра, третий вы-, ход которого и третьи выходы блока формирования номера стека, блока формирования номера коммутации и чет,вер ,тый выход блока формирования номера разряда регистра являются соответственно с третьего по шестой выходами устройства, первый выход первого шифратора .блока управления соединен с первыми входами блоков формирования номеров регистра, разряда регистра и коммутации, четвертый и пятый выходы первого шифратора блока управления соединены с третьим и четвертым входами программного блока соответственно, пятый вход которого соединен с первым вых9дом второго шифратора блока управления, второй, третий и четвертый выходы которого соединены соответственно с вторыми входами блоков формирования номеров коммутации, разряда регистра и регистра с шестого по двенадцатый выходы первого.шифратора блока управления соединены соответственно с третьим входом блока формирования номера коммутации, с входом первого запоминающего блока, с третьим входом блока формирования номера регистра, с выходом невозможности установления соединений устройства, с третьим входом блока формирования номера разряда регистра, с входом второго запоминающего блока и с входом второго регистра, а в блоке управления управляющие входы первого и второго шифраторов дешифратора и элементы И соединены с управляющими входами коммута- тора, выходы первого шифратора соединены с входами третьего шифратора, группа выходов которого соединена с группой входов первого регистра, грзт

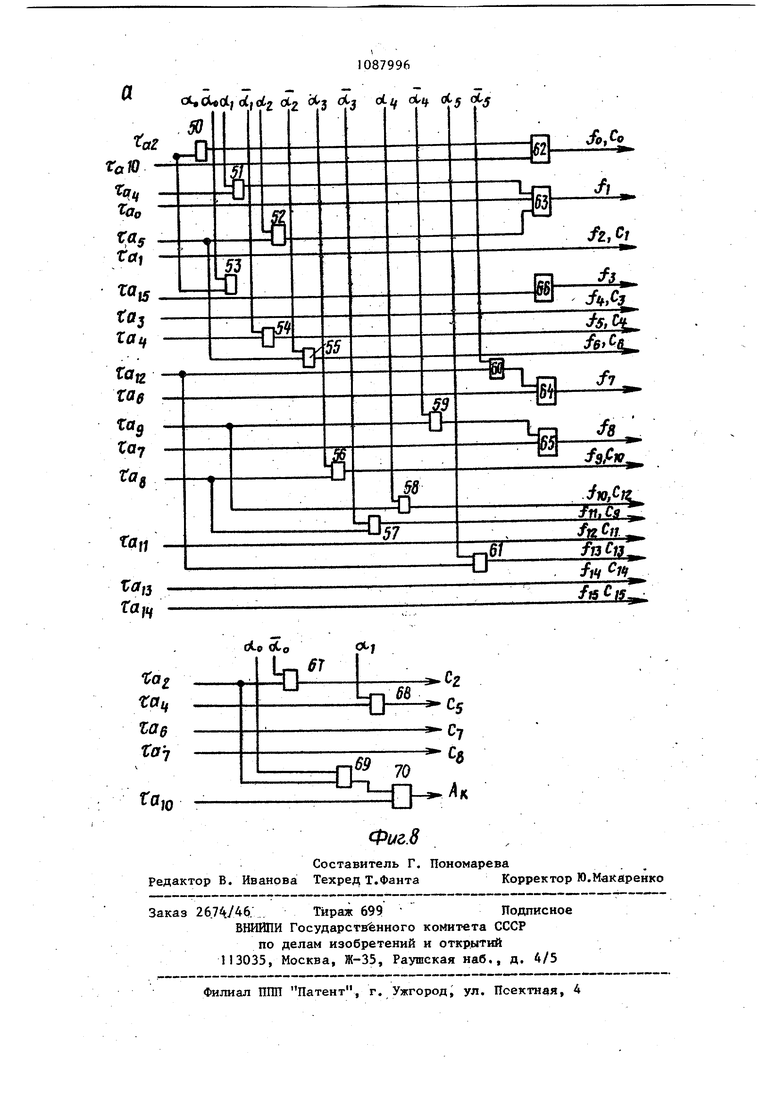

па выходов которого соединена с группой входов элемента И, группа выходов которо.го соеди.нена с группой входов второго регистра, группа выходов которого соединена с группой информационных входов дешифратора, группа выходов которого соединена с группами ннформационньгх входов первого и второго шифраторов.

Блок формирования номера стека содержит схему сравнения, счетчик и дешифратор, выходы которого являются первым и вторым выходами блока, группа входов дешифратора соединена с первой группой выходов счетчика, вторая группа выходов которого соединена с группой входов схемы сравнения, выход которой соединен с третьим выходом блока, первый и второй входы которого соединены соответственно с входом сброса и счетным входом счетчика.,

Блок формирования номера коммутации содержит счетчик, схему сравнения и дешифратор, выходы которого являются первым и вторым выходами блока, первая группа выходов счетчика соединена с группой входов дешифратора и группой выходов блока, первый, второй и третий входы которого соединены соответственно с первым и вторым входами сброса и со счетным входом счетчика, вторая группа выходов которого соединена с группой входов схемь срав нения, выход которой соединен с третьим выходом блока.

Блок формирования номера разряда регистра содержит счетчик, схему срав нения и дешифратор, выход которого соединен с первым, вторым и третьим выходами блока, группа входов дешифратора соединена с первой группой выходов счетчика, вторая группа выходов которого соединена с группой входов схемы сравнения, выход которой соединен с четвертым выходом блока, первый второй и третий входы блока соединены соответственно с входом сброса и с первым и вторым счетными входами счепчика.

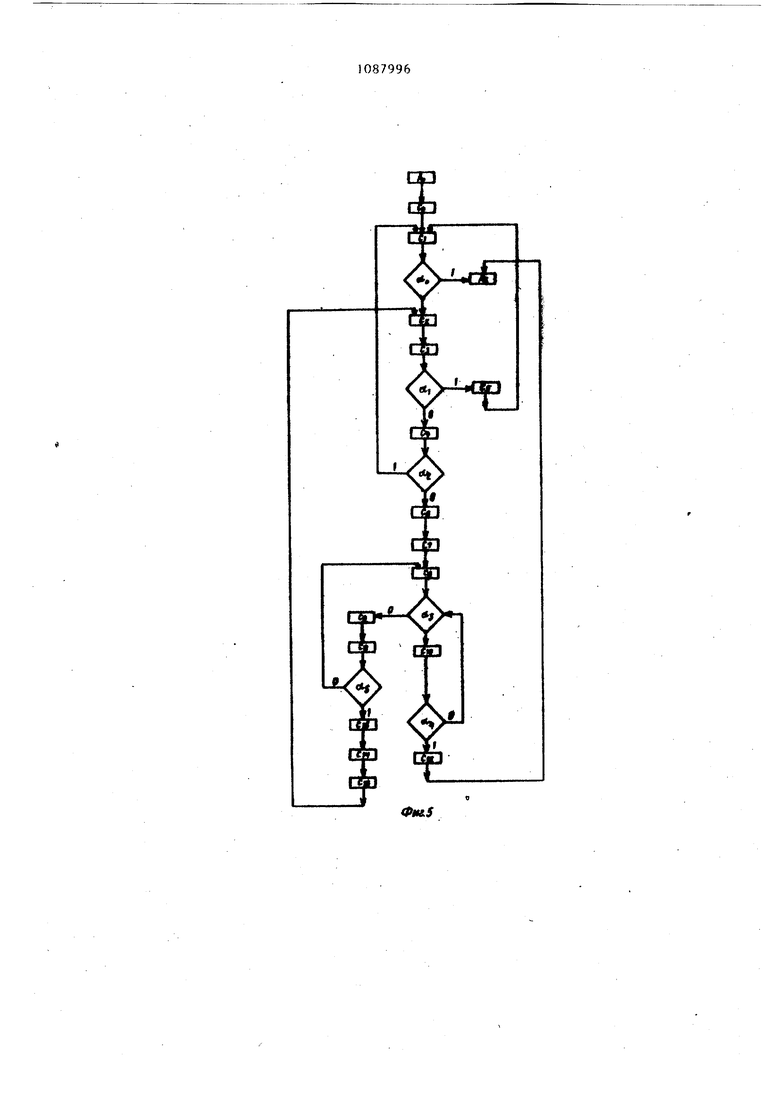

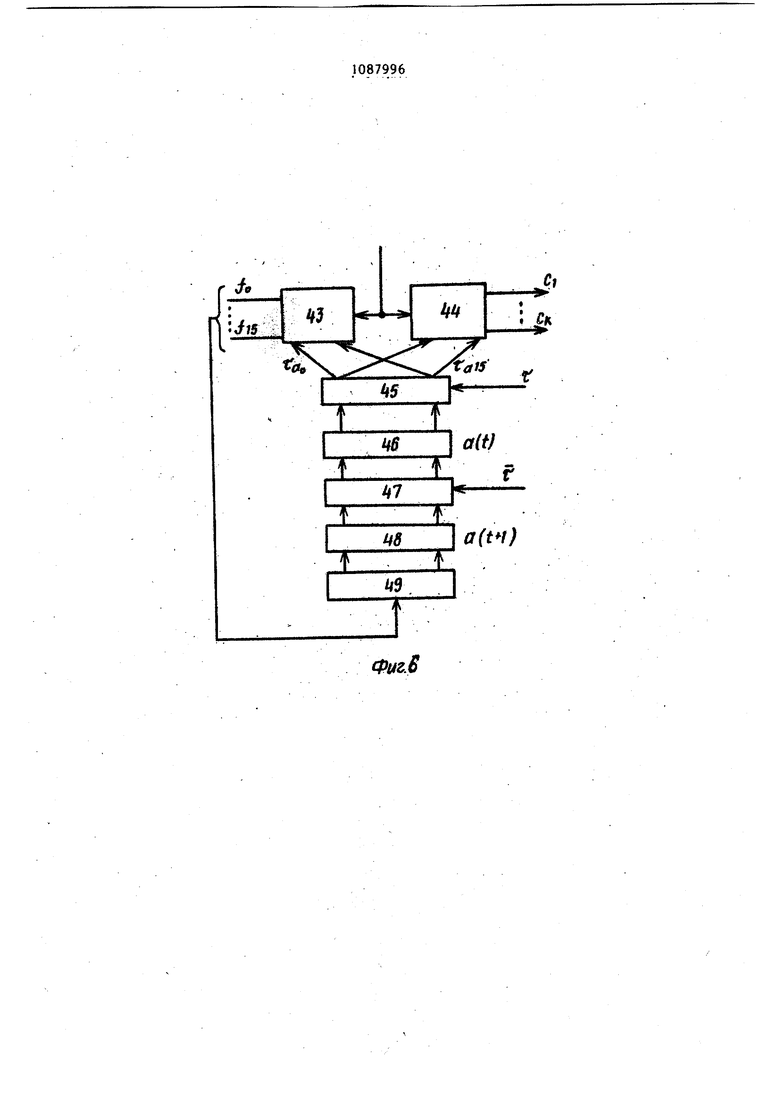

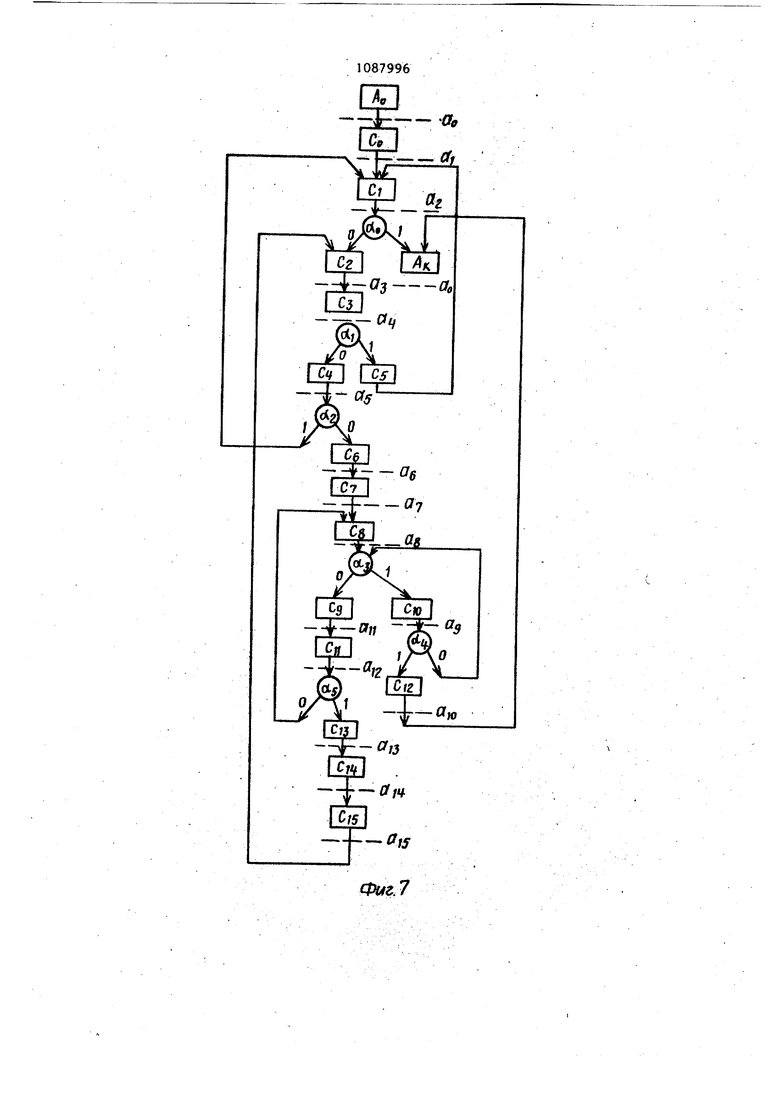

Блок фор.миро&ания номера регистра содержит схему сравнения, счетчик и дешифратор, выходы которого соединены с первым и вторым выходами блока,третий выход которого соединен с выходом схемы, сравнения, группа входов которой соединена с группой выходов счетч.ика и с группой входов дешифратора группа информационных пходов счетчика соединена с группой входов блока, первый, второй и третий входы которого соединены соответственно с входом сброса, управляющим и счетным входами счетчика, Программный блок содержит четыре элемента И, две стековые памяти и ре гистр стека, группа выходов которого является группой выходов блока, вход считывания регистра стека соединен С третьим входом блока, группа инфор мационных входов регистра стека соединена с выходами первой и второй стековых памятей, входы сдвига которых соединены соответственно с вЫходами первого и второго элементов И, первые входы которых соединены с чет вертым входом блока, первый вход бло ка соединен с вторым входом первого элемента И и первым входом третьего элемента И, второй вход блока соединен с вторым входом второго и первым входим четвертого элемента И, пятый вход блока соединен с вторыми входами третьего и четвертого элементов И выходы которых соединены соответственно с информационными входами первой и второй стековых памятей. Блок регистров служит для хранени результатов предыдущих соединений. Разнарядность регистров блока равна количеству блоков третьего электронных ключей, а их количество - количеству блоков второго узла электронных ключей. Первая группа элементов И и элемент ИЛИ определяют состояние регист ров блока, т.е. было ли осуществлено соединение через проверяемую промежу точную линию от блоков второго узла электронных ключей к блокам третьего узла. Группы триггеров управляют электронными ключами. Предполагается, что в исполнительной части коммутатора, в блоках первого, второго и третьего узлов электронных ключей предусмотрены электронные ключи для каждой точки коммутации. Причем при занятии промежуточной линии эта линия не должна больше заниматься, . должна быть заблокирована. С этой целью для каждой промежуточной линии преду .смотрены несколько триггеров, количество которых от числа входов в каждый узел электронных ютю- чей. При выборе испол}тительной части коммутатора предполагается, что трех звбнная коммутационная схема должна быть неблокируемой, т.е. удовлетворять следующему условию Г2 г,,/ (г,-1), где г.- - количество блоков второго . узла электронных ключей; г - количество входов в каждый блок первого узла электронных ключей; jp - максимальное число вькодов соединяемых одновременно с заданными входом. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема исполнительной части устройства; на фиг. 3 - пример таблицы требований на соединение А; на фиг. 4 - пример нахождения матрицы Т по матрице А; на фиг. 5 - алгоритм работы устройства; на фиг. 6 - блок-схема блока управления; на фиг. 7 - граф-схема алгоритма управления с разметкой состояний; на фиг. 8 - блок-схемы первого и второго шифраторов блока управления. , Устройство содержит блок 1 формирования номера стека, программный блок 2, первый дешифратор 3, вторую группу триггеров 4, схему 5 сравнения, первый узел 6 электронньк ключей, блок 7 формирования номера коммута1щи, второй узел 8 электронных ключей, первую группу триггеров 9, вторую группу элементов И 10, первую группу элементов 11, первое запоминающее устройство 12, блок 13 формирования регистра, камеру разряда регистра, блок 14 формирования номера регистра, второй запоминающий блок 15, второй дешифратор I6-, третью группу триггеров 17, третий узел 18 электронных ключей, блок 19 управления, блок 20 регистров, эле мент 21, первый регистр 22, второй регистр 23. Блок 2 содержит элемент И 24, стековую память 25 и 26, регистр 27 стека, элементы И 28-30. Блок 1 содержит схему 31 сравнения, счетчик 32 и дешифратор 33. Блок 13 содержит дешифратор 34, счетчик 35 и схему 36 сравнения. БлоЛ 14 содержит дешифратор 37, счетчик 38 и схему 39 сравнения. Блок 7 содержит схему 40 сравнения, счетчик 41 и дешифратор 42. Блок 19 управления содержит (фиг.6) первый и второй шифраторы 43 и 44, депшфратор 45, второй регистр 46, элемент И 47, первый регистр 48, третий шифратор 49, Первый шифратор (фиг. 8) содержит 9леме:нть И 50-61, элементы ИЛИ 62-65 и элемент НЕ 66. Второй шифратор содержит элементы И 67-69 и элемент ИЛИ 70. На фиг. 2 показана исполиительная часть устройства, где S - количество блоков первого узла электронных ключей; г - количество входов в/ каждый блок первого узла электронных ключей; г - количество блоков второго узла 8; S количество блоков третьего узла 18; г- - количество выходов от каждого блока третьего узла 18; I - общее число коммутируемых входов; L - общее число выходов; о - максимальное число выходов, соединяемых одновременно с заданным вхо дом. На фиг. 3 показан пример таблицы требований А |f а f |( , где А - матрицы требованр(й на соединение; а элемент в матрице А; i - номер входа ( 1 1,2.,.); - номер выхода ( 8 1,2...L). Матрица дана для трехзвенного ком мутатора с параметрами: Sj,3, , ,.., , , г -2, 12, f 2. На фиг. 4 дан пример нахождения матрицы 1 jf/t j/f по матрице где Т - преобразованная матрица, в которой каждому i-му входу сопостав лен определенный выходной j-и блок третьего узла 18 электронных ключей (1 1,2,...,; j l.,2j...,S2); t элемент в матрице. На фиг. 5 .дан алгоритм работы устройства, приведенного на фиг. 1, где АО - начало вьтолнения микрооперации; GO - установка всех счетчиков в С., - плюс 1 на счетчик 32 (, где, п - состояние счетчика 32) проверка состояния счетчика 32 (п.3)7,где S - количество блоков первого узла 6); С - считьгоание инЧ формации из стека; Сз считывание из регистра стека в дешифратор 3; оС - - проверка на признак г, где г признак окончания списка соединений в стеке; Сц, - плюс 1 к счетчику 41 (, где m - состояние счетчика 32) - проверка условия: все ли жуточные линии от блока первого узла 6 к блоку второго узла 8 заняты ( , где Гл количество промежуточных линий от каждого блока первого узла 6 к второму, равное количест ву блоков второго узла 8); Gj - сбро счетчика 29 в О (); G, - считывание из запоминающего устройства 12 в регистр; G i - плюс I к счетчику35 (, где g - состояние счетчика 35); перенос содержимого счетчика 29 в счетчик 38 ( где Z - содержимое счетчика 38); ctg - проверка наличия 1 в соответствугацем j-м разряде р-го регистра блока, где р количество регистров блокаjравное количеству блоков второго 8, G - считывание информации- из регистра 22 в соответствующ1й j-й разряд р-го регистра блока; - плюс 1 к счетчику 38 (); G; - плюс 1 к счетчику 35 ( G - сигнализация о невозможности установления соединений; G - считывание из запоминающего блока 15 в регистр 23; G . считывание из регистра в дешифратор 16; С j - сдвиг в стеке; - проверка условия, все ли регистры блока опрошены (); проверка уело ВИЯ, все ли разряды в регистре блока опрошены ( где S количество блоков третьего узла 18); А - конец микрооперации. Устройство работает следукнцим образом. Устройство работает при наличии заданной таблицы требований на соединение А //а; 8// , которая размещается в.датчике 2, Блок 2 состоит из стековой памяти, причем число стеков равно числу блоков первого (S) y-wia 6. Число регистров в стеке равно Г: + 1, где г- - число входов в каждый блок первого узла 6. В регистрах хранятся номера входов, подлежащих коммутации, и в дополнительном регистре - признак окончания списка соответствующего стека (г). Блок 1 по команде из блока 19 выдает номер стека в блок 2, из которого информация считывается в дешифратор 3. Дешифратор 3 указывает номер входа, подлезкащий коммутации. GxeMa 5 сравнения проверяет наличие признака г. Если признак г есть, то считывается информация со следующего стека. Блок 7 указьшает номер промежуточной линии от первого узла 6 к второму узлу 8, причем занятие начинает по порядку с первой линии. В зависимости от номера коммутируемого входа и номера промежуточной линии устанавливается в 1 соответствующий триггер 4 группы, который открывает электронный ключ узла 6, т.е. заданный вход комму тации соединяется через промежуточну линию к уэлу 8.1 Блок 13 устанавливает номер прове ряемого разряда регистра блока 20, н чиная с первого. Блок 14 устанавлива ет номер регистра -блока 20 в зависимости от состояния счетчика в блоке 7. Группа элементов II и элемент ШШ 21 определяет наличие 1 в разряде регистра блока 20, т.е. определяет, было ли ранее установлено соединение. Если соединения не было, т считывается информация из запоминающего устройства 12 в заданный регист блока 20. При этом устанавливается в I соответствунщийг триггер 9 группы и открывает электронный ключ узла 8. В запоминающем устройстве 12 записана матрица , Эта матрица преобразована из матрицы требований А /(а; в// , где каждому 1 -му входу из матрицы А сопоставлен определенный выходной j-и коммутатор. Таким образом, заданный коммутируемый вход соединен через первый 6 и второй 8 узлы к третьему узлу 18. Запоминающий блок 15 по сигналу из блока 19 выдает информацию о выходах, подлежа щих соединению с заданным входом, де шифратору 16. Информация о соединяемых выходах задана в запоминающем устройстве таблицей требований С//. Дешифратор 16 устанавлива ет соответствующие триггеры группы 17 в 1, при этом открываются элект ронные ключи узла 18. Заданный вход коммутации соединен с требуеьвлми выходами коммутации. Если же при прове ке промежуточная линия от второго узла к третьему занята ранее установ ленным соединением, то блок 14 задает следующую промежуточную линию на проверку. Дпя сокращения описания рассмотри трехзвенный коммутатор, с параметрами 9. Ч 4 ч Ч -i, J- Г| -л f ) По сигналу СО и блока 19 все счет чики блоков 1,7,13 и 14 устанавливаются в О. По сигналу С1 счетчик 02 устанавливается в 1. При этом дешифратор 33 указывает номер стека, с которого считывается информация о но мере выхода, подлежащего коммутации. При этом схема срадрения 31 вьиает условие Если Ыо т.е. nySif состояние счетчика 32 больше числа стеков (т.е. весь список на соединение исчерпан), тогда конец работы Ац. Если , т.е. список не исчерпан (), тогда по сигна лу С2 считывается информадая из вершины первого стека 25 в регистр 27 стека. Далее по сигналу СЗ считывается информация из регистра 27 стека в дешифратор 3. Деошфратор 3 указывает номер входа, подлежащий коммутации. При этом повторяется условие наличия признака г, где г - признак конца списка соединений в стеке, весь список в стеке исчерпан и тогда по сигналу С5 обнуляется счетчик 41 н блок 19 выдает сигнал перехода к следующему стеку, ot 0 - в стеке с имеются входы, подлежащие коммутаций, и по сигналу С4 счетчик 41 устанавливается в единичное состояние. При этом дешифратор 42 указывает номер занимаемой промежуточной линии от первого узла ко второму. При этом в зависимости от номера входа, подлежащего коммутации, и от номера промежуточной линии устанавливается в 1 соответствующий триггер группы 4. Единичный выход триггера открывает соответствующий электронный ключ первого. узла 6. Что0ы исключить повторное занятие промежуточной линии,поставлены пары триггеров на одну линию. При ерабатывании одного триггера второй будет заблокирован. Схема сравнения 40 определяет условие об промежуточные (пинии от первого узла к второму для данного стека, а следовательно , и для данного коммутатора первого узла заняты, т.е. проверяет m Tj , где Tg - количество промежуточных линий. Если,, то опрашивается следующий стек, если mxr, т.е. по сигналу С6 производится считывание информации из запоминающего устройства 12 в регистр блока 20. При этом соответственно номеру входа, подлежащего коммутации, из запоминающего устройства 12 считывается информация о номере коммутатора третьего узла 18, через который происходит соединение. Чтобы исключить повторное занятие пpoмeжytoчнoй линии от второго узла 8 к третьему, необходимо прове ритьеена занятость.Занятие промежуточной линии от коммутаторов второго узла 8, также как и от первого начинается с первой линии. Для этого по сигналу С7 устанавливается счетчик 35 в 1, при этом дешифратор 34 указывает номер разряда в регистре блока 20, подлежащего проверке. Проверяем 1310 1-й разряд (§), а следовательно, и первую промежуточную линию от второго узла 8. По сигналу С8 содержимое счет чика 41 переносится в счетчик 38, дешифратор 37 указывает какой регистр блока 20 прове ряется. Так как промезкуточной линией от коммутаторов первого узла 6 ставится в соответствие свой регистр блока 20, то, следовательно, .состояние счетчика 38 должно соответствовать со тояюоЬ. счетчика 41. Условие наличия 1 в регистре блока 20 (что соответствует занятости промежуточной линии от второго узда 8) снимается с элемента ШШ 21, если О, то линия свободна и ее можно занимать, 9 линия занята. При этом определяется возможность установления соеданения через другую, промежуточную линию, для чего по сигналу CIO прибавляется 1 к счетчику 38. В случав свободной линии по сигналу С6 считывается информация из регистра запоминающего устройства 12 в соответствующий j-и разряд р ре гистра.блока 20. При этом в регистр блока 20 записывается О, ecjm соединения к коммутатору третьего узла 18 нет, и 1, если есть соединение/ (в зависимости от таблицы Т). При этом единичное состояние регистра блока 20 устанавливает в соответствующий триггер группы 9, который в свою очередь открывает электронный ключ узла 8. Блокировка промежуточной линии аналогична описанной выше. Далее проверяется следуюпщй разряд регистра блока 20, для чего по сигналу СМ прибавляется 1 к счетчику 35. Схема 36 сравнения определяет условие - все ли разряды оп1 юшены. Если 0. О - не все разряды опрошены, то проверяется заданный регистр блока 20. Если tf-f ( т.е. все разряды опрошены, то по сигналу С13 считывается информация из запоминающего блока 15 в регистр 23. По сигналу С14 из регистра 23 информация считывается в дешифратор 16, При этом дешифратор 16 указывает но6мера выходов, подлежащих соединению с заданным входом. 1 открывает свой триггер группы 17, который отУрывает свои электронные ключи в узле 18 и,таким образом, заданный вход будет соединен с заданными выходами. Если , 4 1 (), т.е. все регистры опрошены и заняты, то выдается сигнал о невозможности установления соединения заданного входа с требуемыми выходами. После установления соединения по сигналу CIS производится сдвиг в стеке и считывает ся следующий номер входа, подлежащий коммутации. предлагаемое устройство обладает широкими функциональными возможностями. В предлагаемом устройстве коммутируемые сигналы могут быть как цифровыми, так и аналоговюш. Структура устройства не меняется, а тип коммутируемых сигналов определяется только физическим принципом реализации точек коьжутация (электронных ключей) в трехзвенном исполнительном устройстве, Если в качестве такого ключа выбран геркои МОП-транзистор, или оптронная пара, то возможна коммутация как аналоговых, так и дискретных сигналов по выбору. Если использовать pin-диоды, и nipin-диоды, элементы с явлением сверхпроводимости (эффект Джозефсона) в качестве электронных ключей, то возможна коммутация сверхвысокочастотных радиосигналов. Кроме того, в известном устройстве осуществляется коммутация входов-выходов по кодовой комбинации, т.е. на 00000tia выходе появляется сигнал 1-го выхода датчика сигналов, на 00001второго выхода и т.д. В известном устройстве принципиально невозможно осуществить неординарную коммутацию, т.е. соединить любой из входов лри какой-либо управляющей кодовой комбинация с несколькими выходами, что ,как видно из вышеприведенного . описания осуществляется в изобретении.

tr,.

,.S,j /,

Фиг.З

J9-12.

Фиг,г

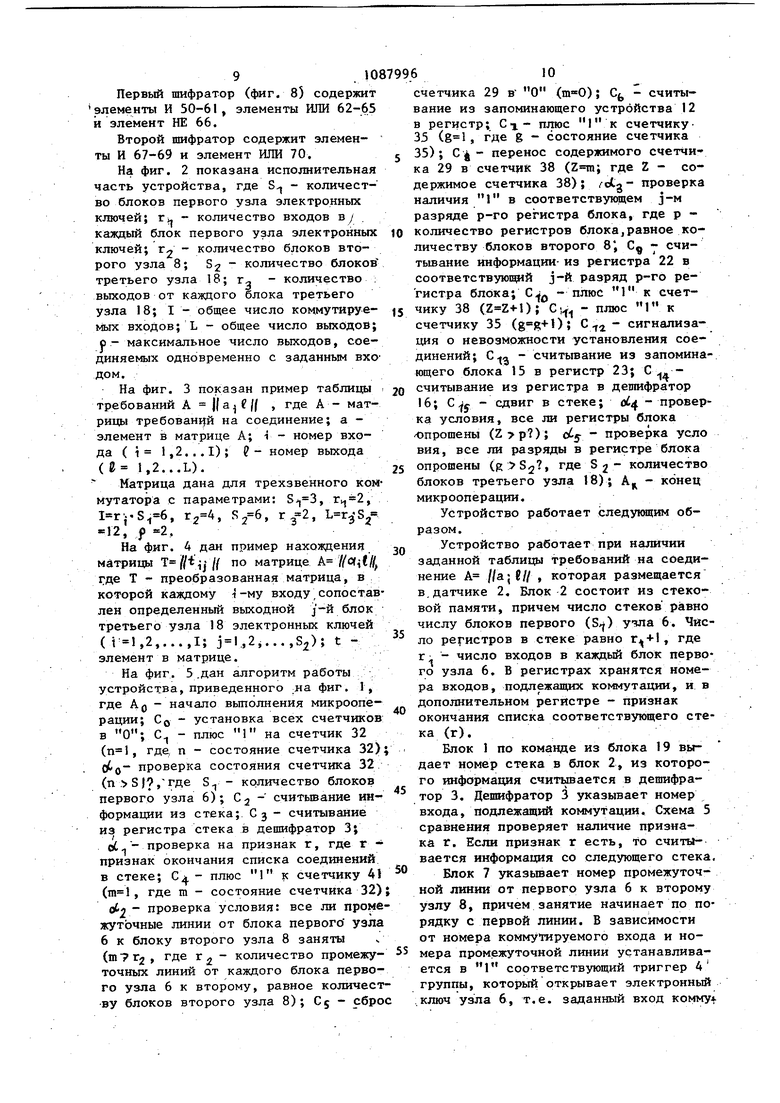

a()

Фиг.6

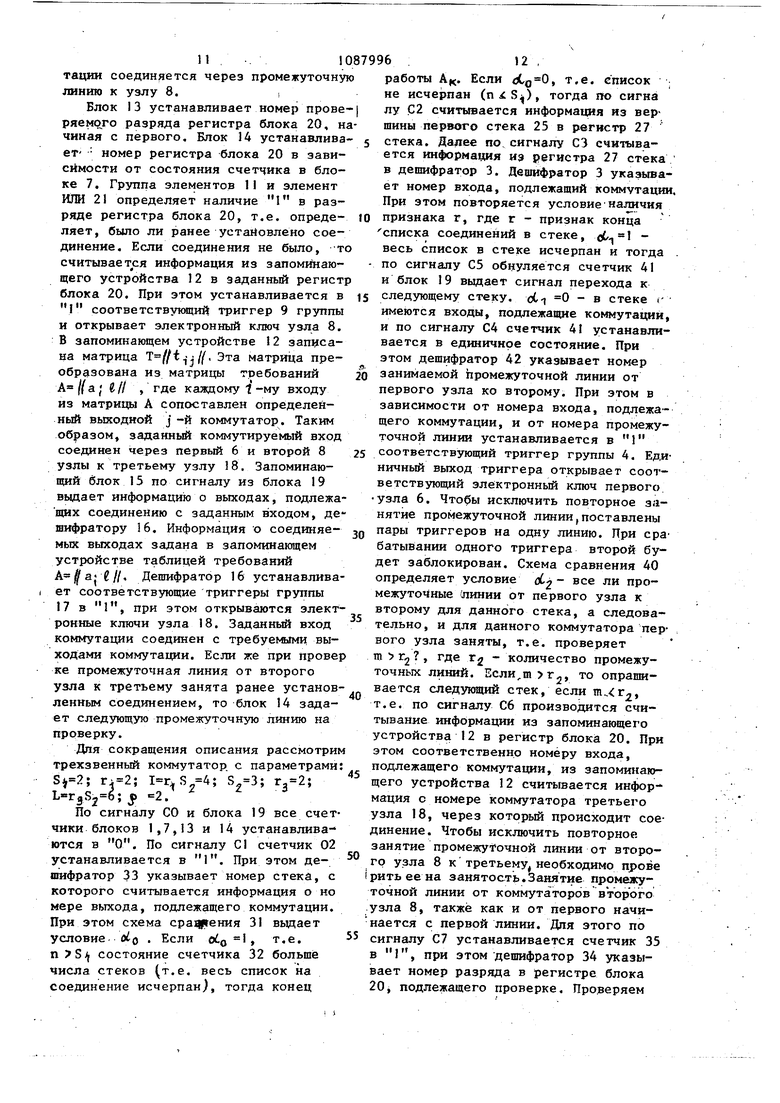

ot(Xeolj o( 04-2 ctj (Xj ot/ tlj oC

tflfj Catf

tOjz

rag flfl

toy tfle

«fT

ra,

cX-o oC(

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авакумов Г.Г | |||

| Электронные промьшшенные устройства | |||

| Киев, Вища школа, 1978, с | |||

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

| , 2 | |||

| Коммутатор | 1978 |

|

SU711566A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-23—Публикация

1982-05-31—Подача