ды селекторов подключены к выходам соответствующих блоков ввода данных,

2. Многоканальное оперативное запоминающее устройство, содержащее накопитель, формирователи адресных токов, усилители считывания, формирователи информационных сигналов, группу элементов ИЛИ, входные и выходные каналы, распределитель сигналов выходных каналов, логический блок, один иэ выходов которого является выходом устройства, выходы элемента И групп подключены к входам соответствующих формирователей адресных токов, выходы которых подк)1ючены к адресньм входам накопителя, выходы распределителя сигналов выходных каналов соединены с входами формирователей информационных сигналов, выходы которых подключены к информационным входам накопителя, выходы которого соединены с входами усилителей счи« тьшания, первый входной канал содержит первый и второй регистры адреса, первый и второй.дешифраторы адреса, выходы которых являются первым и вторым выходами входного канала, и распределитель сигналов, причем выходы первого и второго регистров адреса подключены к входам распределителя сигналов каналов, первые и вторые выходы входных каналов подключены к одним из входов элементов ИЛИ групп, первые входы выходных каналов подключены к выходам усилителей считывания, вторые входы второго и последующих выходных каналов подключены к третьим выходам соответствующих входных каналов, первые выходы выходных каналов подключены к входам распределителя сигналов выходных каналов, о т л и ч а ю. щ е е с я тем, что, с целью расширения области пркмене ния устройства путем обеспечения возможности управления приоритетом его каналов, в него введены переключатели, а в первый входной канал - три группы элементов И, причем выходы первого и второго регистров адреса подключены к первым входам элементов И первой и второй групп, выходы которых соединены с входами первого и второго дешифраторов адреса, выходы распределителя сигналов являются четвертым выходом данного канала и подключены к первым входам элементов И третьей группы, выходы которых являются третьим выходом первого входного канала и подключены к второму входу первого вькодного канала, вторые входы элементов И подключены к треть ему входу первого входного канала, третьи входы и четвертые выходы входных каналов подключены к одним из выводов переключателей, одноименные контакты переключателей соединены между собой и являются другими выводами переключателей подключенными соответственно к шине питания, к входам и другим выходам логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное оперативное запоминающее устройство | 1983 |

|

SU1112406A2 |

| Оперативное запоминающее устройство | 1981 |

|

SU978192A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Устройство для перадачи информации | 1990 |

|

SU1711217A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1994 |

|

RU2127025C1 |

| Устройство для ввода информации | 1987 |

|

SU1474632A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

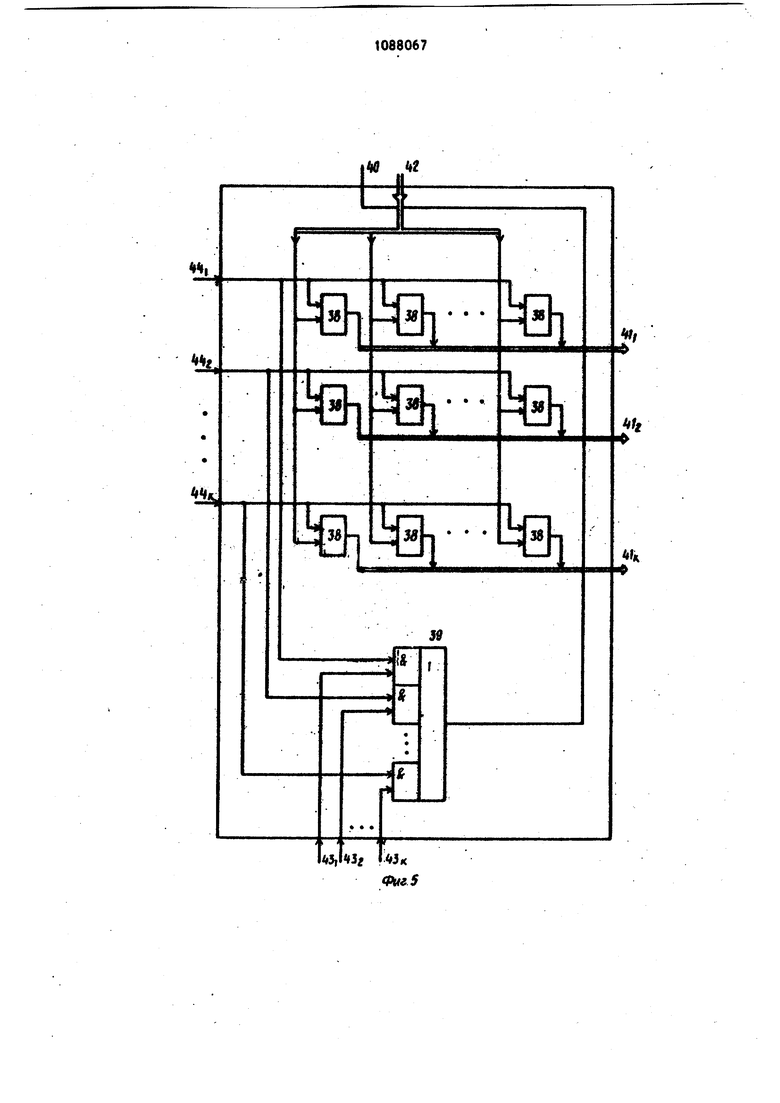

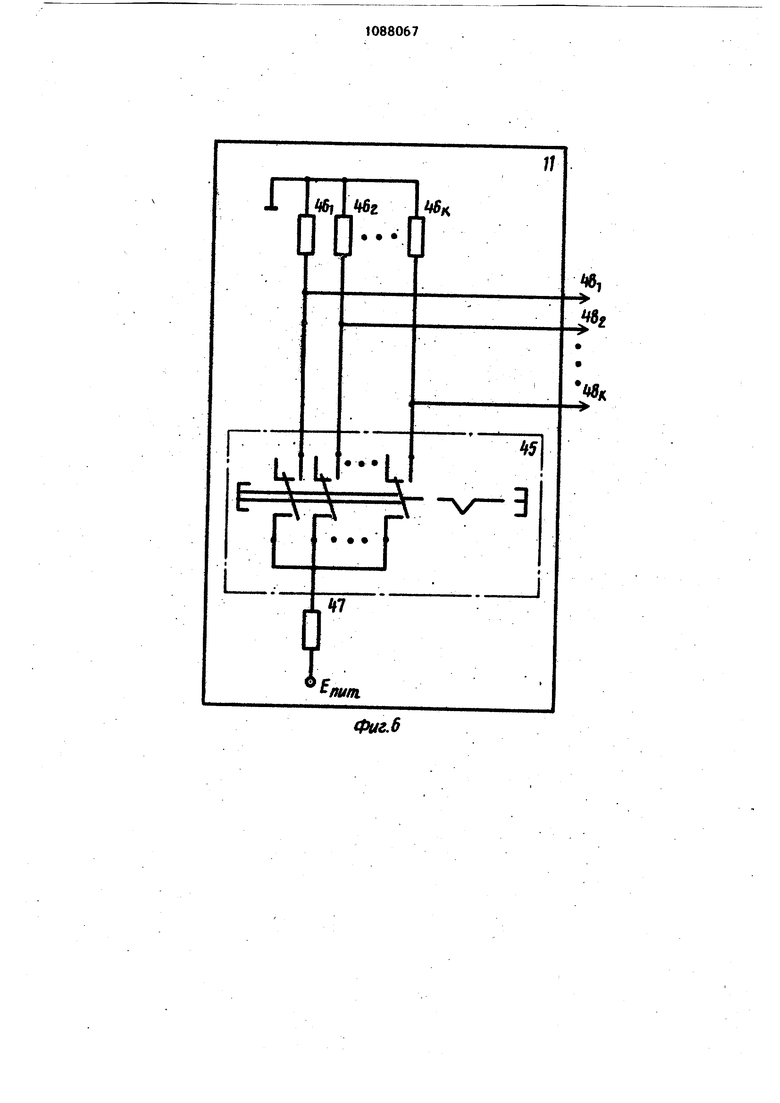

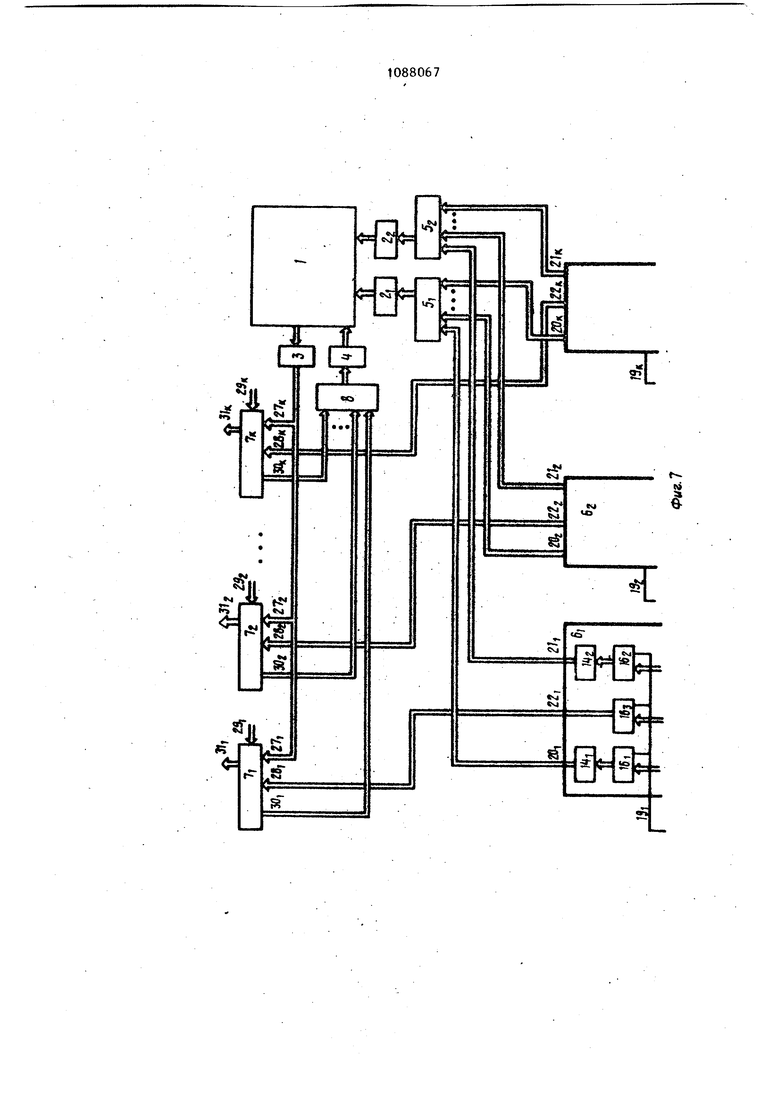

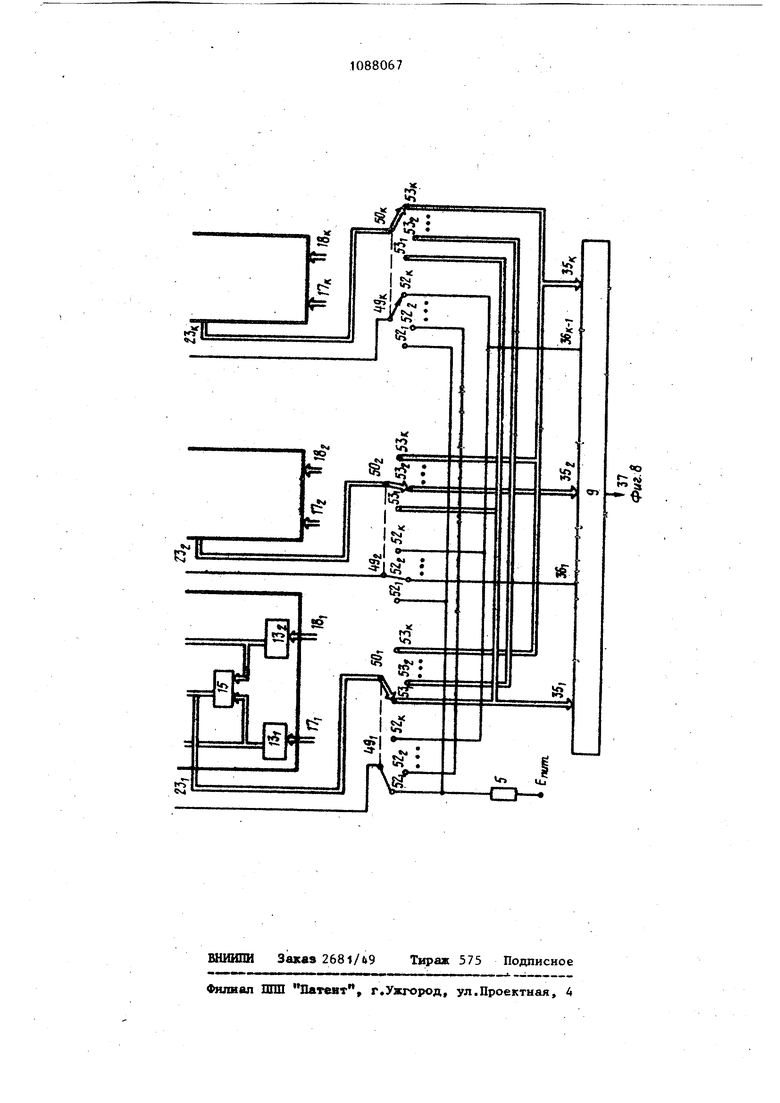

1. Многоканальное оперативное запоминающее устройство, содержащее накопитель, формирователи адресных токов, усилители считывания, формирователи информационных сигналов, группы элементов ИЛИ, входные и выходные каналы, распределитель сигналов выходных каналов, логический блок один из выходов котор ого является выходом устройства, выходы элементов ИЛИ групп подключены к входам соответствующих формирователей адресных токов, выходы которых подключены к адресным входам накопителя, выходы распределителя сигналов выходных каналов соединены с входами формирователей информационных Сигналов, выходы которых подключены к информационным входам накопителя, выходы которого соединены с входами усилителей считывания, первый иходной канал содержит первый и второй регистры адреса, первый и второй дешифраторы адреса, выходы которых являются первым и вторым выходами входного канала, и распределитель сигналов, причем выходы первого и второго регистров адреса подключены к входам распределителя сигналов каналов первые и вторые выходы входных каналов подключены к одним из входов элементов ИЛИ групп, первые входы выходных каналов подключены к выходам усилителей считывания, вторые входы второго и последующих выходных каналов подключены к третьим выходам соответствукяцих входных каналов, первые выходы выходных каналов подключены к входам распределителя сигналов выходных каналов, отличающееся тем, что, с целью расщирения области применения устройства путем обеспечения возможности упт равления приоритетом каналов, в него введены селекторы и блоки ввода данных, а в первый входной канал - три группы элементов И, причем выходы пер вого и второго регистров адреса подключены к первым входам элементов И первой и второй групп, выходы которых соединены с входами первого и второго дешифраторов адреса, выходы рас- пределителя сигналов являются четвер00 00 тым, выходом данного канала и подключены к первым входам элементов И о третьей группы, выходы которых являО) ются третьим выходом первого вход ного канала и подключены к второму входу первого выходного канала, вторые входы элементов И подключены к третьему входу первого входного канала, третьи входы и четвертые выходы входных каналов подключены к первым выходам и первым входам селекторов, вторые выходы селекторов подключены к входам логического блока, другие выходы которого подключены к вторым входам селекторов, третьи вхо

1

Изобретение относится к вычислительной технике и предназначено для использования в многопроцессорных и многомашинных вычислительных системах в качестве общей оперативной памяти,

Известно многоканальное.оперативное запоминающее устройство(Содержащее накопитель, формирователи записи и считывания, адресные и управляющие элементы, ресурсы общей памяти используются несколькими устройствами-потребителями (npoUeccdpaMH ), которые фун|сционируют независимо друг от друга, генерируя об1 ащения

к памяти с целью записи и считывания информации С I П.

Однако данное устройство не обеспечивает возможность одновременного обслуживания хотя бы двух устройствпотребителей.

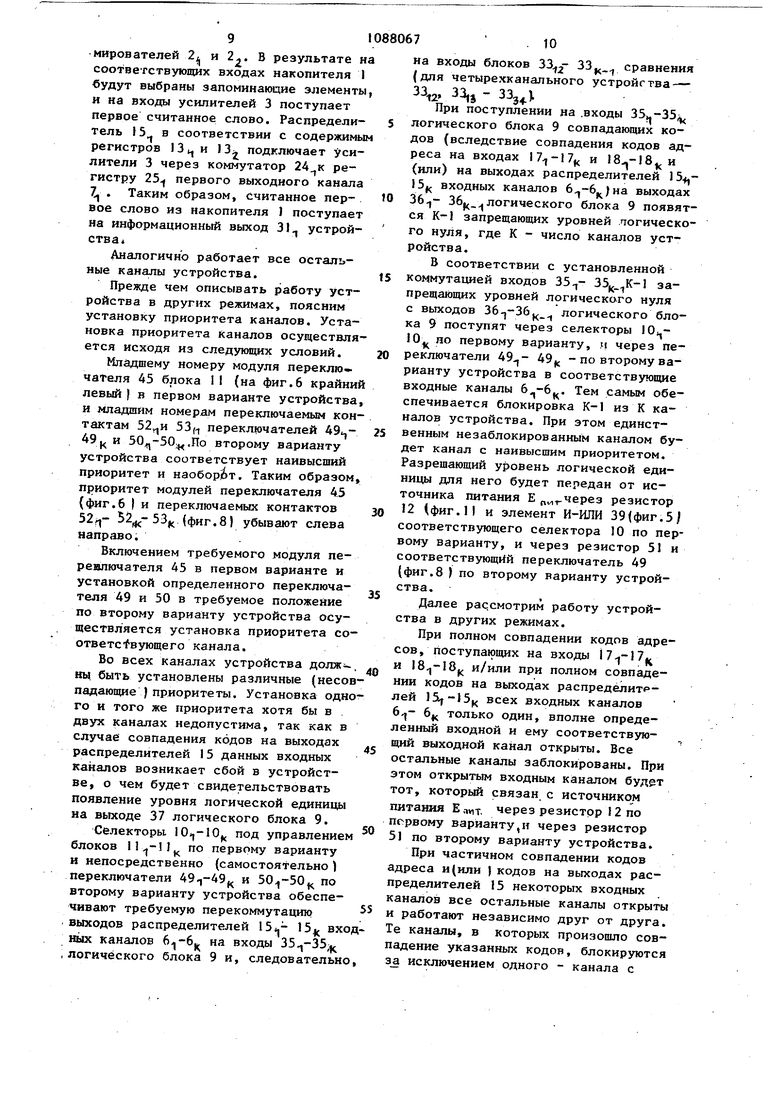

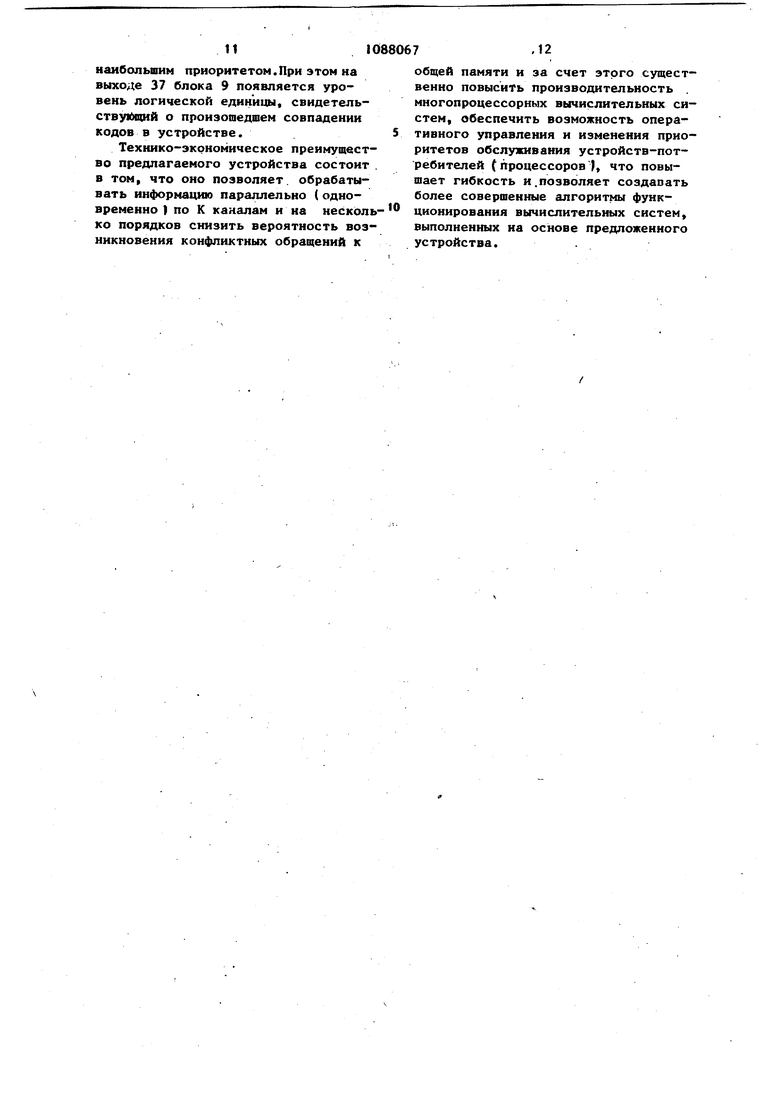

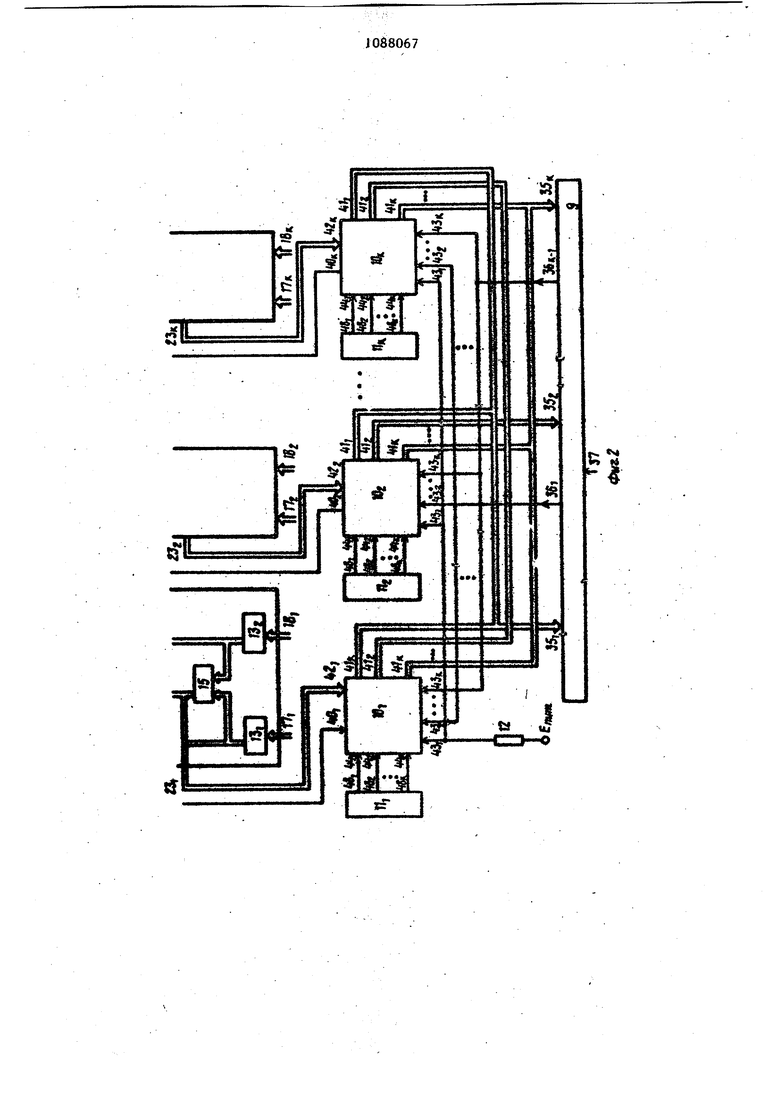

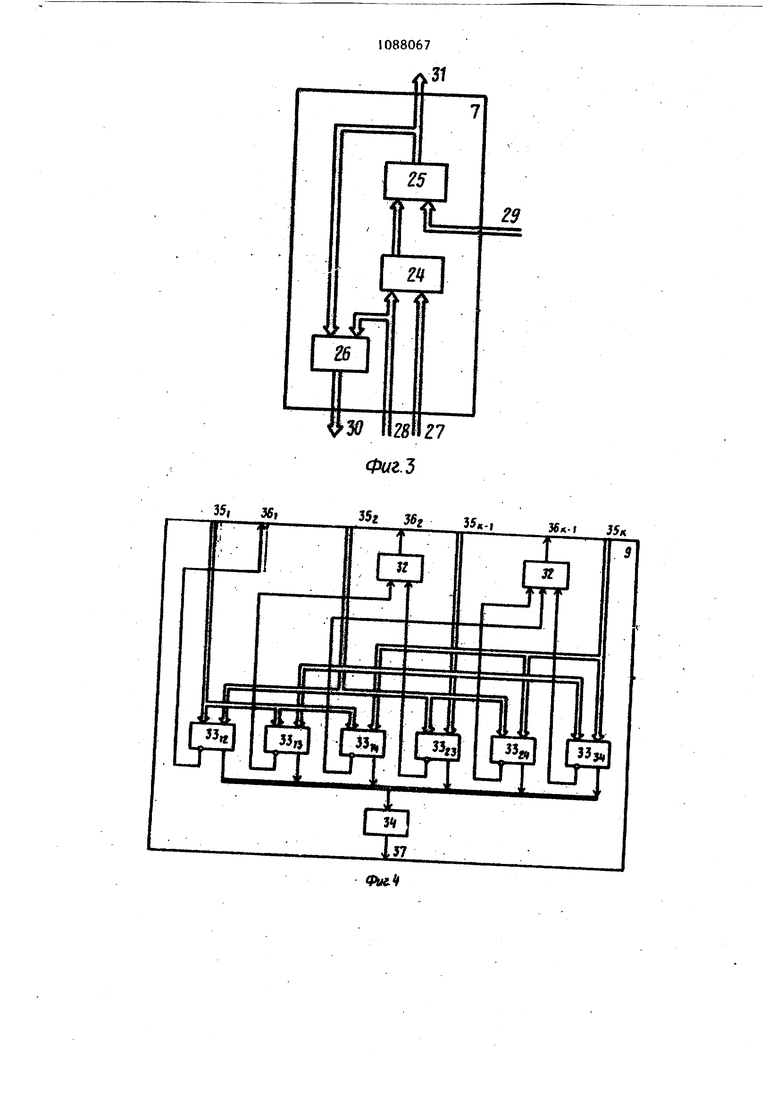

Наиболее близким техническим решением к изобретению является многоканальное оперативное запоминающее устройство, содержащее накопитель, формирователи адресных токов, усилители считывания, формирователи информационньрс сигналов, группу элементов ИЛИ, входные каналы, выходные каналы, распределитель сигналов вьпсодных каналов, логический блок, причем ЙЫХО1Ы элементов ИЛИ групп подключены ко входам соответствующих фор мирйвателей адресных токов, выходы которых подключены к адресным входам накопителя, выходы распределителя си налов выходных каналов соединены со .входами формирователей информационных сигналов, выходы которых подключены к информационным входам накопителя, выходы которого соединены со входа1 и усилителей считывания, первый входной канал содержит первый и второй регистры адреса, первый и вто рой дешифраторы адреса и первый распределитель сигналов канала, причем выходы первого и второго регистров адреса подключены ко входам распределителя сигналов канала, каждый последующий входной канал содержит третий и четвертый регистры адреса, третий и четвертый дешифраторы адреса, второй распределитель сигналов канала и три группы элементов И, при чем выходы третьего и четвертого регистров адреса соединены с первыми входами элементов И первой и второй групп, выходы которых подключены ко входам соответствующих дешифраторов адреса, и со входами второго распределителя сигналов канала, выход которого соединен с первыми входами элементов И третьей группы, выходы дешифраторов адреса входных каналов подключены к одним из входов элементов ИЛИ групп, каждый выходной канал содержит регистр слова, коммутатор и третий распределитель сигналов канала, причем выходы коммутатора подключены ко входам регистра слова, выходы которого соединены с одним из входов третьего распределителя сигналов канала, выход которого соединен с одним из входов распределителя сигналов выходных каналов, другие входы коммутатора и третьего распределителя сигналов вто рого и последующих выходных каналов соединены с выходами элементов И третьей группы соответствующего вход ного канала, а логический блок содержит элементы И, схемы сравне11ия и элемент ИЛИ, причем инверсные выходы схем сравнения подключены ко входам элементов И и одному из выходов логического блока, прямые выходы схем сравнения соединены со входами элемента ИЛИ, входы схем сра нения являются входами логического блока, другими выходами которого явяются выходы элементов И и элемента ИЛИ С 23. Одцако для известного устройства характерно, что приоритеты его каналов жестко закреплены, и в нем не обеспечивается возможность изменения приоритетов каналов, за счет чего ограничивается область применения устройства. Целью изобретения ( двух его вариантов ) является расширение области применения устройства путем обеспечения возможности управления приоритетом его каналов. Поставленная цель достигается тем, что в многоканальное оперативное запоминающее устройство по -первому варианту, содержащее накопитель, формирователи адресных токов, усилители считывания, фррмирователи информационных сигналов, группы элементов ИЛИ, входные и выходные каналы, распределитель сигналов выходных каналов, логический блок, один из выходов которого является выходом устройства, выходы элементов ИЛИ групп подключены ко входам соответствующих формирователей адреснных токов, выходы которых подключены к адресным входам накопителя, выходы распределителя сигналов выходных каналов соединены со входами формирователей информационных сигналов, выходы которых подключены к информационным входам накопителя, выходы которого соединены со входами усилителей считывания, первый входной канал содержит первый и второй регистры адреса, первый и второй дешифраторы адреса, выходы которых яв- , ляются первым и вторым выходами входного канала, и распределитель сигналов, причем выходы первого и второго регистров адреса подключены ко входам распределителя сигналов каналов, первые и вторые выходы входных каналов подключены к одним из входов элементов ИЛИ групп, первые входы выходных каналов подключены к выходам усилителей считывания, вторые входы второго и последующих выходных каналов подключены к третьим выходам соответствующих входных каналов, первые выходы выходных каналов подключены ко входам распределителя сигналов выходных каналов, введены селекторы и блоки ввода данных, а в первый входной канал - три группы элементов И, причем выходы первого и второго регистров адреса подключены к первым входам элементов И первой и второй групп, выхода которых соединены со входами первого и второго дешифраторов адреса, выходы распределителя сигналов являются чет вертым выходом данного канала и подключены к первым входам элементов И третьей группы, выходы которых явIляются третьим выходом первого входного канала и подключены ко второму входу первого выходного канала, вторые входы э/1ементов И подключены к третьему входу первого входного канала, третьи входы и четвертые выходы входных каналов подключены к первым выходам и первым входам селекторов вторые выходы селекторов подключены ко входам логического блока, другие выходы которого подключены ко вторым входам селекторов, третьи входы селекторов подключены к вьсходам соответствующих блоков ввода данных. При этом,в устройство по второму варианту введены переключатели, а в первый входной канал - три группы элементов И, причем выходы йервого и второго регистров адреса подключены к первым входам элементов И nep вой и второй групп, выхода которых соединены со входами первого и второ го дешифратора адреса, выходы распр делителя сигналов являются четвертым выходом данного канала и подключены к первым входам элементов И третьей группы, выходы которых являются третьим выходом первого входного канала и подключены ко второму входу первого выходного канала, вторые входы элементов И подключены к третьему входу первого входного Kia-нала, третьи входы и четвертые выходы входных каналов подключены к одним из выводов переключателей, одноименные контакты переключателей сое.динены между собой и являются другими выводами переключателей, подключенными соответственно к шине питания, ко входам и другим выходам логического 6;joKa. . Первый вариант устройства целесообразно применять при большом числе каналов (больше четырех | и большой информационной емкости памяти (больше 256 тыс.слов ). Применение микросхем средней и большой степени интеграции позволяет создавать компакт ные электронные блоки даже при боль176 шом числе каналов и больших информационных емкостях памяти. Второй вариант устройства целесообразно применять при малом числе каналов (не больше четырех) и небольшой информационной емкости (не более 256 тыс. слов). На фиг.1 и 2 изображена структурная схема первого варианта многоканального оперативного запоминающего устройства; на фиг. 3 - структурная схема выходного канала; на фиг. 4 - структурная схема логического блока (например, для четырехканального устройства); на фиг.5 структурная схема селектора; на фиг.6 - электрическая схема блока ввода информации; на фиг.7 и 8 структурная схема второго варианта многоканального оперативного запоминающего устройства. Многоканальное оперативное запоминающее устройство (по первому вариан. .ту содержит ((Ьиг.1 и 2| накопитель }, формирователи 2 и 2 адресных токов, усилители 3 считывания, формирователи 4 информационных сигналов, группы 51 и 52 элементов ИЛИ, входные каналы б- -6|, выходные каналы 7(где К - число каналов), распределитель 8 сигналов выходных каналов, логический блок 9, селекI О,,, блоки I Iff, ввода информации, и резистор 12. Входной какал 6 (фиг.1 и 2J содержит первый 13 и второй 132 адреса, первый 14i и второй 142 Дешифраторы адреса, распределитель 15 сигналов и Три группы элементов И 16 - 163. Входные каналы 6ц имеют первые 17 ц, вторые 18-,- 18, и третьи 19 - 9 входы и первые 20 - 20ц, вторые 2Ц - .,третьи 21, и четвертые 23 - 23,. выходы. Выход.G ной канал 7 (фиг.З ) содержит коммутатор 24, регистр 25 слова и распределитель 26 сигналов выходного канала. Выходные каналы имеют первые 27;,-27,, вторые 28-,-28, и еретьи входы и первые 30.,-30jj и вторые ЗЦ- 31ц выходы. Логический блок 9 (фиг.4 } содержит элементы И 32, блоки сравнения 33, ЗЗзз 33j, и элемент ИЛИ 34. Логический блок 9 имеет входы 35 - 35 и первые и второй 37 выходы. Индексы в обозначении блоков сравнения указывают на сочетания номеров их входов. Например, блок ЗЗ,,сравнения имеет сочетание на входе из входов 35 и 35 (ъ общем случае блок 9 содержит двух входовые схемы сравнения, количество которых определяется числом сочетаНИИ из К по 2 ) , Селектор 10(фиг.5 содержит двухвходовые.элементы И 38 И элемент И-ИПИ 39. Селекторы имеют первые 40 и вторые 4Ц-А1 выходы и первые 42, вторые и третьи 44(t 441, входы. Блок 1 I ввода информации выполнен в виде бло ка клавиатуры и содержит (фиг.61 К-модульный переключатель 45 с за.виСИМОЙ фиксацией и общей кнопкой сбро са, и резисторы ( и 47. Блоки 11 имеют выходы 48,. Во втором варианте многоканальног оперативного запоминающего устройства (фиг.7 и 8) вместо селекторов 10 10.J4 И блоков 11 -- П ц ввода информации использованы переключатели и , соединенные попарно, а вместо резистора 12 - резистор 51, причем общие выводы переключателей 49 и подключены ко входам 19.К и к выходам 23--23,. входных каналов 6 соответственно, одноименные переключаемые кон53 переключатакты 52 и 53 тедей 49,( и 50 соединены между собой, при этом первые контакты 52 переключателей 49| через резистор 51 подсоединены к источ нику питания, остальные контакты 55L 52|| - к первым выходам 3 ц лоS9 - If ironnijiu lakrvnrraM ЯА --ЧА.. , nn- гического блока 9, входы 35 которого подключены к соответствующим контактам 53, переключателей 50. Устройство работает следующим образом. На входы 17 и ка. налов подаются адреса слов, подлежапшх произвольной или одновременной обработке (считыванию и/или записи I и максимальное число которых при одновременной обработке равно К-числу входных или выходных каналов устройства. Будем условно считать, что входы 17-- 174с соответствуют координате X , а входы 18.координате У устройства. Кроме того, будем иметь в виду следующие три свойства распределителей 15 входных каналов 6.,- во-первых, при совпадении кодов адресов, поступающих 7-,18, каналов на. входы 6 -6 ц , совпадают коды на выходах соответствующих распределителей 15 ISj- 15 (на фиг.2 распределители iSj15 не показаны); во-вторых, при кодах, не совпадаюо111х на входах каналов, но характеризующихся перестановкой первой и второй половин кодов (например, дпя кодбв ОПО 1110 и 1110 0110, где первые половины кодов соответствуют координате X , а вторые - координате У)совпадают коды на выходах соответствующих распределителей 15.-15jj; в-третьих, в остальных случаях не совпадают коды на выходах распределителей 15р. С учетом вьвпеизложенного представляет интерес рассмотрение случаев, охватывающих все интересующие нас события в данном устройстве: несовладение кодов на выходах распредеЛителей 15,- 15,(; во-вторых совпадение кодов адресов каналов или при несовпадении кодов адресов совпадение кодов на выходах распределителей 15., 15,j. При этом совпадение кодов может быть полным (когда совпадшот коды во всех каналах) и частичным (когда совпадают коды в нескольких каналах), При несовпадении кодов на выходах распределителей и, следовательно, при несовпадении кодов адресов , поступающих на входные каналы 6,. (первый случай), входные , 6, И выходные .j каналы полностью независиьш и позволяют обеспечить одновременно считывание и/или запись до /К слов. Поскольку указанные коды не совпадают, то на инверсных выходах всех блоков 33 сравнения (фиг.4) будут высокие уровни, которые,.пройдя элементы И 32 и селектор 10, поступают на входы элементов И , входных каналов качестве разрешающих уровней. Рассмотрим прохождение сигналов через первые входной и выходной каналы устройства, поскольку прохождение сигналов через все остальные входные и выходные каналы аналогично прохождению через первые. При поступлении кода адреса на входы 17 и 18 первого входного канала 6i. с выхода регистров коды адреса поступают непосредственно на входы распределителя 15 и на входы дешифраторов 14, адреса через предварительно открытые элементы И 16 и 16,. С выходов дешифра П IV у. и 14 через элементы ИЛИ 5 торов 14 и 52 сигналы поступают на входы формирователей 2. и 2 В результате н соответствующих входах накопителя I будут выбраны запоминаюцие элементы и на входы усилителей 3 поступает первое считанное слово. Распределитель 15 в соответствии с содержимы 13 подключает усиреГНСтронлители 3 через коммутатор регистру 25 первого выходного канала /L . Таким образом, считанное первое слово из накопителя поступает на информационный выход 31 устройстваАналогично работает все остальные каналы устройства. Прежде чем описывать работу устройства в других режимах, поясним установку приоритета каналов. Установка приоритета каналов осуществля ется исходя из следующих условий. Младшему номеру модуля переключателя 45 блока II (на фиг.6 крайни левый I в первом варианте устройства и младшим номерам переключаемым кон тактам 53f переключателей 49,49ц и .По второму варианту устройства соответствует наивысший приоритет и наобор| т. Таким образом приоритет модулей переключателя 45 (фиг.6 I и переключаемых контактов 53jj (фиг. 81 убывают слева направо. Включением требуемого модуля перевлючателя 45 в первом варианте и установкой определенного переключателя 49 и 50 в требуемое положение по второму варианту устройства осуществляется установка приоритета со ответствующего канала. Во всех каналах устройства долж ны быть установлены различные (несо падающие ) приоритеты. Установка одн го и того же приоритета хотя бы в . двух каналах недопустима, так как в случае совпадения кодов на выходах распределителей 15 данных входных каналов возникает сбой в устройстве, о чем будет свидетельствовать появление уровня логической единицы на выходе 37 логического блока 9. Селекторы 10,-10 под управление блоков - по первому варианту и непосредственно (самостоятельно ) переключатели и , по второму варианту устройства обеспечивают требуемую перекоммутацию 154J- 15,ц вх выходов распределителей Hkx каналов 6;,-6| на входы ,ц , логического блока 9 и, следовательн 7 на входы блоков ЗЗ.- 33 сравнения (для четырехканального устройства- 33t2. 3% - 33з)1 При поступлении на .входы 35,.-35 логического блока 9 совпадающих кодов (вследствие совпадения кодов адреса на входах 17-,- 7ц и 18.-18,и (или) на выходах распределителей 15,15j5 входных каналов 6-,-6j)Ha выходах 36j логического блока 9 появятся К-1 запрещающих уровней логического нуля, где К - число каналов устройства. В соответствии с установленной коммутацией входов 35,К-1 запрещающих уровней логического нуля с выходов ( логического блока 9 поступят через селекторы lOj,10 яо первому варианту, и через переключатели 49j( - по второму варианту устройства в соответствующие входные каналы . Тем самым обеспечивается блокировка К-1 из К каналов устройства. При зтом единственным незаблокированным каналом будет канал с наивысшим приоритетом. Разрешающий уровень логической единицы для него будет передан от источника питания Е„ через резистор 12 (фиг.11 и элемент И-ИЛИ 39(фиг.5/ соответствующего селектора 10 по первому варианту, и через резистор 51 и соответствующий переключатель 49 (фиг.8 } по второму варианту устройства. Далее рассмотрим работу устройства в других режимах. При полном совпадении кодов адре17 -17сов, поступающих на входы и/или при полном совпадеиНИИ кодов на выходах распределителей всех входных каналов 6-J- 6ц только один, вполне определенный входной и ему соответствзгющий выходной канал открыты. Все остальные каналы заблокированы. При этом открытым входным каналом будет тот, который связан, с источником питания ЕЛИТ. через резистор 12 по первому варианту,и через резистор 51 по второму варианту устройства. При частичном совпадении кодов адреса и(или ) кодов на выходах распределителей 15 некоторых входных каналов все остальные каналы открыты и работают независимо друг от друга. Те каналы, в которых произошло совпадение указанных кодов, блокирзпотся исключением одного - канала с наибольшим приоритетом.При этом на выходе 37 блока 9 появляется уровень логической единицы, свидетельству1йщий о произошедшем совпадении кодов в устройстве. Технико-экономическое преимушество предлагаемого устройства состоит в том, что оно позволяет, обрабатывать информацию параллельно (одновременно ) по К каналам и на несколь ко порядков сниэить вероятность возникновения конфликтных обращений к общей памяти и за счет этого существенно повысить производительность . многопроцессорных вычислительных систем, обеспечить возможность оперативного управления и изменения приоритетов обслуживания устройств-потребителей С процессоров ), что повышает гибкость и.позволяет создапать более совершенные алгоритмы функционирования вычислительных систем, выполненных на основе предложенного устройства.

«ч 35, 36, 35г Збг 35,.| 3ffx.i 35ц

Ml

.

./

tJt.L

«

«3, 03;

Фиг, 6

«

м-

t

CS U

k

«

Ч

«м

:

5Г

Д..«

)Г

«о

с

r

«м so

5TE

k

Я

а

о

if « «о

w

15

«й- г

1Ми,

m

и

« :

С

и

к

Ail

PC:

-CZb-

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Майоров С.А., Новиков Г.И | |||

| Структура электронных вычислительных машин | |||

| Л., Машиностроение, 1979, | |||

| с | |||

| Замкнутая радиосеть с несколькими контурами и с одной неподвижной точкой опоры | 1918 |

|

SU353A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3305032/18-24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-23—Публикация

1982-11-26—Подача