5 ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1981 |

|

SU978192A1 |

| Многоканальное оперативное запоминающее устройство (его варианты) | 1982 |

|

SU1088067A1 |

| Многоканальное запоминающее устройство | 1981 |

|

SU953669A1 |

| Оперативное запоминающее устройство | 1984 |

|

SU1236551A1 |

| Многоканальное оперативное запоминающее устройство | 1983 |

|

SU1112406A2 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство микропрограммного управления | 1990 |

|

SU1815636A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Запоминающее устройство | 1975 |

|

SU639016A1 |

1

Изобретение относится к запоминающим устройствам и может быть использовано в двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти.

Известно оперативное запоминающее устройство, в котором ресурсы общей оперативной памяти используются несколькими устройствами-потребителями , которые функционируют независимо друг от друга, генерируя обращение к памяти с целью записи и считывания информации П.

Недостатком этого запоминающего устройства является то, что оно не обеспечивает возможность одновременного обслуживания хотя бы двух устройств-потребителей.

Наиболее близким по технической сущности к изобретению является . оперативное запоминающее устройство, содержащее регистр адреса У., подключенный к входам координатного дешифратора адреса У, регистр адреса X, подключенный к входам координатного дешифратора адреса X, координатные фopмиpoвateли X и У, подключенные к соответствующим обмоткам накопителя, обмотки считывания накопителя через блок усилителей считывания подключены к первым входам блоков коммутаторов усилителей, выходы блоков коммутаторов че,0 рез регистры слова связаны с выходными шинами устройства и с первыми входами первичных узлов выбора разрядных формирователей, выходами подключенных к разрядным обмоткам

)5 накопителя через последовательно соединенные блок выбора разрядных формирователей и блок разрядных . формирователей, выходы регистров X и У через блок выбора усилителей

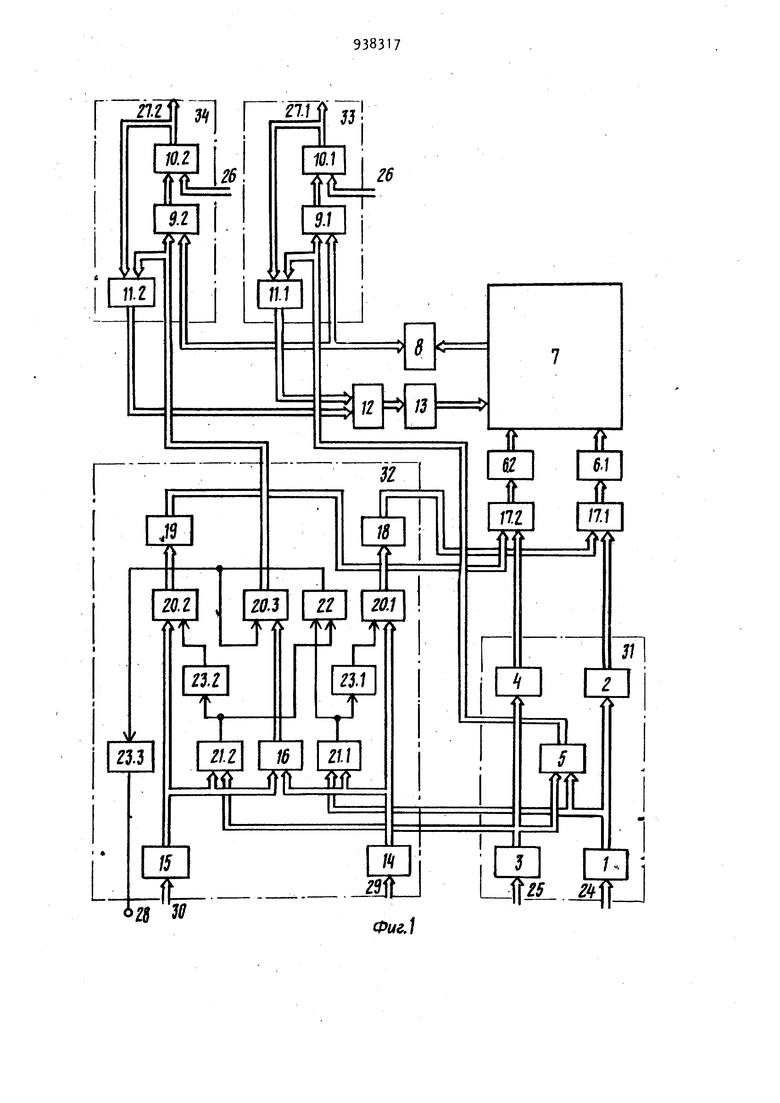

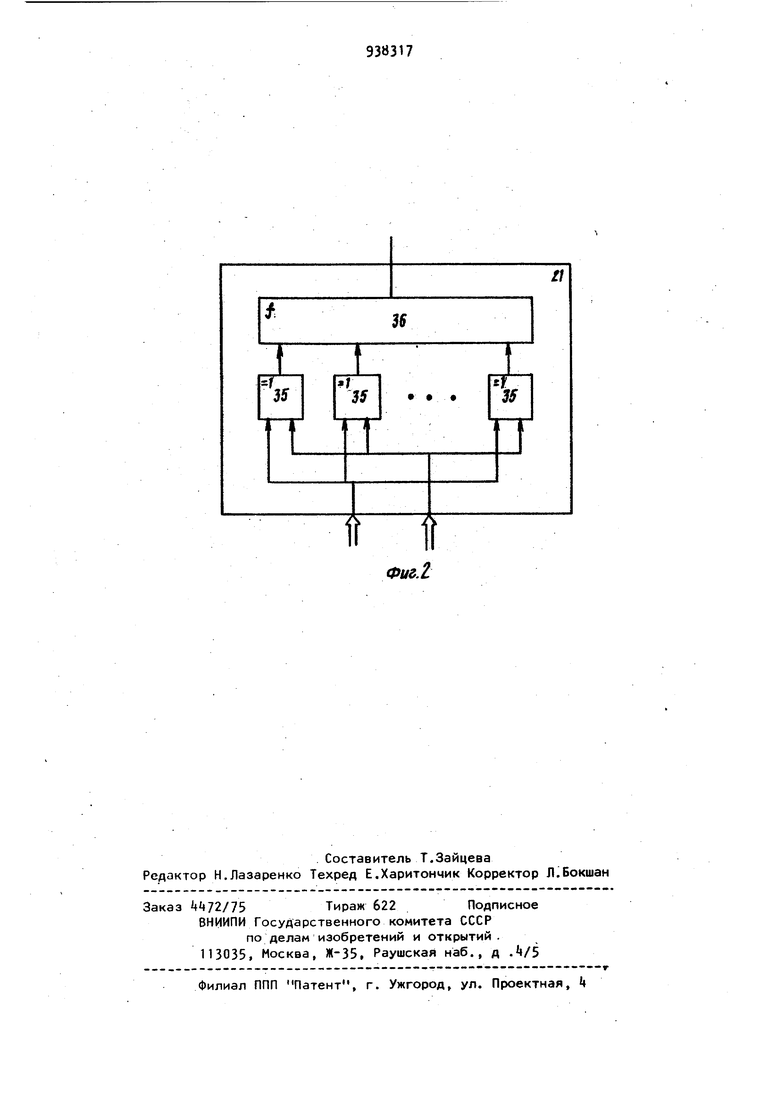

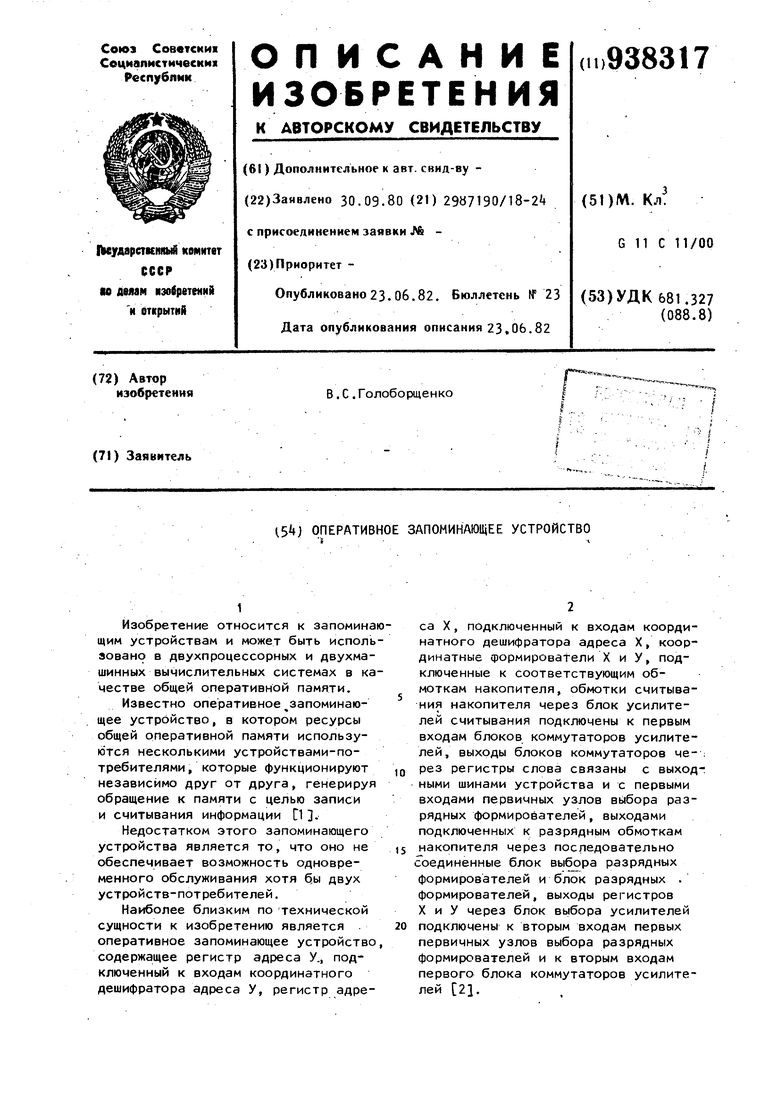

20 подключены к вторым входам первых первичных узлов выбора разрядных формирователей и к вторым входам первого блока коммутаторов усилителей 2, 393 Недостатком ;4;1звестного устройств является ограниченность области его применения, поскольку оно не позволяет двум устройствам-потребителям одновременно обрабатывать (считыват и записывать } два слова. Цель изобретения - расширение области применения устройства за счет обеспечения возможности использования его в качестве общей on ративной памяти в двухпроцессорных вычислительных системах при одновре менном считывании и записи двух слоев. Поставленная цель достигается тем, что в оперативное запоминающее устройство, содержащее накопитель, формирователи адресных сигналов,уси лители считывания, коммутаторы, регистры слов , формирователи информационных сигналов, распределители сигналов, дешифраторы адреса и регистры адреса, причем выходы первого регистра адреса подключены к входам первого дешифратора адреса и одним из входов первого распределителя, сигналов , выходы второго регистра адреса соединены с входами второго дешифратору адреса и дру гими входами первого распределителя сигналов, выходы формирователей адресных сигналов подключены к адресным входам накопителя, информаци онные выходы которого соединены с входами усилителей считывания,выходы которых подключены к одним из входов коммутаторов, другие входы первого коммутатора соединены с выходами первого распределителя сигналов и одним из входов второго распределителя сигналов, другие .входы второго коммутатора подключен к одним из входов третьего распределителя сигналов, выходы коммутаторов соединены соответственно с одними из входов регистров слов, другие входы и выходы которых являются соответственно .информационными входами и выходами устройства,вы ходы первого и второго регистров слов подключены к другим входам вто рого и третьего распределителей сигналов соответственно, выходы которых соединены с входами четвертого распределителя сигналов, выход которого подключены к входам формирователей информационных сигналов, выходы которых соединены.с информационными входами усилителя,введены третий и четвертый регистры адреса, третий и четвертый дешифраторы адреса, пятый распределитель сигналов, схемы сравнения, элементы ИЛИ, элементы И, элемент И-НЕ и элементы НЕ, причем выходы третьего и четвертого регистров адреса соединены соответственно с входами пятого распределителя сигналов, одними из входов первой и второй схем сравнения соответственно и одними из входов, первого и второго элементов И соответственно , выходы которых подключены к входам третьего и четвертого дешифратора адреса соответственно, выходы которых соединены с одними из входов первого и второго элементов ИЛИ соответственно , другие входы которых подключены к выходам первого и второго дешифраторов адреса соответственно, выходы элементов ИЛИ соединены с входами формирователей адресных сигналов, выходы схем сравнения Подключены к входам элемента И-Ht и входам первого и второго элементов НЕ, выходы которых соединены с другими входами первого и второго элементов И соответственно, выходы пятого распределителя сигналов соединены с одними из входов третьего элемента И, выходы которого подключены к другим входам второго коммутатора, а другой вход соединен с выходом элемента И-НЕ и входом третьего элемента НЕ, выход которого является индикаторным выходом устройства. На фиг.1 изображена функциональная схема предлагаемого устройства; на фиг,2 - структурная схема наиболее предпочтительного варианта выполненная схемы сравнения. Устройство содержит первый регистр 1 адреса, первый дешифратор 2 адреса, второй регистр 3 адреса, второй дешифратор 4 адреса, первый распределитель 5 сигналов, первый 6.1 и второй 6.2 формирователи адресных си1- налов, накопитель 7, усилители 8 считывания, первый 9.1 и второй 9-2 коммутаторы, первый 10.1 и второй 10.2 регистры слов, второй 11.1, третий 11.2 и четвертый 12 распределители сигналов, формирователи 13 информационных сигналов, третий регистр 14 адреса, четвертый регистр 15 адреса, пятый распределитель 16 сигналов, первый 17.1 и второй 17.2 элементы ИЛИ, третий 18 и четвертый 19 дешифраторы адреса, первый 20.1, второй 20.2 и третий 20.3 элементы И, первую 21.1 и вторую 21.2 схемы сравнения, элемент И-НЕ 22, первый 23.1, второй 23.2 и третий 23.3 элементы НЕ, первый 2k и второй 25 адресные входы, информационные вход 26 и выходы 27.1 и 27.2, индикаторный выход 28, третий 29 и четвертый 30 адресные входы устройства, основной 31 и дополнительный 32 входные каналы, первый 33 и второй 3 выходные каналы устройства. Схема сравнения (фиг.2) включает элементы НЕРАВНОЗНАЧНОСТЬ 35 и элемент И 36. Устройство работает следующим образом. На адресные входы 2k, 25, 29 и 30 (фиг.1) устройства подаются адреса двух слов, подлежащих обработке (считыванию и/или записи). При этом возможны три случая: несовпадение адресов, частичное совпадение (совпадение только по координате X или У ) и полное совпадение адресов (совпадение по координатам Х,И У).. Будем условно считать, что входы 25 и 30 соответствуют координате X, а входы 2k и 2Э - координате У, При несовпадении адресов работа обоих входных каналов 31 и 32 (фиг протекает независимо друг от друга а именно: в канале 31 с выходов регистров 1 и 3 коды адреса поступаю на входы дешифраторов 2 и 4, -а также на входы распределителя 5 (фиг. С выходов дешифраторов 2 и i через элементы ИЛИ 17.1 и 17.2 поступают сигналы на входы формирователей 6.1 и 6.2 для возбуждения координатных обмоток накопителя 7. В результате на соответствующих координатных обмотках накопителя 7 будут выбраны запоминающие элементы, и на входы усилителей 8 поступит первое слово считанное в соответствии с адресом пришедшим на входы 2k и 25. Распределитель 5 в соответствии с содержимым регистров 1 и 3 подключит усилители 8 через коммутатор 9.1 к регистру 10.1 первого выходного канала ЗЗ устройства. Таким образом, считанное первое слово из накопителя 7 поступит на первый информационный выход 27.1 устройства. В дополнительном выходном канале 32 адрес второго слова, поступивший на входы 29 и 30 через регистры И и 15 будет передан на входы первого 20.1 и второго 20.2 элементов И, первые входы схем 21.1 и 21.2 сравнения и входы распределителя 16. На вторые входы схем 21.1 и 21.2 сравнения-с выходов регистров 1 и 3 поступят коды адреса первого слова, поданного на входы 2 и 25. При несовпадении кодов адресов первого и второго слов, на выходе хотя бы одного из элементов НЕРАВНОЗНАЧНОСТЬ 35 (фиг.2) будет присутствовать низкий уровень сигнала, поэтому на выходе элемента И Зб (фиг.2) и на выходе каждой схемы 21.1 и 21.2 (фиг.1) будет низкий уровень, свидетельствующий о несовпадении кодов адресов, поступивших на входы устройства. С выходов схем 21.1 и 21.2 сравнения (фиг.1) низкие уровни через элементы НЕ 23.1 и 23.2 будут поданы на вторые входы элементов И 20.1 и 20.2 в качестве разрешающих (высоких) уровней сигналов, в результате код адреса второго слова, поступивший на входы 29 и 30 (фиг.1), будет передан на входы дешифраторов 18 и 19 (фиг.1), с выходов КОТОРЫХ продешифрированные коды адреса подаются через элементы ИЛИ 17.1 и 17.2 на входы формирователей 6.1 и 6.2, При возбуждении формирователей 6.1 и -6.2 из накопителя 7 будет считано второе слово, которое через усилители 8 поступит на входы коммутаторов 9-1 и 9.2. Одновременно с этим выходом схем сравнения 21.1 и 21.2 низкие уровни сигналов поступят на элемент И-НЕ 22, с . выхода которого высокий уровень сигнала будет подан на второй вход элемента И 20.3, на первые входы которого поступят сигналы с выходов распределителя 16 (фиг.1). Выходные сигналы распределителя 16 определяются содержимым регистров }k и 15 и, пройдя через элемент И 20.3, подключат усилители 8 через коммутаторы 9.2 к регистру 10.2 Таким образом, второе слово, считанное из накопителя 7 поступит на выход 27.2 устройства. При частичном совпадении адресов двух слов (совпадение по координате X или У ) совпадают содержимые регистров 1 и tU или соответственно 7 регистров 3 и 15 (фиг.1). При этом, например, при совпадении содержимых регистров 3 и 15 на выходе второй схемы 21.2 сравнения появится высокий уровень сигнала, поскольку на входах каждого элемента НЕРАВНОЗНАЧ НОСТЬ 35 (фиг.2) в этом случае буд одинаковые уровни сигналов и, следо тельно, на выходе элемента И 36 бу дет высокий уровень сигнала. С выхода схемы сравнения 21.2 высокий уровень сигнала поступит на вход элемента И 20.2 и запретит прохожде ние кода адреса с выхода регистра 15 на дешифратор 19. В результате этого через элемент ИЛИ 17.2 пройдут сигналы для возбуждения формиро вателя 6.2 только с выхода регистра 3 (фиг.1). Поскольку коды адресов на регист pax 1 и не совпадают, то на выход первой схемы 21.1 сравнения будет присутствовать низкий уровень сигна ла, который разрешит прохождение ко да адреса с выхода регистра Т на дешифратор 18. Сигналом, с выхода дешифратора 18 будет возбужден формирователь 6.1 (фиг.1). В результат будут считаны из накопителя 7 два слова, у которых одни координаты ко адреса (X или У) частично совпали. При полном совпадении кодов адре сов двух слов на выходах обеих схем сравнения 21.1 и 21.2 появятся высо кие уровни сигналов, которые запретят прохождение кодов адресов с регистров 1 и 15 на дешифраторы 18 и 19. Одновременно высокие уровни сигналов с-выходом схем сравнения 21.1 и 21.2 будут поданы на вхо ды элемента И-НЕ 22, с выхода которо го низкий уровень сигнала поступит н второй вход третьего элемента И 20. и запретит прохождение сигналов с выхода распределителя 16 на входы коммутаторов Э.2 и входы распределителя 11.2 и, следовательно, на выход 27.2 второго выходного канала 3 . В результате описываемое устройство будет реагировать только на код адреса, поступившего на входные шины 2k и 25 основного входного канала 31 (фиг. и . В соответствии с этим адресом из накопителя 7 будет считано только одно слово, которое появиться на выходе 27.1 первого выходного канала 33. Одновременно с этим низкий 78 уровень сигнала с выхода элемента И-НЕ 22 (фиг.1), пройдя через элемент НЕ 23.3 и преобразовавшись в высокий уровень, поступит на индикаторный выход 28 устройства, сигнализируя о совпадении кодов двух слов, поступивших в устройство. Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно позволяет двум устройствам-потребителям одновременно считывать и/или записывать в накопитель два слова, за счет чего расширяется, по сравнению с известным, область его применения в качестве общей оперативной памяти в двухпроцессорных системах. Формула изобретения Оперативное запоминающее устройство, содержащее накопитель, формирователи адресных сигналов усилители считывания, коммутаторы, регистры слов, формирователи информационных сигналов, распределители сигналов, дешифраторы адреса и регистры адреса, причем выходы первого регистра адреса подключены к входам первого дешифратора адреса и одним из входов первого распределителя сигналов, выходы второго регистра адреса соединены с входами второго дешифратора адреса и другими входами первого распределителя сигналов, выходы формирователей адресных сигн: лов подключены к адресным входам накопителя, информационные выходы которого соединены с входами усилителей считывания, выходы которых подключены к одним из входов коммутаторов, другие входы первого коммутатора соединены с выходами первого распределителя сигналов и одними из входов второго распределителя сигналов, другие входы второго коммутатора подключены к одним из входов третьего распределителя сигналов, выходы коммутаторов соединены соответственно с одними из входов регистров слов,цругие входы и выходы которых являются соответственно информационными входами и выходами устройства, выходы первого и второго регистров слов подключены к другим входам второго и третьего распределителей сигналов соответственно, выходы которых

9 , 938 соединены с входами -четвертого распределителя сигналов, выходы которого подключены к входам формирователей информационных сигналов, выходы которых соединены с информационными входами усилителя, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности использования его в качестве общей оперативной памяти в двухпроцессорных вычислитель-н ных системах, оно содержит третий и четвертый регистры адреса, третий и четвертый дешифраторы адреса, пятый распределитель сигналов, схемы оравнения, элементы ИЛИ, элементы И, элемент И-НЕ и элементы НЕ, причем выходы третьего и четвертого регистров адреса соединены соответственно с входами пятого распределителя сигналов, одними из входов первой и второй схем сравнения соответственно и одними из входов первого и второго элементов И соответственно, выходы которых подключены к входам третьего и четвертого дешифраторов адреса соответственно, выходы которых соединены с одним из входов первого и второго элементов

710

ИЛИ соответственно, другие входы которых подключены к выходам первого и второго дешифраторов адреса соответственно, выходы элементов ИЛИ соединены с входами формирователей адресных сигналов, выходы схем сравнения подключены к входам элемента И-НЕ и входам первого и второго элементов НЕ, выходы которых соединены с другими входами первого и второго элементов И соответственно, выходы пятого распределителя сигналов соединены с одними из входо третьего элемента И, выходы которого подключены к другим входам второго коммутатора, а другой вход соединен с выходом элемента И-НЕ и входом третьего элемента НЕ, выход которого является индикаторным выходом устройства.

Источники информации, принятые во внимание при экспертизе

1979, с.353-355.

Фиг.1

Фиг.2

Авторы

Даты

1982-06-23—Публикация

1980-09-30—Подача