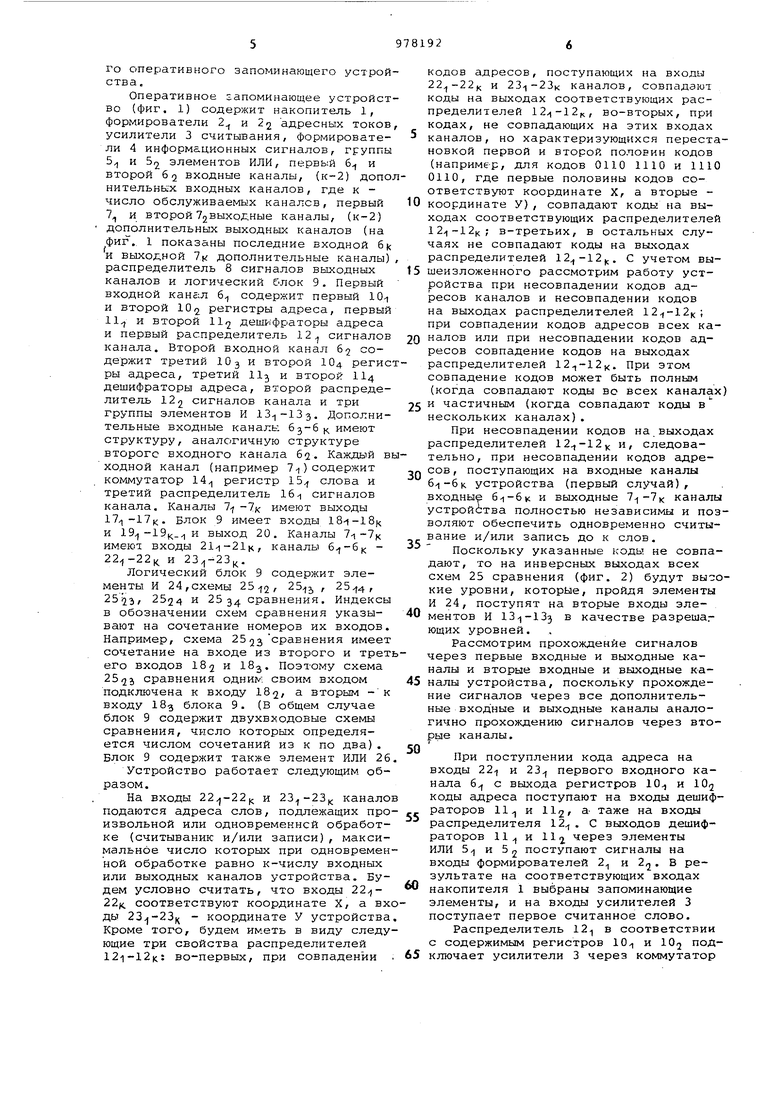

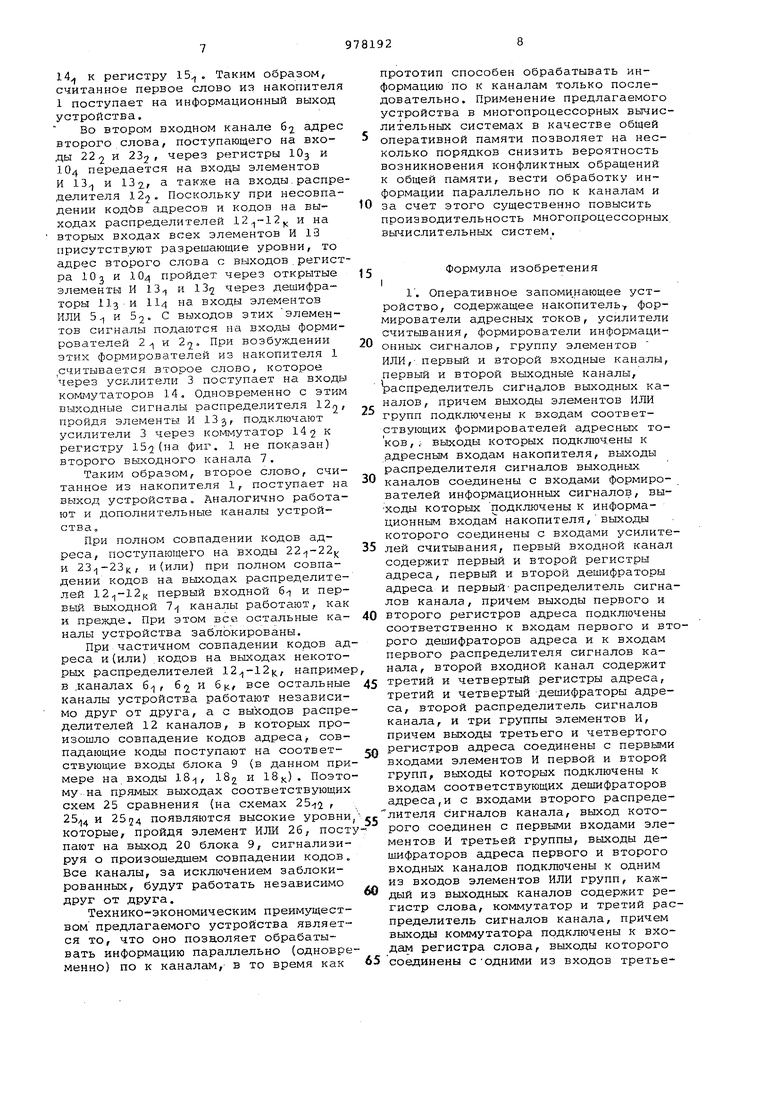

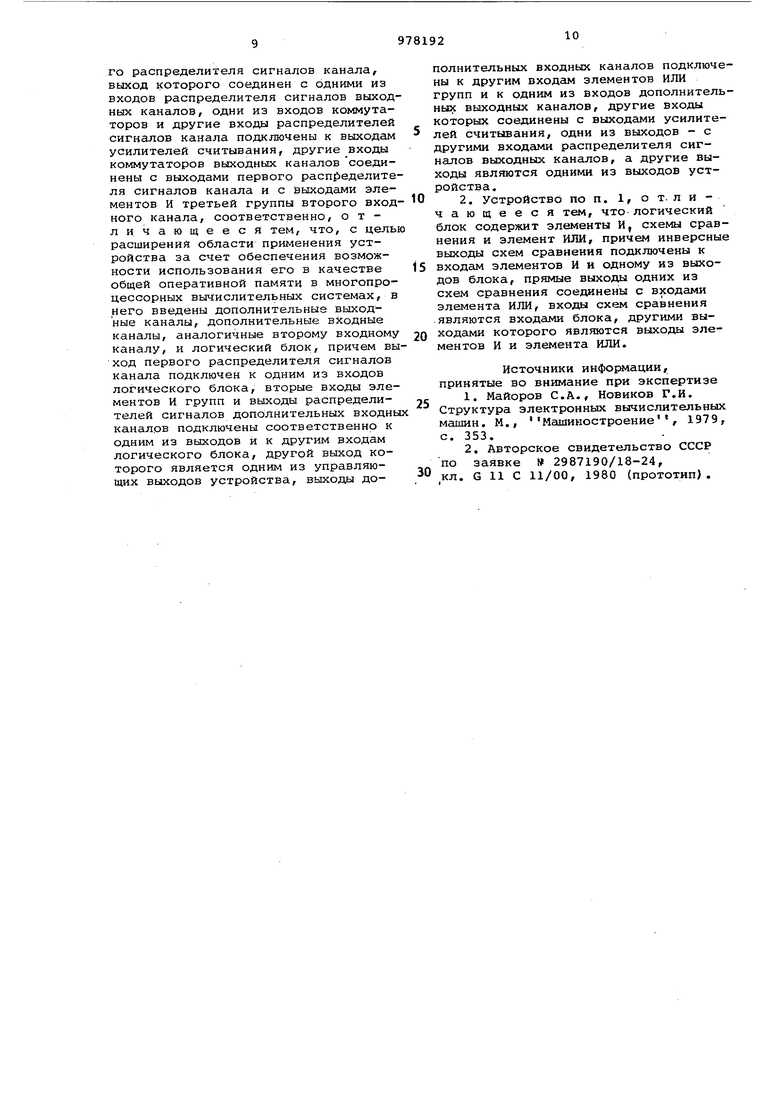

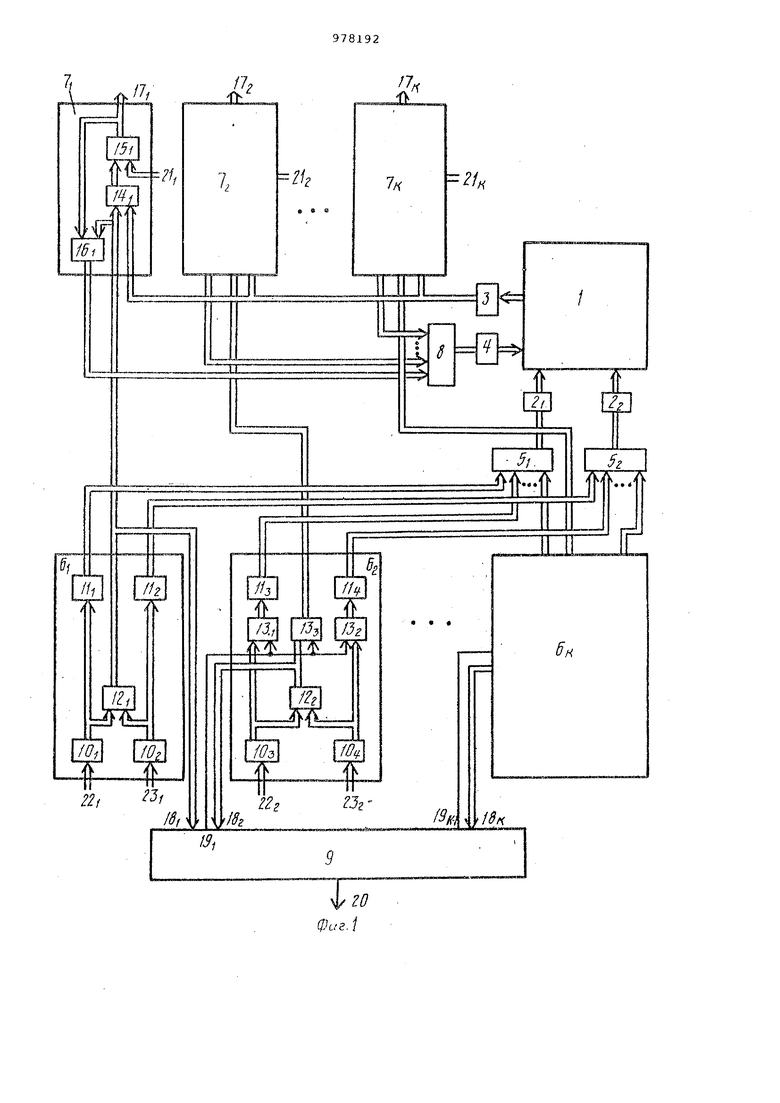

причем выходы коммутатора через ре гистр слова связаны с выходными uui нами устройства и первыми входами распределителя сигналов, в каждом вы ходном канале выход распределителя сигналов подключен к соответствующим входам распределителя сигналов выход ных каналовf первые входы коммутатор каждого выходного канала подключены к выходам, усилителей считывания, вто рые входы коммутатора и распределите ля сигналов первого выходного канала связаны с выходами распределителя сигналов первого входного канала, вторые входы комглутатора и распредли теля сигналов второго выходного кана ла связаны с гзыходами элементов И третьей группы второго входного канала I 2 „ Недостаток известного устройства состоит в томf что оно не позволяет проиэвольнслгу числу у строй ств-потреби тел е;й одновременно обрабатывать (сч.итыБать и записывать) произвольное число слов, что ограничивает область применения устройства, Цель изобретения - расш1;рение области применения устройства за счет обеспечения возможности использовани его в качестве общей оперативной памяти в многопроцессорных вычислитель ных системах (с числом процессоров больше: двух) , Поставленная цеэль достигается тем что в операливное запоминающее устройство, содерх ащее накопитель, формирователи адресных токов, усилители считывания, формирователи информационных сигналов, группы элементов ИЛИ первый и второй входные каналы, первый и второй выходные каналы, распре делитель сигналов выходных каналов, причем выходы элементов ИЛИ групп подключ. к входам соответствующих формирователей адресных токов, выходы которых подключены к адресным вхо Дс1М накопителя, выходы расределителя сигналов выходных каналов соединены входами формирователей информационны сигналов, выходы которых подключены к информацио 1ным входам накопителя. выходы которого соединены с входами усилителей считывания, первый входной канал содержит первый и второй р гистры адреса, первый и второй дешиф раторы адреса и первый распределител сигналов канала, причем выходы перво го и второго регистров адреса подклю чены соответственно к входам первого и второго дешифраторов адреса и к входам первого распределителя сигналов канала, второй входной канал содержит третий и четвертый регистры адреса, третий и четвертый дегдшфраторы адреса, второй распределитель сигналов канала, и три группы элемен тов И, причем выходы третьего и четвертого регистров адреса соединегны с первыми входами элементов И первой и второй групп, выходы которых подключены к входам соответствующих дешифраторов адреса, и с входами второго распределителя сигналов канала, выход которого соединен с первыми входами элементов И третьей группы, выходы дешифраторов адреса первого и второго входных каналов подключены к одним из входов элементов ИЛИ группы, каждый из выходных каналов содержит регистр слова, коммутатор и третий распределитель сигналов канала, причем выходы коммутатора подключены к входам регистра слова, выходы которого соединены с одними из входов третьего распределителя сигналов канала, выход которого соединен с одними из входов распределителя сигналов выходных каналов г одни из входов KoiviMyTaTroров и другие входы распределителей сигналов канала подключены к выходам усилителей считывания, другие входы коммутаторов выходных каналов соединены с выходами первого распределителя сигналов канала и с выходами элементов И третьей группы второго входного канала соответственно, в него введены дополнительные выходные каналы, дополнительные входные каналы, аналогичные второму входному каналу, и логический блок, причем выход первого распределителя.сигналов канала подключен к одним из входов логического блока, вторые входы элементов И групп и выходы распределителей сигналов дополнительных входных каналов подключены соответственно к одним из выходов и к другим входам логического блока, другой выход которого является одним из управляющих выходов устройства, выходы дополнительных входных каналов подключены к другим входам элементов ИЛИ групп и к одним из входов дополнительных выходных каналов, другие входы которьгх соединены с выходами усилителей считывания, одни из выходов - с другими входами распределителя сигналов выходных каналов, а другие выходы являются одними из выходов устройства. Кроме того, логический блок содержит элементы И, схемы сравнения и элемент ИЛИ, причем инверсные выходы схем сравнения подключены к входам элементов И и одному из выходов блока, прямые выходы одних из схем сравнения соединены с входами элемента ИЛИ, входы схем сравнения являются, входами блока, другими выходами которого являются выходы элементов И и элемента ИЛИ. На фиг. 1 изображена структурная схема оперативного запоминающего устройства; на фиг. 2 - функциональная схема логического блока, выполненного, например, для четырехканального оперативного запоминающего устрой ства. Оперативное запоминающее устройст во {фиг. 1) содержит накопитель 1, формирователи 2 и 25 адресных токов усилители 3 считывания, формирователи 4 информационных сигналов, группы 5 и 5 элементов ИЛИ, первый 6 и второй 6-2 входные каналы, (к-2) допо нительных входных каналов, где к число обслуживаемых каналов, первый 7 и второй 72выходные каналы, (к-2) дополнительных выходных каналов (на фиг.. 1 показаны последние входной 6к и выходной 7к дополнительные каналы) распределитель 8 сигналов ВЕЛХОДНЫХ каналов и логический блок 9. Первый входной канс1Л 6 содержит первый 10 и второй 102 регистры адреса, первый 11 и второй 11,2 дешифраторы адреса и первый распределитель 12 сигналов канала. Второй входной канал 65 содержит третий Юз и второй 104 регис ры адреса, третий llj и второй 114 дешифраторы адреса, второй распределитель 122 сигналов канала и три группы элементов И 13-,-13з. Дополнительные входные каналы 63-61 имеют структуру, аналогичную структуре второго входного канала 65. Каждый в ходной канал (например 7)содержит коммутатор 14 регистр 15 слова и третий распределитель 16 сигналов канала. Каналы имеют выходы 17/,-17(/. Блок 9 имеет входы l8-i-l8( и 19 -19к--1 и выход 20. Каналы 7-1-7 имеют входы , каналы 6-,-бк и . Логический блок 9 содержит элементы И 24,схемы 25-12, 25,,j , 25, , 2524 и 2534 сравнения. Индексы в обозначении схем сравнения указывают на сочетание номеров их входов. Например, схема 25 53 Рэ внения имеет сочетание на входе из второго и трет его входов 185 и 183. Поэтому схема 25-23 сравнения одним своим входом подключена к входу IS, а вторым -к входу 18-3 блока 9. (В общем случае блок 9 содержит двухвходовые схемы сравнения, число которых определяется числом сочетаний из к по два). Блок 9 содержит также элемент ИЛИ 26 Устройство работает следующим образом. На входы и канало подаются адреса слов, подлежащих про извольной или одновременнсй обработке (считыванию и/или записи), максимальное число которых при одновремен ной обработке равно к-числу входных или выходных каналов устройства. Будем условно считать, что входы 22-)22«. соответствуют координате X, а вх ды - координате У устройства Кроме того, будем иметь в виду следу ющие три свойства распределителей 121-12к: во-первых, при совпадении кодов адресов, поступающих на входы и 23-(-23к каналов, совпадают коды на выходах соответствующих распределителей , во-вторых, при кодах, не совпадающих на этих входах каналов, но характеризующихся перестановкой первой и второй половин кодов (например, для кодов ОНО 1110 и 1110 ОНО, где первые половины кодов соответствуют координате X, а вторые координате У), совпадают коды на выходах соответствующих распределителей в-третьих, в остальных случаях не совпадают коды на выходах распределителей . С учетом вышеизложенного рассмотрим работу устройства при несовпадении кодов адресов каналов и несовпадении кодов на выходах распределителей 12 -12к; при совпадении кодов адресов всех каналов или при несовпадении кодов адресов совпадение кодов на выходах распределителей 12-,-12ц. При этом совпадение кодов может быть полным (когда совпадают коды во всех каналах) и частичным (когда совпадают коды в нескольких каналах). При несовпадении кодов на выходах распределителей ,, и, следовательно, при несовпадении кодов адресов, поступающих на входные каналы 6-1-6к устройства (первый случай), входные 6-1-6к и выходные каналы устройства полностью независимы и позволяют обеспечить одновременно считывание и/или запись до к слов. Поскольку указанные коды не совпадают, то на инверсных выходах всех схем 25 сравнения (фиг. 2) будут высокие уровни, которые, пройдя элементы И 24, поступят на вторые входы элементов И 13.,-13э в качестве разреша.ющих уровней. Рассмотрим прохождение сигналов через первые входные и выходные каналы и вторые входные и выходные каналы устройства, поскольку прохождение сигналов через все дополнительные входные и выходные каналы аналогично прохождению сигналов через вторые каналы. При поступлении кода адреса на входы 22.J и 23 первого входного канала 6 с выхода регистров Ю. и 102 коды адреса поступают на входы дешифраторов 11 и II12г а- таже на входы распределителя 12. С выходов дешифраторов 11 и 112 через элементы ИЛИ 5/1 и Sj поступают сигналы на входы формирователей 2 и , В результате на соответствующих входах накопителя 1 выбраны запоминающие элементы, и на входы усилителей 3 поступает первое считанное слово. Распределитель 12 в соответствии с содержимым регистров 10-, и 10 подключает усилители 3 через коммутатор 14 к регистру 15, Таким образом, считанное первое слово из накопителя 1 поступает на информационный выход устройства. Во втором входном канале 6 адрес второго слова, поступающего на входы 22 2 и 232, через регистры Юз и 104 передается на входы элементов И 13 и 132., а также на входы, распре делителя 122- Поскольку при несовпадении кодбв адресов и кодов на выходах распределителей , и на вторых входах всех элементов И 13 присутствуют разрешающие уровни, то адрес второго слова с выходов.регист ра 103 и 10 пройдет через открытые элементы И 13 и 13 через дешифраторы Из и 114 нэ. входы элементов ИЛИ 5 и 52 С выходов этих элементов сигналы подаются на входы формирователей 2 и 2rj. При возбуждении этих формирователей из накопителя 1 .считывается второе слово, которое через ус ;лители 3 поступает на входы коммутаторов 14, Одновременно с этим выходные сигналы распределителя 122, пройдя элементы И 13зг подключают усилители 3 через коммутатор 142 к регистру 15(на фиг. 1 не показан) второго выходного канала 7, Таким образом, второе слово, считанное из накопителя 1, поступает на выход устройства. Аналогично работают и дополнительные каналы устройства. При полном совпадении кодов адреса, поступающего на входы и (;, и (или) при полном совпадении кодов на выходах распределителей , первый входной 6 и первый ВЕЛходной 7 каналы работают, как и прежде. При этом все остальные каналы устройства заблокированы. При частичном совпадении кодов ад реса и(или) кодов на выходах некоторых распределителей , наприме в .каналах 6-;, 6 и б|, все остальные каналы устройства работают независимо друг от друга, а с выходов распре делителей 12 каналов, в которых произошло совпадение кодов адреса совпадающие коды поступают на соответствующие входы блока 9 (в данном при мере на входы 18, ISj и 18), Поэто му, на прямых выходах соответствующих схем 25 сравнения (на схемах 25х,2 , и 2524 появляются высокие уровни которые, пройдя элемент ИЛИ 26, пост пают на выход 20 блока 9, сигнализируя о произошедшем совпадении кодов. Все каналы, за исключением заблокированных, будут работать независимо друг от друга. Технико-экономическим преимуществом предлагаемого устройства является то, что оно позаоляет обрабатывать информацию параллельно (одновре менно) по к каналам,- в то время как прототип способен обрабатывать информацию по к каналам только последовательно. Применение предлагаемого устройства в многопроцессорных вычислительных системах в качестве общей оперативной памяти позволяет на несколько порядков снизить вероятность возникновения конфликтных обращений к общей памяти, вести обработку информации параллельно по к каналам и за счет этого существенно повысить производительность многопроцессорных вычислительных систем. Формула изобретения I 1, Оперативное запоми.нающее устройство, содержащее накопитель формирователи адресных токов, усилители считывания, формирователи информационных сигналов, группу элементов ИЛИ, первый и второй входные каналы, первый и второй выходные каналы, распределитель сигналов выходных каналов, причем выходы элементов ИЛИ групп подключены к входам соответствующих формирователей адресных токов, ;- выходы КОТОРЫХ подключены к адресным входам накопителя, выходы распределителя сигналов выходных каналов соединены с входами формирователей информационных сигналов, выходы которых подключены к информационным входам накопителя,выходы которого соединены с входами усилителей считывания, первый входной канал содержит первый и второй регистры адреса, первый и второй дешифраторы адреса и первый-распределитель сигналов канала, причем выходы первого и второго регистров адреса подключены соответственно к входам первого и второго дешифраторов адреса и к входам первого распределителя сигналов канала, второй входной канал содержит третий и четвертый регистры адреса, третий и четвертый дешифраторы адреса, второй распределитель сигналов канала, и три группы элементов И, причем выходы третьего и четвертого регистров адреса соединены с первыми входами элементов И первой и второй групп, выходы которых подключены к входам соответствующих дещифраторов адреса,и с входами второго распределителя сигналов канала, выход которого соединен с первыми входами элементов И третьей группы, выходы дешифраторов адреса первого и второго входных каналов подключены к одним из входов элементов ИЛИ групп, каждый из выходных каналов содержит регистр слова, коммутатор и третий распределитель сигналов канала, причем выходы коммутатора подключены к входам регистра слова, выходы которого соединены с одними из входов третьего распределителя сигналов канала, выход которого соединен с одними из входов распределителя сигналов выходных каналов, одни из входов коммутаторов и другие входы распределителей сигналов канала подключены к вьлходам усилителей считывания, другие входы коммутаторов выходных каналов соединены с выходами первого распределителя сигналов канала и с выходами элементов И третьей группы второго входного канала, соответственно, отличающееся тем, что, с цель расширения области применения устройства за счет обеспечения возможности использования его в качестве общей оперативной памяти в многопроцессорных вычислительных системах, в него введены дополнительные выходные каналы, дополнительные входные каналы, аналогичные второму входному каналу, и логический блок, причем выход первого распределителя сигналов канала подключен к одним из входов логического блока, вторые входы элементов и групп и выходы распределителей сигналов дополнительных входны каналов подключены соответственно к одним из выходов и к другим входам логического блока, другой выход которого является одним из управляющих выходов устройства, выходы дополнительных входных каналов подключены к другим входам элементов ИЛИ групп и к одним из входов дополнительных выходных каналов, другие входы которых соединены с выходами усилителей считывания, одни из выходов - с другими входами распределителя сигналов выходных каналов, а другие выходы являются одними из выходов устройства,

2. Устройство по п. 1, от. ли чающееся тем, что логический блок содерясит элементы И, схемы сравнения и элемент ИЛИ, причем инверсные выходы схем сравнения подключены к

входс1М элементов И и одному из выходов блока, прямые выходы одних из схем сравнения соедо1нены с входами элемента ИЛИ, входы схем сравнения .являются входами блока, другими выходами которого являются выходы элементов И и элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Майоров С.А., Новиков Г.И. Структура электронных вычислительных машин, М., Машиностроение, 1979, с. 353.

2.Авторское свидетельство СССР по заявке W 2987190/18-24,

кл. G 11 С 11/00, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное оперативное запоминающее устройство (его варианты) | 1982 |

|

SU1088067A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Многоканальное оперативное запоминающее устройство | 1983 |

|

SU1112406A2 |

| Многоканальное запоминающее устройство | 1981 |

|

SU953669A1 |

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Оперативное запоминающее устройство | 1984 |

|

SU1236551A1 |

| Устройство для сопряжения телеграфных каналов с электронной вычислительной машиной | 1982 |

|

SU1067494A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

Авторы

Даты

1982-11-30—Публикация

1981-06-24—Подача