Изобретение относится к вычислительной технике и предназначено для использования в многопроцессорных к многомашинных вычислительных системах в качестве общей оперативной памяти.

По основному авт. св. № 1088067 известно многоканальное оперативное запоминающее устройствс содержащее накопитель, формирователи адресных токов, усилители считывания, формирователи информационных сигналов, группы элементов ИЛИ, входной и выходной каналы, распределитель сигналов выходных каналов, селекторы блока ввода данных и логический блок, один из выходов которого является выходом устройства, выходы элементов ИЛИ групп подключены к входам соответствующих формирователей адресных токов, выходы которых подключены к адресным входам накопителя, выходы распределителя сигналов выходных каналов соединены с входами формирователей информационных сигналов, выходы которых подключены к информационным входам накопителя, выходы которого соединены с входами усилителей считывания первый входной канал содержит первый и второй регистры адреса, первый и второй дешифраторы адреса, выходы которых являются первым и вторым выходами входного канала, и рас-, пределитель сигналов, причем выходы первого и второго регистров адреса подключены к входам распределителя сигналов, первые и вторые выходы входных каналов - к одним из входов элементов ИЛИ групп, первые входы выходных каналов - к выходам усилителей считывания, вторые входы второго и последующих выходных каналов к третьим выходам соответствующих входных каналов, первые выходы выходных каналов - к входам распределителя сигналов выходных каналов, причем первый входной канал содержит три группы элементов И, а выходы первого и второго регистров адреса подключены к первым входам элементов И первой и второй групп, выходы которых соединены с входами первого и второго дешифраторов адреса, выходы распределителя сигналов являются четвертым выходом данного канала и подключены к первым входам элементов И третьей группы, выходы которых являются третьим выходом первого входного канала и подключены к второму входу первого выходного канала, вторые входы элементов И подключены к третьему входу первого входного канала, третьи входы и четвертые выходы входных каналов - к первым выходам и первым входам селекторов, вторые выходы селекторов - к входам логического блока, другие выходы которо.го подключены к вторым входам селекторов, третьи входы селекторов - к выходам соответствующих блоков ввода данных . Недостатком известного устройства является невысокая точность контроля его приоритетов каналов, что снижает надежность устройства. Это обусловлено тем, что контролируются конфликтные обращения, устройств-потребителей (процессоров) и не кбнтролируется правильность установки приоритетов его каналов, в результате чего могут возникать неопределенные ситуации и сбои. Так при несовпадении кодов адресов на входах устройства и/или при несовпадении кодов иа выходах распределителей сигналов

в устройстве не обнаруживается неправильная установка приоритетов каналов. Следует отметить, что в данном случае это и не влияет на работоспособность устройства. Однако при появлении уровня логической единицы на выходе логического блока неясно, возник ли этот уровень только из-за конфликтного обращения процессоров, что не влияет на дальнейшее продолжение работы устройства, или из-за конфликтного обращения процессоров и неправильной установки приоритета, что приводит к сбою и требует вмешательства оператора в работу устройства. Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что

в многоканальное оперативное запоминающее устройство введены первый элемент ИЛИ и дополнительный логический блок, входы которого подключены к одноименным выходам блоков ввода информации, а выход соединен с одним из входов первого элемента ИЛИ, другой вход которого подключен к второму выходу логического блока, причем выходы дополнительного логического блока и первого элемента ИЛИ являются одними из выходов устройства.

При этом дополнительный логический

блок содержит элементы И-ИЛИ и вто-. рой элемент ИЛИ, выход которого является выходом блока, а входы подключены к выходам элементов И-ИЛИ, входы которых попарно соединены между собой по принципу

сочетаний «из К по два (где К - число каналов устройства) и являются входами блока.

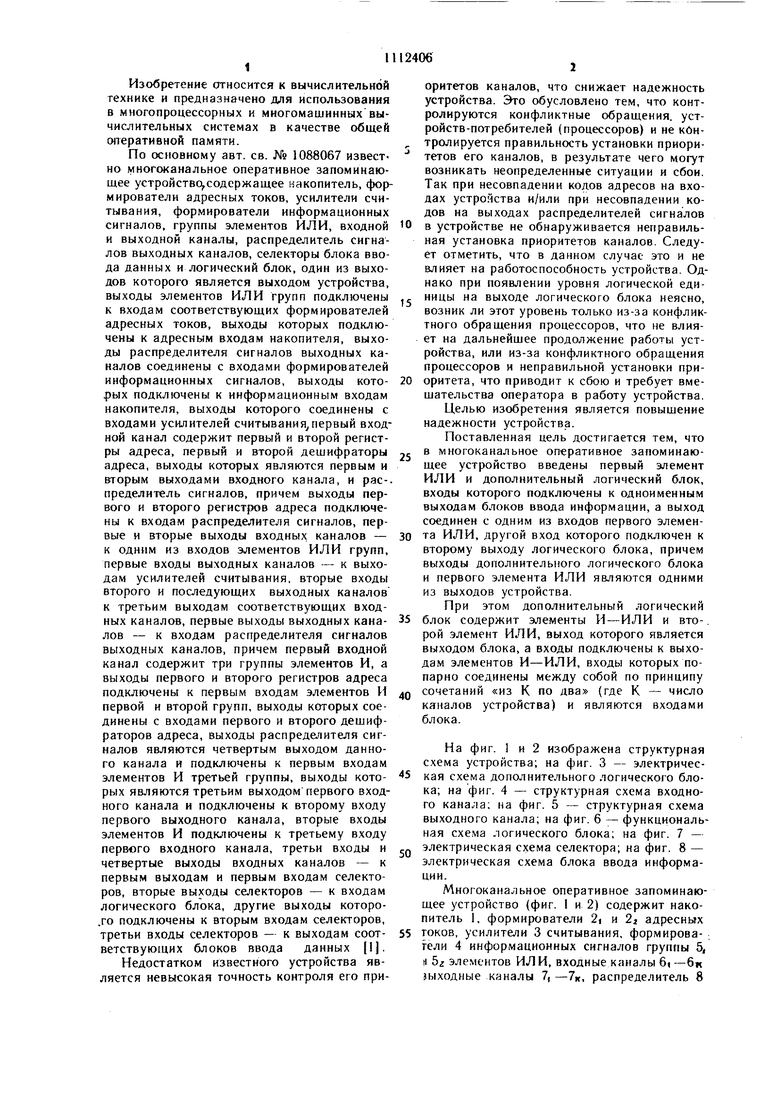

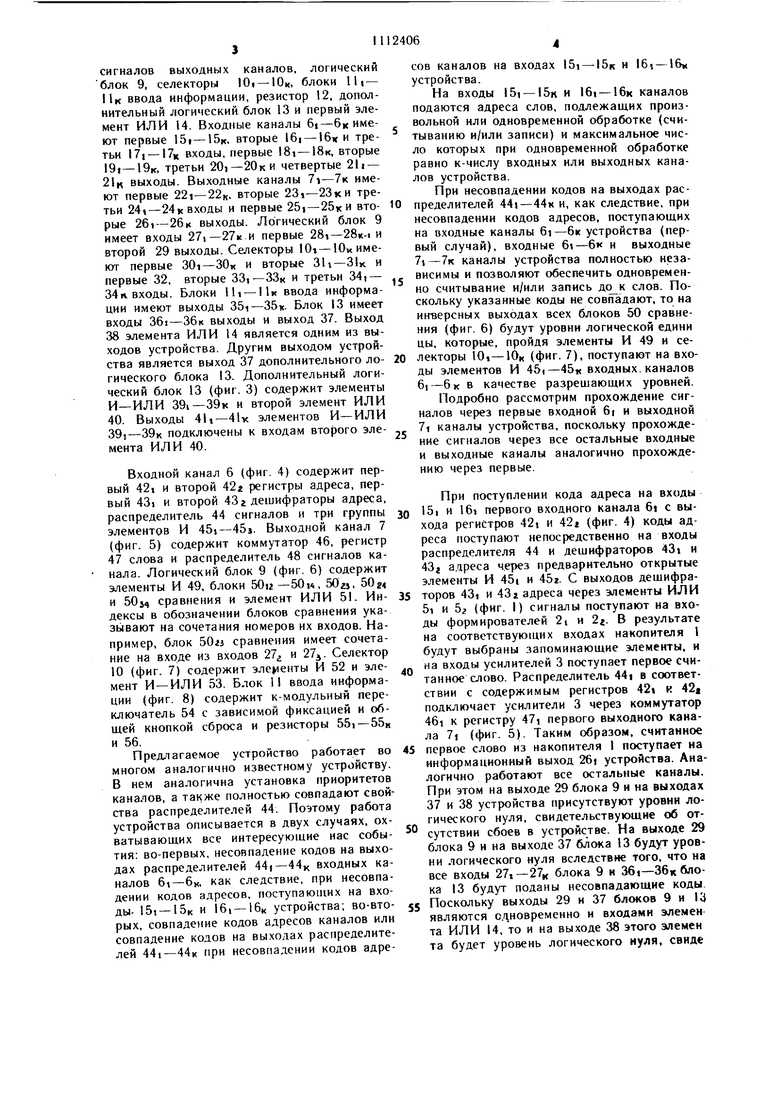

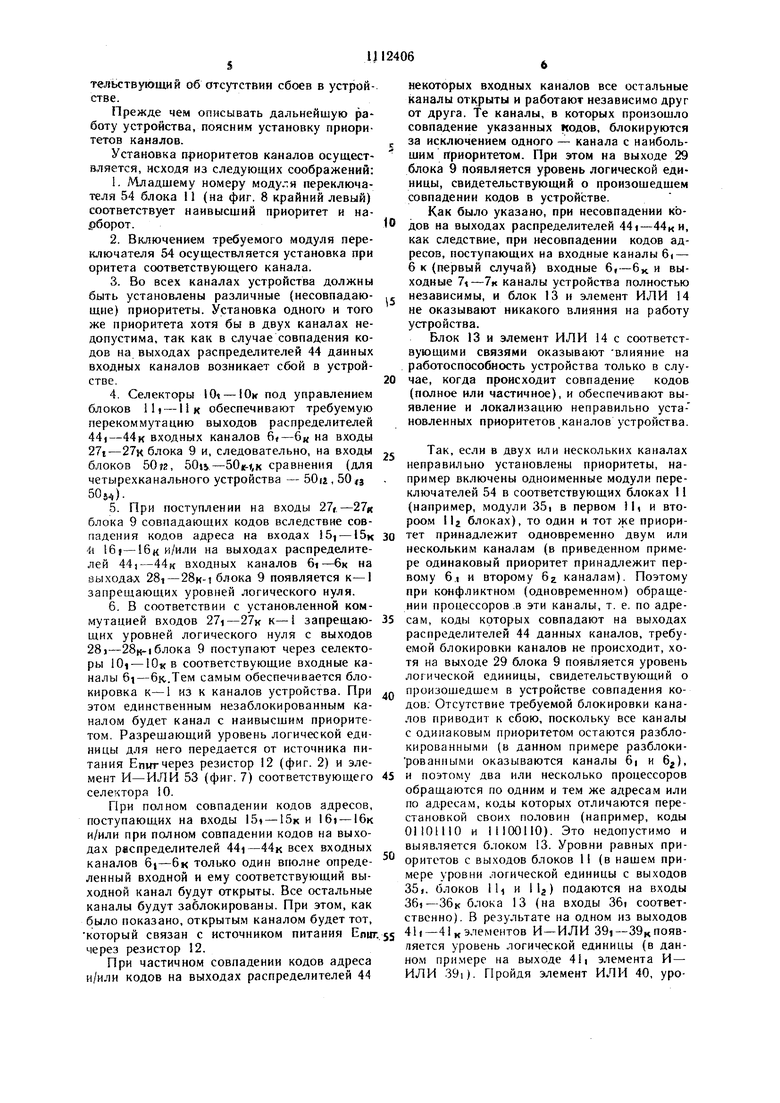

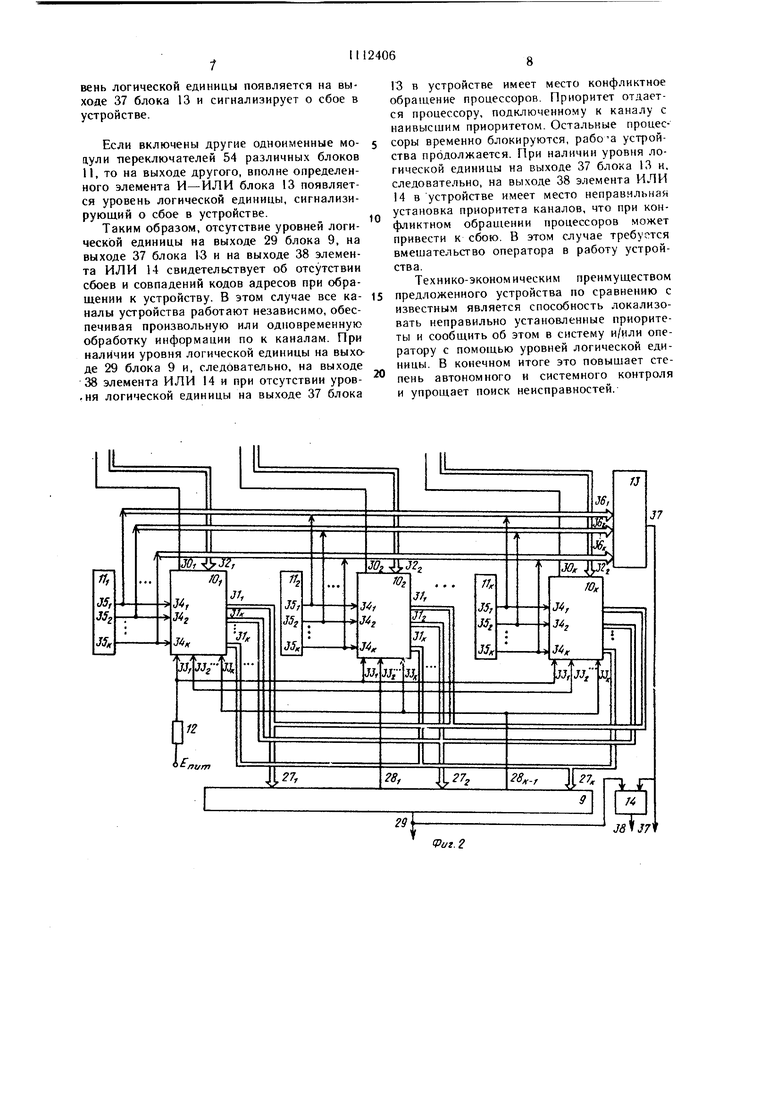

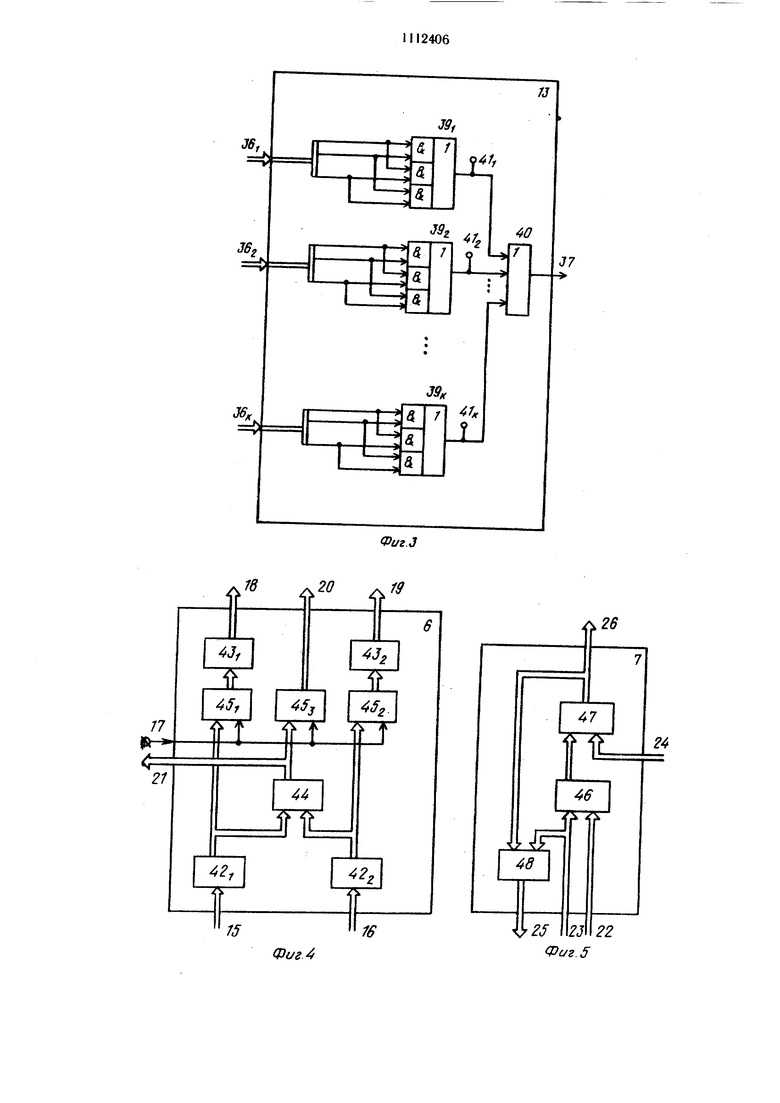

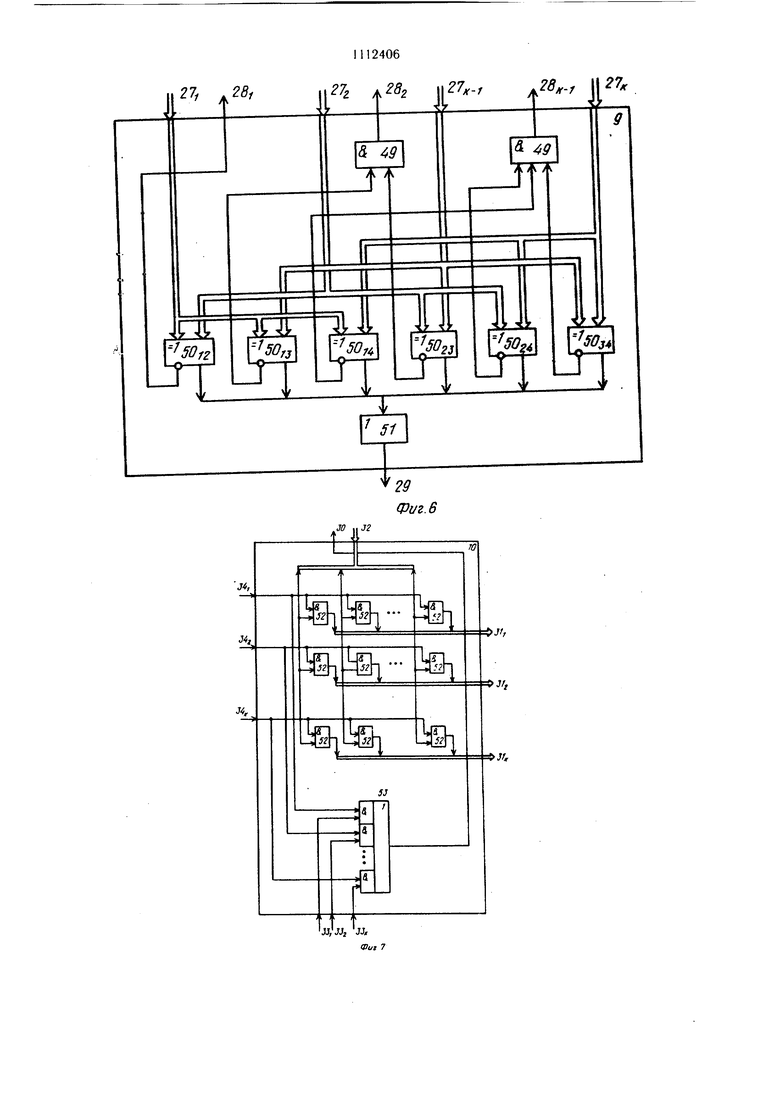

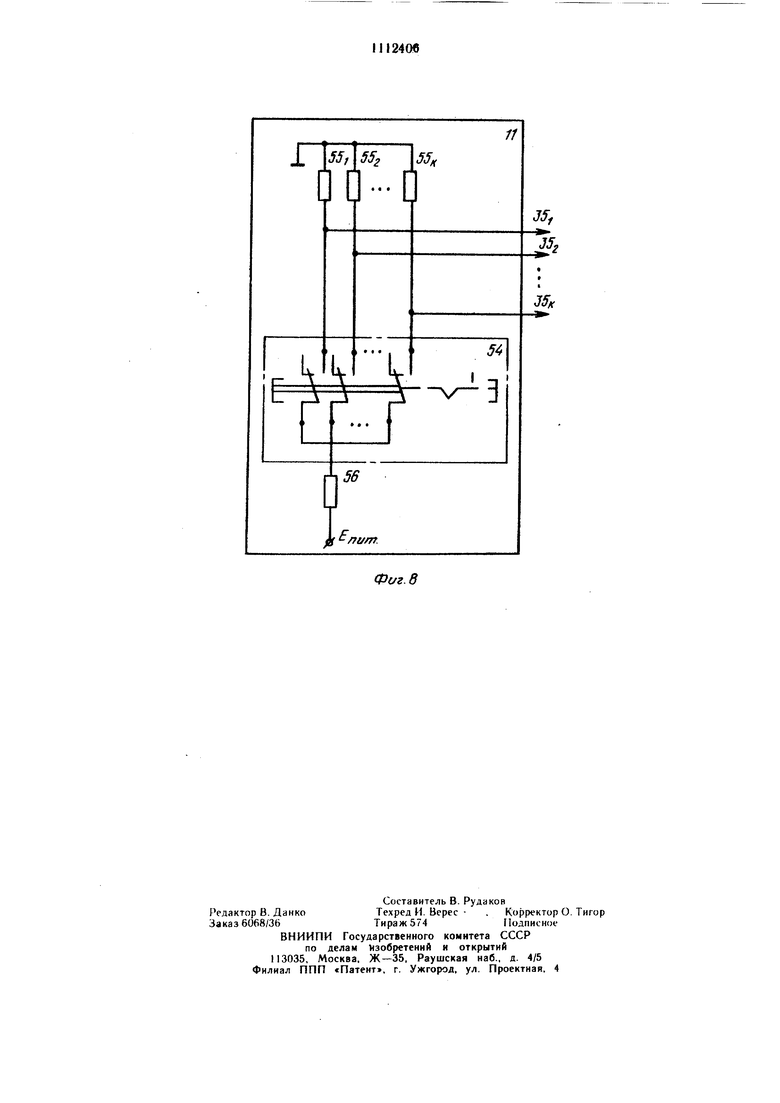

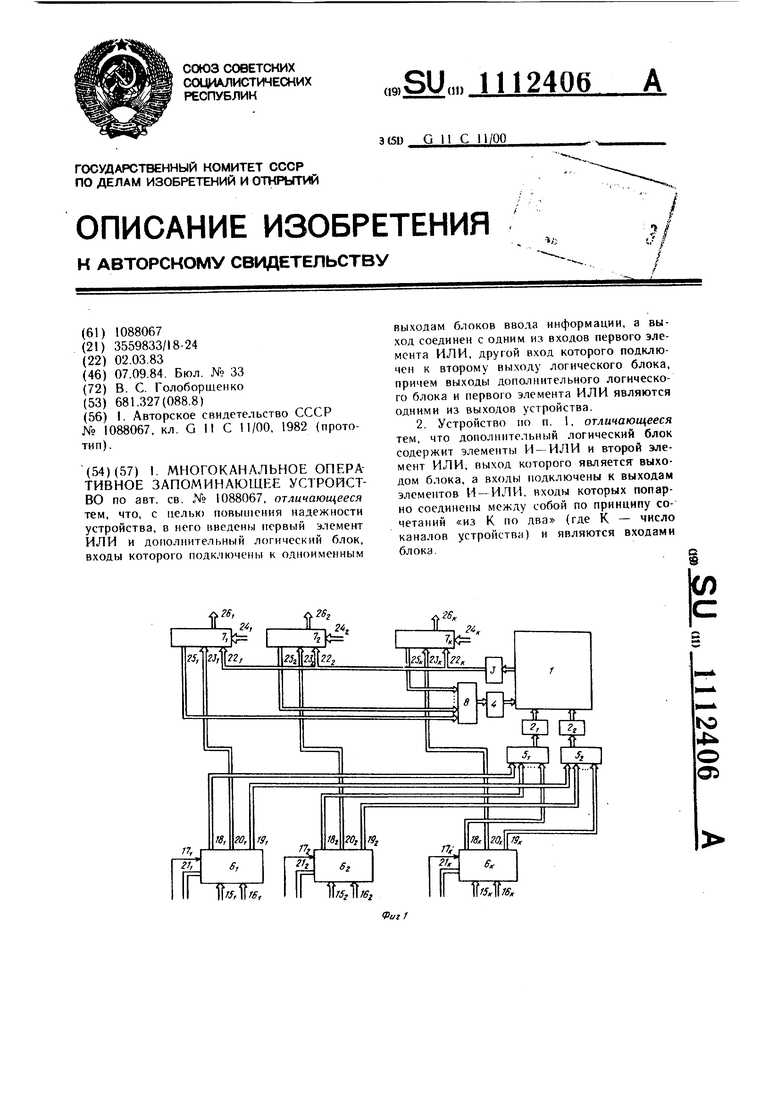

На фиг. 1 и 2 изображена структурная схема устройства; на фиг. 3 - электрическая схема дополнительного логического блока; на фиг. 4 - структурная схема входного канала; на фиг. 5 - структурная схема выходного канала; на фиг. 6 - функциональная схема логического блока; на фиг. 7 -

электрическая схема селектора; на фиг. 8 - электрическая схема блока ввода информации.

Многоканальное оперативное запоминающее устройство (фиг. 1 и 2) содержит накопитель 1, формирователи 2i и 2j адресных

токов, усилители 3 считывания, формирователи 4 информационных сигналов группы 5, к 5г элементов ИЛИ, входные каналы 6i-6к выходные каналы 7, -7к, распределитель 8

сигналов выходных каналов, логический блок 9, селекторы lOi - 10к, блоки lit - UK ввода информации, резистор 12, дополнительный логический блок 13 и первый элемент ИЛИ И. Входные каналы 6i-6к имеют первые 15|-15к, вторые I6| - 16ж и третьи I7t - 17к входы, первые I8i-18к, вторые 191-19к, третьи 20i-20 к и четвертые 211 - 21к выходы. Выходные каналы имеют первые 22i-22к, вторые 23 -23ки третьи 24t-24к входы и первые 25i-25к и вторые 261-26к выходы. Логический блок 9 имеет входы и первые 28t-28it-i и второй 29 выходы. Селекторы 10%-Юкимеют первые 30i-ЗОк и вторые и первые 32, вторые и третьи 341 - 34л входы. Блоки Ih - 11к ввода информации имеют выходы 35i-35х. Блок 13 имеет входы 36i-Збк выходы и выход 37. Выход 38 элемента ИЛИ 14 является одним из выходов устройства. Другим выходом устройства является выход 37 дополнительного логического блока 13. Дополнительный логический блок 13 (фиг. 3) содержит элементы И-ИЛИ 39v-39к и второй элемент ИЛИ 40. Выходы 411-41х элементов И-ИЛИ подключены к входам второго элемента ИЛИ 40.

Входной канал 6 (фиг. 4) содержит первый 42 и второй 42г регистры адреса, первый 43j и второй 43г дешифраторы адреса, распределитель 44 сигналов и три группы элементов И . Выходной канал 7 (фиг. 5) содержит коммутатор 46, регистр 47 слова и распределитель 48 сигналов канала. Логический блок 9 (фиг. 6) содержит элементы И 49, блоки 50« -50м, 50а, 50г4 и 50м сравнения и элемент ИЛИ 51. Индексы в обозначении блоков сравнения указывают на сочетания номеров их входов. Например, блок 50« сравнения имеет сочетание на входе из входов 27 и 27з. Селектор 10 (фиг. 7) содержит эле 1енты И 52 и элемент И -ИЛИ 53. Блок II ввода информации (фиг. 8) содержит к-модульный переключатель 54 с зависимой фиксацией и общей кнопкой сброса и резисторы 55i-55и и 56.

Предлагаемое устройство работает во многом аналогично известному устройству. В нем аналогична установка приоритетов каналов, а также полностью совпадают свойства распределителей 44. Поэтому работа устройства описывается в двух случаях, охватывающих все интересующие нас события: во-первых, несовпадение кодов на выходах распределителей 44|-44 входных каналов 6t-6к, как следствие, при несовпадении кодов адресов, поступающих на входы- 15i -15к и 16| -16к устройства; во-вторых, совпадение кодов адресов каналов или совпадение кодов на выходах распределителей 44i-44к при несовпадении кодов адресов каналов на входах I5i -15к и 16.,- 16i устройства.

На входы I5i -15к и I6i -16к каналов подаются адреса слов, подлежащих произвольной или одновременной обработке (считыванию и/или записи) и максимальное число которых при одновременной обработке равно к-числу входных или выходных каналов устройства.

При несовпадении кодов на выходах распределителей 44t-44к и, как следствие, при несовпадении кодов адресов, поступающнх на входные каналы 6i-6к устройства (первый случай), входные 6t-6к и выходные каналы устройства полностью неза- висимы и позволяют обеспечить одновременно считывание и/или запись слов. Поскольку указанные коды не совпадают, то на инверсных выходах всех блоков 50 сравнения (фиг. 6) будут уровни логической едини цы, которые, пройдя элементы И 49 и се0 лекторы (фиг. 7), поступают на входы элементов И 45i-45к входных, каналов 6)-6 к в качестве разрещающих уровней. Подробно рассмотрим прохождение сигналов через первые входной 6i и выходной 7i каналы устройства, поскольку прохождение сигналов через все остальные входные и выходные каналы аналогично прохождению через первые.

При поступлении кода адреса на входы

0 15| и 16i первого входного канала 6« с выхода регистров 42 и 42 (фиг. 4) коды адреса поступают непосредственно на входы распределителя 44 и дешифраторов 43 и 43 адреса через предварительно открытые элементы И 45i и 45г. С выходов дещифра5 торов 43i и 43г адреса через элементы ИЛИ 5i и 5г (фиг. I) сигналы поступают на входы формирователей 2 и 2j. В результате на соответствующих входах накопителя 1 будут выбраны запоминающие элементы, и .. на входы усилителей 3 поступает первое считанное слово. Распределитель 44i в соответствии с содержимым регистров 42 к 42 подключает усилители 3 через коммутатор 46i к регистру 47 первого выходного канала 7i (фиг. 5). Таким образом, считанное

5 первое слово из накопителя 1 поступает на информационный выход 26j устройства. Аналогично работают все остальные каналы. При этом на выходе 29 блока 9 и на выходах 37 и 38 устройства прнсутствуют уровни логического нуля, свидетельствующие об от сутствни сбоев в устройстве. На выходе 29 блока 9 и на выходе 37 блока 13 будут уровни логического нуля вследствие того, что на все входы 27t-27, блока 9 и блока 13 будут поданы несовпадающие коды. 5 Поскольку выходы 29 н 37 блоков 9 и 13 являются о./ новременно н входами элемен та ИЛИ 14, то и на выходе 38 этого элемеи та будет уровень логического иуля, свиде

тельствующий об отсутствии сбоев в устройстве.

ГТрежде чем описывать дальнейшую работу устройства, поясним установку приоритетов каналов.

Установка приоритетов каналов осуществляется, исходя нз следующих соображений:

1.Младшему номеру моду.-я переключателя 54 блока 11 (на фиг. 8 крайний левый) соответствует наивысший приоритет и нарборот.

2.Включением требуемого модуля переключателя 54 осуществляется установка при оритета соответствующего канала.

3.Во всех каналах устройства должны быть установлены различные (несовпадающие) приоритеты. Установка одного и того же приоритета хотя бы в двух каналах недопустима, так как в случае совпадения кодов на выходах распределителей 44 данных входных каналов возникает сбой в устройстве.

4.Селекторы iOt - Юк под управлением блоков Hf - И к обеспечивают требуемую переком мутацию выходов распределителей 44i-44к входных каналов 6«-6и на входы 27t-27к блока 9 и, следовательно, на входы блоков , 50tv-50((.f,K сравнения (для четырехканального устройства - 50(4, 50 з 50 j).

5.При поступлении на входы 27/.-27«t блока 9 совпадающих кодов вследствие совпадения кодов адреса на входах iSj - 15к 41 16}-16к и/или на выходах распределителей 44)-44к входных каналов 6t-6к на выходах 28,-28к-1 блока 9 появляется к-1 запрещающих уровней логического нуля.

6.В соответствии с установленной коммутацией входов 27i-27к к-1 запрещающих уровней логического нуля с выходов 28)-28к-|блока 9 поступают через селекторы lOi - 10к в соответствующие входные каналы GI-бк.Тем самым обеспечивается блокировка к-1 из к каналов устройства. При этом единственным незаблокированным каналом будет канал с наивысщим приоритетом. Разрешающий уровень логической единицы для него передается от источника питания Enin-через резистор 12 (фиг. 2) и элемент И-ИЛИ 53 (фиг. 7) соответствующего селектора 10.

При полном совпадении кодов адресов, поступающих на входы 15 - 15к и 16 - 16к и/или при полном совпадении кодов на выходах распределителей 44i-44к всех входных каналов 6|-6к только один вполне определенный входной и ему соответствующий выходной канал будут открыты. Все остальные каналы будут заблокированы. При этом, как было показано, открытым каналом будет тот, который связан с источником питания Епиг. через резистор 12.

При частичном совпадении кодов адреса и/или кодов на выходах распределителей 44

некоторых входных каналов все остальные каналы открыты и работают независимо друг от друга. Те каналы, в которых произошло совпадение указанных кодов, блокируются

за исключением одного - канала с наиболь шим приоритетом. При этом на выходе 29 блока 9 появляется уровень логической единицы, свидетельствующий о произошедшем совпадении кодов в устройстве.

Как было указано, при несовпадении кЬ0 дов на выходах распределителей 44i-44кН, как следствие, при несовпадении кодов адресов, поступающих на входные каналы 6( - 6 к (первый случай) входные 6,--6к и выходные 7t-7к каналы устройства полностью

j независимы, и блок 13 и элемент ИЛИ 14 не оказывают никакого влияния на работу устройства.

Блок 13 и элемент ИЛИ 14 с соответствующими связями оказывают влияние на работоспособность устройства только в слу0 чае, когда происходит совпадение кодов (полное или частичное), и обеспечивают выявление и локализацию неправильно установленных приоритетов каналов устройства.

с Так, если в двух или нескольких каналах неправильно установлены приоритеты, например включены одноименные модули переключателей 54 в соответствующих блоках 11 (например, модули 35i в первом П, и второом llj блоках), то один и тот же приори0 тет принадлежит одновременно двум или нескольким каналам (в приведенном примере одинаковый приоритет принадлежит первому 6.1 и второму 6г каналам). Поэтому при конфликтном (одновременном) обращении процессоров .в эти каналы, т. е. по адре5 сам, коды которых совпадают на выходах распределителей 44 данных каналов, требуемой блокировки каналов не происходит, хотя на выходе 29 блока 9 появляется уровень логической единицы, свидетельствующий о

произошедшем в устройстве совпадения кодов. Отсутствие требуемой блокировки каналов приводит к сбою, поскольку все каналы с одинаковым приоритетом остаются разблокированными (в данном примере разблокироваипыми оказываются каналы 6| и 6),

5 и поэтому два или несколько процессоров обращаются по одним и тем же адресам или по адресам, коды которых отличаются перестановкой своих половин (например, коды ОПОИ 10 и 11100110). Это недопусти.мо и выявляется блоком 13. Уровни равных при оритетов с выходов блоков II (в нашем примере уровни логической единицы с выходов 351. блоков 111 и I 1г) подаются на входы блока 13 (на входы 36i соответственно). В результате на одном из выходов

J 41(-41кЭлементов И-ИЛИ 39i-39кпоявляется уровень логической единицы (в данном прн.мере на выходе 411 элемента И - ИЛИ 39i). Пройдя элемент ИЛИ 40, уровень логической единицы появляется на выходе 37 блока 13 и сигнализирует о сбое в устройстве. Если включены другие одноименные моаули -переключателей 54 различных блоков II, то на выходе другого, вполне определенного элемента И-ИЛИ блока 13 появляется уровень логической единицы, сигнализирующий о сбое в устройстве. Таким образом, отсутствие уровней логической единицы на выходе 29 блока 9, на выходе 37 блока 13 и на выходе 38 элемента ИЛИ 14 свидетельствует об отсутствии сбоев и совпадений кодов адресов при обращении к устройству. В этом случае все каналы устройства работают независимо, обеспечивая произвольную или одновременную обработку информации по к каналам. При наличии уровня логической единицы на выхо де 29 блока 9 и, следовательно, на выходе 38 элемента ИЛИ 14 и при отсутствии уров.ня логической единицы на выходе 37 блока 13 в устройстве имеет место конфликтное бращение процессоров. Приоритет отдается процессору, подключенному к каналу с наивысшим приоритетом. Остальные процессоры временно блокируются, работа устройства продолжается. При наличии уровня логической единицы на выходе 37 блока 13 и. следовательно, на выходе 38 элемента ИЛИ 14 в устройстве имеет место неправильная установка приоритета каналов, что при конфликтном обращении процессоров может привести к сбою. В этом случае требуется вмещательство оператора в работу устройства. Технико-экономическим преимуществом предложенного устройства по сравнению с известным является способность локализовать неправильно установленные приоритеты и сообщить об этом в систему и/или оператору с помощью уровней логической единицы. В конечном итоге это повышает степень автономного и системного контроля и упрощает поиск неисправностей.

1

J7

4

J«r

41

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное оперативное запоминающее устройство (его варианты) | 1982 |

|

SU1088067A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU978192A1 |

| Устройство для контроля запоминающих матриц | 1976 |

|

SU639024A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство для фиксации сбоев | 1979 |

|

SU860074A1 |

| Многоканальное запоминающее устройство | 1981 |

|

SU953669A1 |

| Устройство для сопряжения абонентов с каналами связи | 1984 |

|

SU1233158A1 |

| Многоканальная система электропитания | 1990 |

|

SU1803952A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

I. /ПНОГОКАНЛЛЬНОЕ ОПЕРАТИВНОЕ ЗАПО/ЦИНАЮЩЕЕ УСТРОЙСТВО по авт. св. № 1088067, отличающееся тем, что, с целью повыи1ения надежности устройства, в него введены первый элемент ИЛИ и дополнительный логический блок, входы которого подключены к одноименным выходам блоков ввода информации, а выход соединен с одним из входов первого элемента ИЛИ, другой вход которого подключен к второму выходу логического блока, причем выходы дополнительного логического блока и первого элемента ИЛИ являются одними из выходов устройства. 2. Устройство но п. 1, отличающееся тем, что дополнительный логический блок содержит элементы И - ИЛИ и второй элемент ИЛИ, выход которого является выходом блока, а входы подключены к выходам элементов И-ИЛИ, входы которых попарно соединены между собой по принципу сочетаний «из К по два (где К - число каналов устройства) и являются входами блока. to . о О)

Фа г 4

(26

Фиг. 5

j

J

9Jf,

ДЛг JJ,

1 ш, Ь

J5,

| I | |||

| Многоканальное оперативное запоминающее устройство (его варианты) | 1982 |

|

SU1088067A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-09-07—Публикация

1983-03-02—Подача