им (счетным) входом реверсивного счетчика, четвертый (нулевой) вход реверсивного счетчика соединен с выходом второго элемента задержки, выход реверсивного счетчика соединен с пятым входом сумматора,- входы первого и второго элементов задержки соединены с выходом индикатора контрольных отверстий.

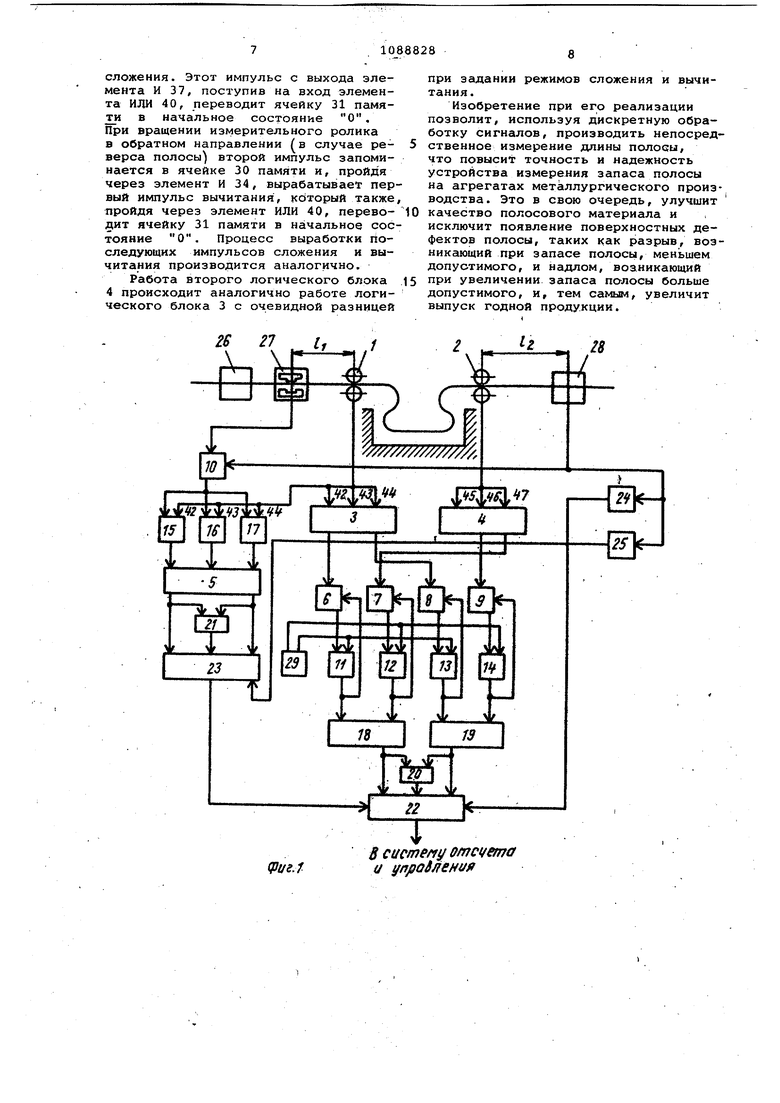

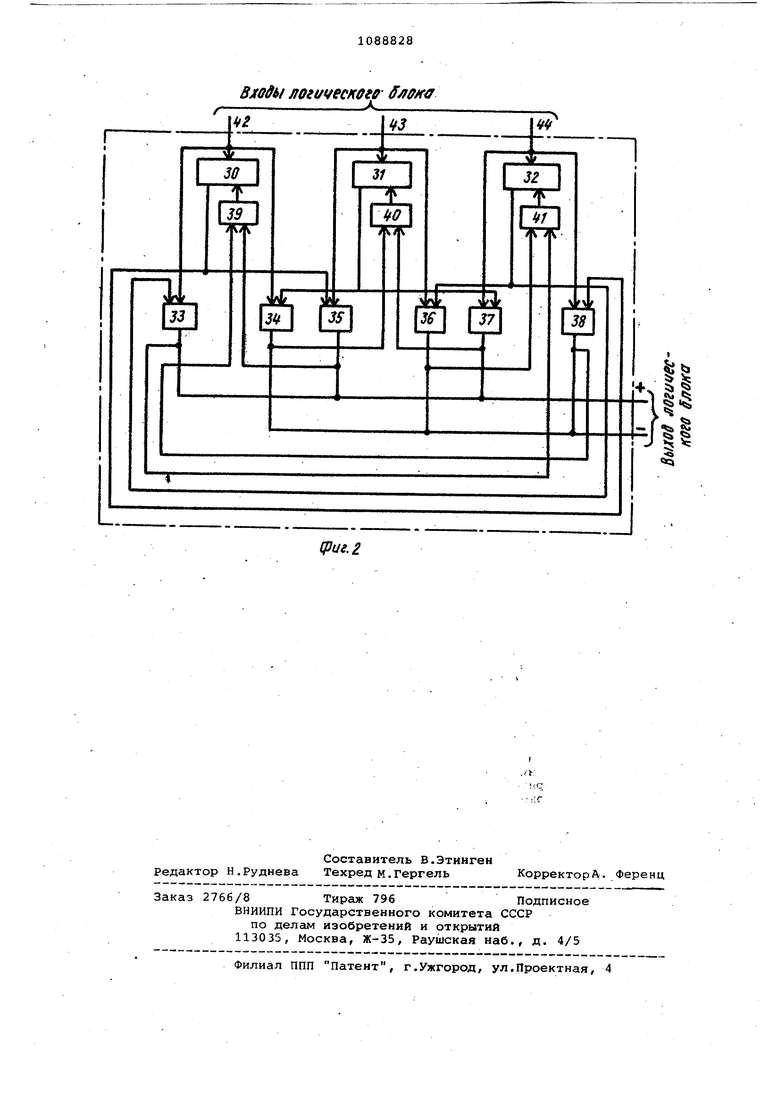

2. Устройство поп. 1, отлйчающе е с я тем, что логический :блок содержит три ячейки памяти, три элемента ИЛИ и шесть элементов И, причем входы ячеек памяти являются входами логического блока и соединены 7Г первыми входами Двух эле 4ентов И каждый, второй вход ячейки памяти , соединен с выходом соответствующего элемента ИЛИ, выход первой ячейки

памяти соединены с вторыми входами третьего и шестого элементов И, первые выходы которых соединены с входами первого элемента ИЛИ, выход второй ячейки памяти соединен с вторыми входами второго и пятого элементов И, первые выходы которых соединены с входами ВТОРОГО элемента ИЛИ, а выход третьей ячейки памяти - с вторыми входами первого и четвертого элементов И, первые выходы которых соединены с входами третьего элемента ИЛИ, вторые выходы первого, третьего и пятого элементов И объединены и являются первьа« выходом логического блока, а вторые выходы второго, четвертого и шестого элементов И являются вторым выходом логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ГЕОМЕТРИЧЕСКИХ НЕРОВНОСТЕЙ КОЛЕСНЫХ ПАР ПОДВИЖНОГО СОСТАВА12 | 1973 |

|

SU384711A1 |

| Система сбора и обработка данных для обслуживания торгового комплекса общественного питания | 1975 |

|

SU608164A1 |

| Система стабилизации запаса полосы в накопителе | 1988 |

|

SU1600882A1 |

| Устройство для контроля, учета и автоматического управления работой сеялки | 1988 |

|

SU1616531A1 |

| Устройство для регулирования петли проката | 1990 |

|

SU1763061A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| СИСТЕМА УЧЕТА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2003 |

|

RU2247994C1 |

1. УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЗАПАСА ПОЛОСЫ В НАКОПИТЕЛЬНОМ КОЛОДЦЕ, содержащее датчики скорости пояс сы и сумматор, отличающе ёс я тем, что, с целью повышения точности измерения и надежности устройства, оно дополнительно содержит пробойник контрольных отверстий, индикатор контрольных отверстий, два импульсных датчика длины полосы, ;одержащих по три импульсные головки Кс1ждый, четыре элемента ИЛИ, два элемента задержки, пять ячеек памяти, семь элементов И, реверсивный счетчик и синхронизатор импульсов, три логических блока, причем первые выходы импульсных головок первого импульсного датчика длины соединены с входами первого логического блока, выходы которого соединеиы с первыми входами первой и третьей ячеек памяти, выхода которых соединены с первыми входами соответственно первого и третьего элементов И, вторые входь которых соединены с первым выходом синхронизатора импульсов, выходы первого и третьего элементов И соединены с первыми входами соответственно первого и второго элементов ИЛИ и с вторыми входами (шинами сбро г Р -Г - f л 1 13 :v;:7;j Ciifti, .У44а;Г.У.-:А са) первой И третьей ячеек памяти соответственно, три выхода импульсных головок второго импульсного датчика соединены с входами второго логического блока, первый и второй выходы которого соединены с первыми входами второй и четвертой ячеек памяти, выходы второй и четвертой ячеек памяти соединены с первыми входами второго и четвертого элементов И, вторые входы которых соединены с вторым выходом синхронизатора импульсов, выходы второго и четвертого элементов И соединены с вторыми входами соответственно первого и второго элементов ИЛИ и с вторыми входами (шинами сброса) соответственно второй и четвертой ячеек памяти, выходы первого и (Л второго элементов ИЛИ соединены соответственно с первым и вторым вхо|Дами (шинами сложения и вычитания) сумматора и с первым и вторым входа§ ми третьего элемента ИЛИ, выход т тьего элемента ИЛИ соединен с i третьим (суммируницим) входом суммато-; ра, четвертый вход (шина сброса) коэ торого соединен с выходом первого X) элемента задержки, вторые выходы 30 импульсных головок nepiBoro импульсного датчика длины соединены с пер- ; х выми входами пятого, шестого и седью мого элементов И, вторые входы которых соединены с выходом пятой ячейки / ЭО памяти, первый и второй входы пятой ячейки памяти соединены соответственно с пробойником контрольных отверстий и с индикатором контрольных отверстий, выходы пятого, шестого и седьмого элементов И соединены с входами третьего логического блока, первый и второй выходы которого соединены собтветственно с первым и вторим входами (шинами сложения и вычитания) реверсивного счетчика и с первым и вторым входами четвертого элементов ИЛИ, выход которого соединен с треть

Изобретение относится к автоматизации производства металлического полосового материала, а именно к устройствам для определения запаса полосы и накопительном колодце.

Известно устройство для автоматического контроля количества ленты в накопительном колодце, содержащее входные и выходные зажимные ролики 1 .

Недостатком этого устройства является накопление ошибки измерения, связанное с проскальзыванием роликов относительно полос л. .

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство, содержащее стыкосварочную машину, тянущие ролики. установленные до и после накопительного колодца и кинематически связанные с датчиками скорости, и сумматорf23.

Недостатками этого устройства являются наличие ошибки определения длины полосы за счет косвенного метода получе.шя длины полосы - интегрированием скорости на аналоговых интеграторах зависимость ошибки интегрирования от скорости движения полосы и параметров интегрирования, необходимость перенастройки интеграторов в случае значительного изменения интервала между коррекциями ошибки.

Цель изобретения - повышение точности измерения и надежности устройства.

Поставленная цель достигается тем, что устройство для измерения запаса полосы в накопительном колодце, содержащее датчики

скорости полосы и сумматор, .дополнительно содержит пробойник контрольных отверстий, индикатор контрольных отверстий, два импульсных

5 датчика длины полосы, содержащих по три импульсные головки каждый, четыре элемента ИЛИ, два элемента задержки, пять ячеек памяти, семь элементов ИЛИ, реверсивный счетчик,

o синхронизатор импульсов, три логических блока, причем первые выходы импульсных головок первого импульсного датчика длины соединены с входами первого логического блока, выходы

5 которого соединены с первыми входами первой и третьей ячеек памяти,выходы которых соединены с первыми входами соответственно первого и третьего элементов И,, вторые входы которых

J соединены с первым выходом синхрони затора импульсов, выходы первого и Третьего элементов И соединены с первыми входами соответственно первого и второго элементов ИЛИ и с вторыми входами (шинами сброса) первой и третьей ячеек памяти соответственно, три выхода импульсных головок второ±43 импульсного датчика соединены с входами втброго логического блока, первый и второй выходы которого сое0 динены с первыми входами второй и четвёртой ячеек памяти, выходы второй и четвертой ячеек памяти соединены с первыми входами второго и четвертого элементов И, вторые входы

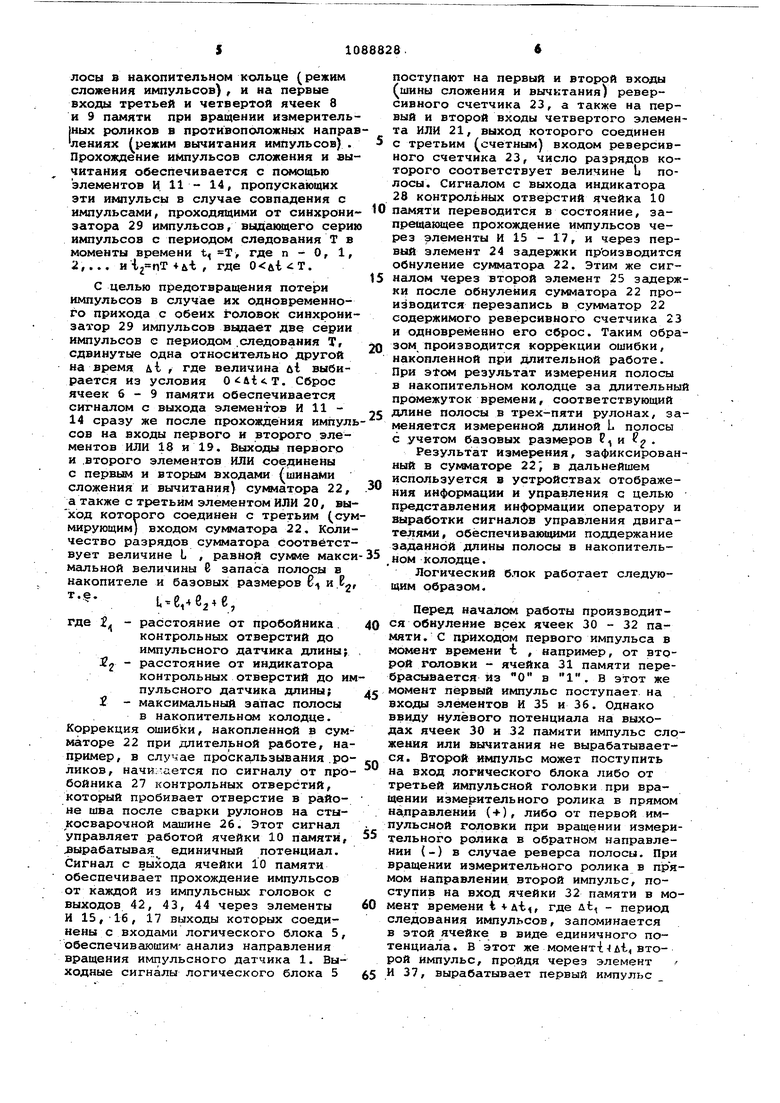

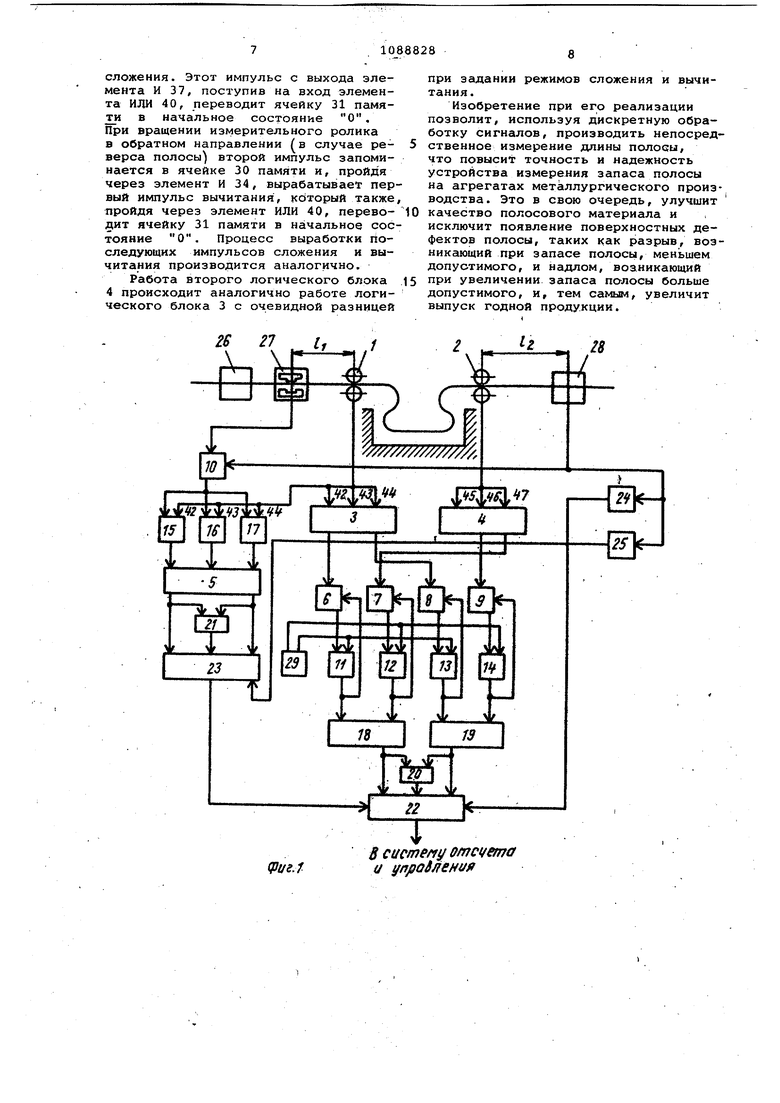

5 которых соединены с вторым выходом .синхронизатора импульсов,выходы второго и четвертого элементов И соединены с вторыми входами соответственно дервого и ВТОРОГО элементов ИЛИ и с вто0 рыми входами {шинами сброса) соответ ственно второй и четвертой ячеек памяти , выходы первого и второго элементов ИЛИ соединены.. соответственно с первым и вторым входами (шинами сложения и вычитания) cyNiMaTopa и с первым и вторым входами третьего эле мента ИЛИ, выход третьего элемента ИЛИ соединен с третьим (суммирующим) входом сумматора, четвертый вход (ши на сброса которого соединен с выходом первого элемента задержки, вторые выходы импульсных головок первого импульсного датчика длины соедине ны с первыми входами пятого, шестого и седьмого элементов И, вторые входы которых соединены с выходом пятой ячейки памяти; первый и второй входы пятоЛ ячейки памяти соединены соответственно с пробойником контрольных отверстий и с индикатором контроль/ных; отверстий, выходы пятого, шестого и седьмого элементов ИЛИ соединены с входами: третьего логического блока, первый и второй выходы которого соединены соответственно с-первым и вторым входами (шинами сложе- . НИН и вычитания) реверсивного счетчи ка и с первым и вторым входами четвертого элементов ИЛИ,выход которого соединен с третьим (счетным) входом. реверсивного счетчика, четвертый (ну левойУ вход реверсивного счетчика соединен .с выходом второго элемента задержки, выход реверсивного счетчика соединен с пятым входом сумматора входы первого -и второго элементов за держки соединены с выходом индикатора контрольных отверстий. Логический блок содержит три ячей ки памяти, три элемента ИЛИ и шесть элементов И, причем входы ячеек памя ти являются входами логического бло ка и соединены с первыми входами двух элементов И каждый, второй вход ячейки памяти соединен с выходом соответствующего элемента ИЛИ, выход первой ячейки памяти соединен с вторыми входами третьего и шестого элементов И, первые выходы которых соединены с входами первого элемента ИЛИ, выход второй ячейки памяти соединен с вторыми входами второго и пятого элементов И, первые выходы которых соединены с входами второго элемента ИЛИ, а выход третьей ячейки памяти - с вторыми входами первого и четвертого элементов И, первые выходы которых соединены -с входами: третьего элемента ИЛИ, вторые выходы первого, третьего и пятого элемен тов И объединеныи являются первым выходом логического блока, а вторые выходы второго, четвертого и шестого элементов И являются вторым выходом логического блока. . На фиг. 1 изображена структурная схема устройства; на фиг. 2 - структурная схема логического блока. Устройство содержит первый 1 и второй 2 импульсные датчики длины полосы, первый 3, второй 4 и третий 5 логические блоки, ячейки 6-10 памяти с первой по пятую, элементы И 11-17 с первого по седьмой, элементы ИЛИ 18-21 с первого по четвертый, сумматор 22 реверсивный счетчик 23, первый 24 и второй 25 элементы задержки, стыкосварочную машину 26, пробойник 27 контрольных отверстий, индикатор 28 контрольных отверстий, синхсюнизатор 29 импульсов. Логический блок 3 содержит первую 30, вторую 31 и третью 32 ячейки памяти, шесть логических элементов И 33-38, три логических элемента ИЛИ 39 - 41, Каждый из импульсных датчиков 1 длины полосы содержит по три импульсные головки с выходами 42, 43, 44 и 45, 46, 47 соответственно. Выходы каждой из трех импульсных головок, например выходы 42 - 44 первого импульсного датчика 1 длины, соединены с первыми входами ячеек 30 - 32 памяти соответственно, а также соединены попарно с первыми входами элементов И 33 - 38 соответственно, выходы ячеек 30, 31, 32 памяти соединены попарно с вторыми входами элементов и 38 и 35, 34 и 37, 36 и 33 соответственно, первые выходы элементов И 38 и 35, 34 и 37, 36 и 38 попаршо соединены с первым и вторым входами элементов ИЛИ 39, 40 и 41 соответственно, выходы которых соединены с вторыми входами (шинами сброса) ячеек 30 - 32 памяти,вторые выходы элементов и 33, 35 и 37 подключены к первому выходу логического блока 3, котог-лй соединен с первым входом первой ячейки 6 памяти, а вторые выхода элементов И 34, 36, 38 подключены к второму выходу логического блока 3, который соединен с первым входом ячейки 8 памяти. Электрические связи для головок первого импульсного датчика 1 будут аналогичны электрическим связям для головок второго импульсного датчика 2. Устройство работает следующим образом. : Предварительно производится обнуление реверсивного счетчика, сумматора, ячеек памяти. Сигналы от каждой из импульсных головок поступают на входы первого и второго логическ-их блоков 3 и 4 соответственно, которые анализируют направление вращения импульсных датчиков 1 и 2 длины. В зависимости от направления вращения импульсных датчиков логические блоки 3 и 4 выдают импульсы, которые поступают на первые входы первой и второй ячеек 6 и 7 памяти при вращении измерительных роликов в направлениях, обеспечивающих увеличение запаса no-J лосы в накопительном кольце (режим сложения импульсов), и на первые входы третьей и четвертой ячеек 8 и 9 памяти при вращении измеритель 1ИЫХ роликов в противоположных направ лениях (режим вычитания импульсов) . Прохождение импульсов сложения и вы читания обеспечивается с элементов И 11 - 14, пропускающих эти импульсы в случае совпадения с импульсами, проходящими от синхрони затора 29 импульсов, выдс1киаего сери импульсов с периодом следования Т в моменты времени t, Т где п - О, 1, 2,... Hi2 nT+&t, где . С целью предотвращения потери импульсов в случае их одновременного прихода с обеих головок синхрони затор 29 импульсов выдает две серии импульсов с периодом .следования Т, сдвинутые одна относительно другой на время &i , где величина ut выбирается из условия О At Т. Сброс ячеек 6-9 памяти обеспечивается сигналом с выхода элементов И 11 14 сразу же после прохождения импул сов на входы первого и второго элементов ИЛИ 18 и 19. Выходы первого и .второго элементов ИЛИ соединены с первым и вторым входами (шинами сложения и вычитания} сумматора 22, а также с третьим элементом ИЛИ 20, вы ход которого соединен с третьим (сум мирующим) входом сумматора 22, Коли чество разрядов сумматора соответствует величине L , равной сумме макси мальной величины в запаса полосы в накопителе и базовых размеров 6 и.В где 2 расстояние от пробойника контрольных отверстий до импульсного датчика длины; расстояние от индикатора контрольных отверстий до им пульсного датчика длины; максимальный запас полосы в накопительном колодце. Коррекция ошкбкя, накопленной в сумматоре 22 при длительной работе, например, в случае проскальзывания.роликов, начк;ается по сигналу от пробойника 27 контрольных отверстий, который пробивает отверстие в районе шва после сварки рулонов на сты сосварочной машине 26. Этот сигнал управляет работой ячейки 10 памяти, вырабатывая единичный потенциал. Сигнал с выхода ячейки 10 памяти обеспечивает прохождение импульсов от каждой из импульсных головок с выходов 42, 43, 44 через элементы И 15, 16, 17 выходы которых соединены с входами логического блока 5, обеспечивающим- анализ направления вращения импульсного датчика 1. Выходные сигналы логического блока 5 поступают на первый и второй входы шины сложения и вычитания) реверсивного счетчика 23, а также на первый и второй входы четвертого элемента ИЛИ 21, выход которого соединен с третьим (счетным) входом реверсивного счетчика 23, число разрядов которого соответствует величине Ь полосы. Сигналом с выхода индикатора 28 контрольных отверстий ячейка 10 памяти переводится в состояние, запрещающее прохождение импульсов через элементы И 15 - 17, и через первый элемент 24 задержки прЪизводится обнуление сумматора 22. Этим же сигналом через второй элемент 25 задержки после обнуления сумматора 22 производится перезапись в сумматор 22 содержимого реверсивного счетчика 23 и одновременно его сброс. Таким образом производится коррекции ошибки, накопленной при длительной работе. При этом результат измерения полосы в накопительном колодце за длительный промежуток времени, соответствующий длине полосы в трех-пяти рулонах, заменяется измеренной длиной L полосы с учетом базовых размеров Р и . Результат измерения, зафиксированный в сумматоре 22 в дальнейшем используется в устройствах отображения информации и управления с целью представления информации оператору и выработки сигналов управления двигателями, обёспечиваюпшми поддержание заданной длины полосы в накопитель,ном колодце. Логический блок работает следующим образом. Перед начсшсж работы производится обнуление всех ячеек 30 - 32 памяти. С приходом первого импульса в момент времени t , например, от второй головки - ячейка 31 памяти перебрасывается из О в 1. в этот же момент Первый импульс поступает на входы элементов И 35 и 36. Однако ввиду нулевого потенциала на выходах ячеек 30 и 32 памяти импульс сложения или вычитания не вырабатывается. Второй импульс может поступить на вход логического блока либо от третьей импульсной головки при вращении измерительного ролика в прямом направлений (-), либо от первой импульсной головки при вращении измерительного ролика в обратном направлении {-) в случае реверса полосы. При вращении измерительного ролика в прямом направлении второй импульс, поступив на вход ячейки 32 памяти в момент времени i +Ai, где At, - период следования импульсов, запоминается в этой ячейке в виде единичного потенциала В этот же мoмeнтi дt второй Импульс, пройдя через элемент И 37, вырабатывает первый импульс

сложения. Этот импульс с выхода элемента И 37, поступив на вход элемента ИЛИ 40, переводит ячейку 31 памяО

ти в начальное состояние

При вращении измерительного ролика в обратном направлении (в случае ре- 5 верса полосы) второй импульс запоминается в ячейке 30 памяти и, пройдя через элемент И 34, вырабатывает первый импульс вычитания, который также, пройдя через элемент ИЛИ 40, перево- 10 дит ячейку 31 памяти в начальное состояние О. Процесс выработки Последующих импульсов сложения и вычитания производится аналогично.

Работа второго логического блока 15 4 происходит аналогично работе логического блока 3 с очевидной разницей

при задании режимов сложения и вычитания.

Изобретение при его реализации позволит, используя дискретную обработку сигналов, производить непосредственное измерение длины полосы, что повысит точность и надежность устройства измерения запаса полосы на агрегатах металлургического производства . Это в свою очередь, улучшит качество полосового материала и исключит появление поверхностных дефектов полосы, таких как разрыв, возникающий при запасе полосы, меньшем допустимого, и надлом, возникающий при увеличении запаса полосы больше допустимого, и, тем самым, увеличит выпуск годной продукции.

I Г

(риг.Т

22

В систепу omci/ffna и ynpo /feHUii

Bjtoditi non/vecKOfo-

IE

П

UU

(риг, I

-ii

:}

-il

lil

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Прибор для исследования слуха и колебания мембран | 1928 |

|

SU10224A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-04-30—Публикация

1983-02-15—Подача