;4

-П

-т

ел

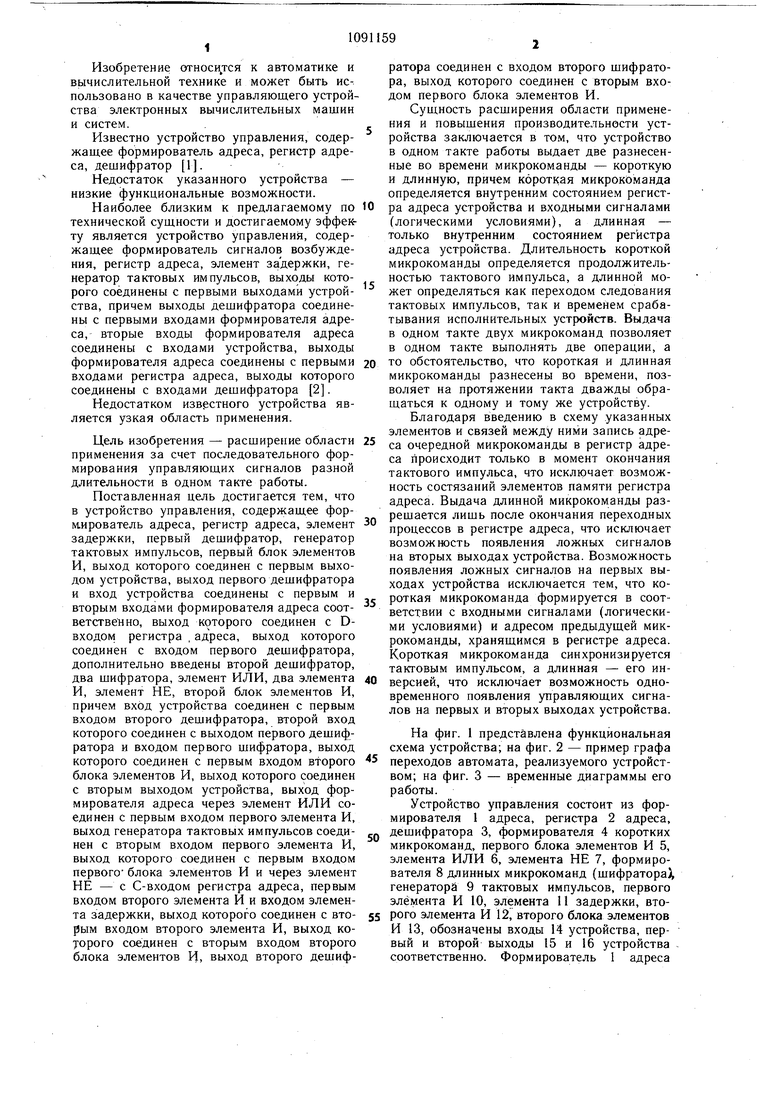

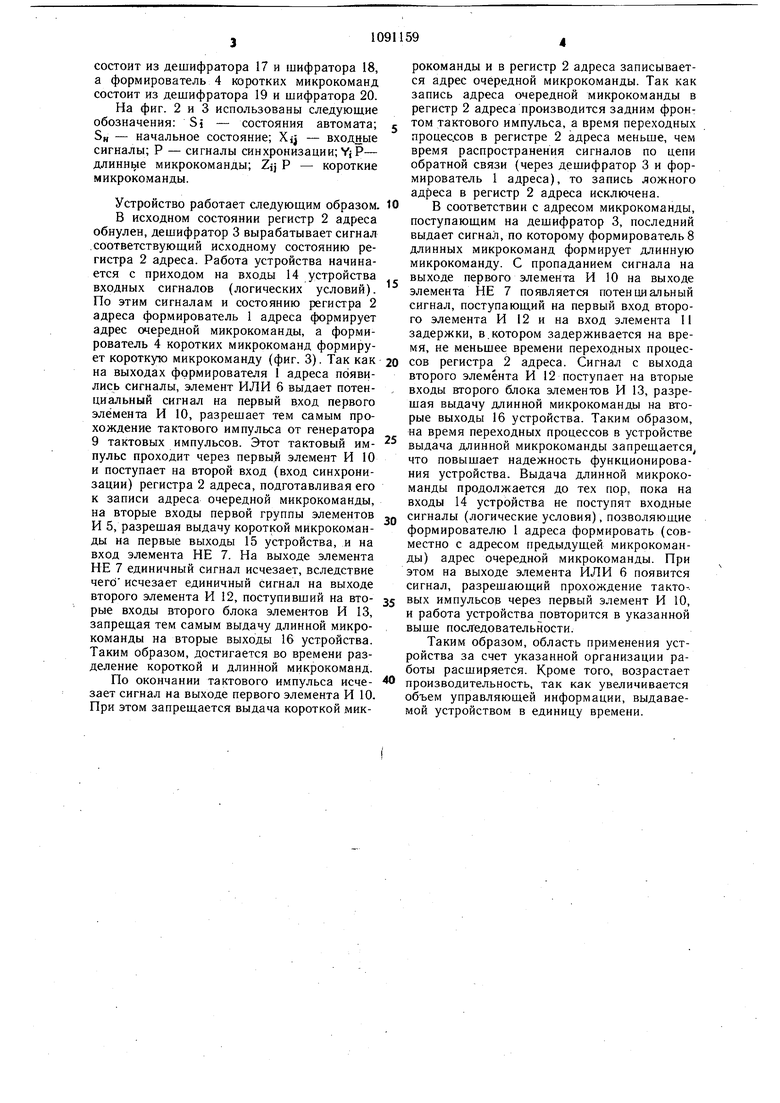

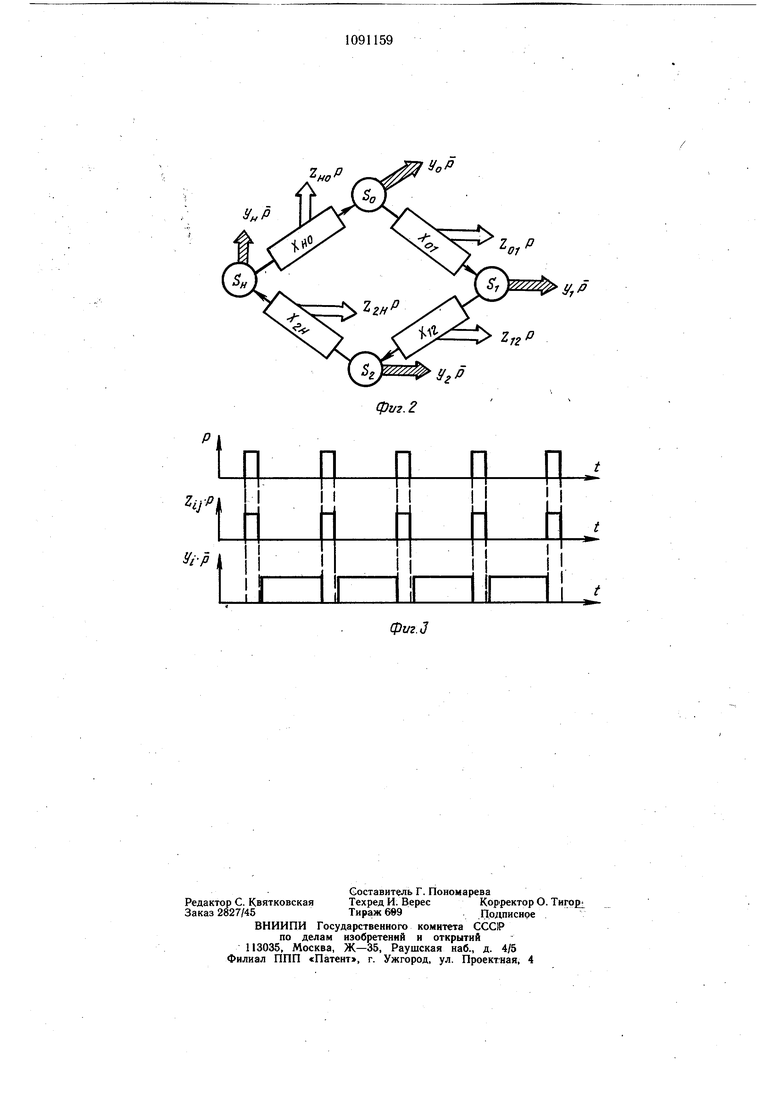

со Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве управляющего устройства электронных вычислительных машин и систем. Известно устройство управления, содержащее формирователь адреса, регистр адреса, дешифратор 1. Недостаток указанного устройства - низкие функциональные возможности. Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство управления, содержащее формирователь сигналов возбуждения, регистр адреса, элемент задержки, генератор тактовых импульсов, выходы которого соединены с первыми выходами устройства, причем выходы дешифратора соединены с первыми входами формирователя адреса, вторые входы формирователя адреса соединены с входами устройства, выходы формирователя адреса соединены с первыми входами регистра адреса, выходы которого соединены с входами дешифратора 2. Недостатком известного устройства является узкая область применения. Цель изобретения - расширение области применения за счет последовательного формирования управляющих сигналов разной длительности в одном такте работы. Поставленная цель достигается тем, что в устройство управления, содержащее форм.ирователь адреса, регистр адреса, элемент задержки, первый дещифратор, генератор тактовых импульсов, первый блок элементов И, выход которого соединен с первым выходом устройства, выход первого дешифратора и вход устройства соединены с первым и вторым входами формирователя адреса соответствег1но, выход которого соединен с Dвходом регистра , адреса, выход которого соединен с входом первого дешифратора, дополнительно введены второй дешифратор, два шифратора, элемент ИЛИ, два элемента И, элемент НЕ, второй блок элементов И, причем вход устройства соединен с первым входом второго дешифратора, второй вход которого соединен с выходом первого дешифратора и входом первого шифратора, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с вторым выходом устройства, выход формирователя адреса через элемент ИЛИ соединен с первым входом первого элемента И, выход генератора тактовых импульсов соединен с вторым входом первого элемента И, выход которого соединен с первым входом первого блока элементов И и через элемент НЕ - с С-входом регистра адреса, первым входом второго элемента И и входом элемента задержки, выход которого соединен с вторым входом второго элемента И, выход коjoporo соединен с вторым входом второго блока элементов И, выход второго дешифратора соединен с входом второго шифратора, выход которого соединен с вторым входом первого блока элементов И. Сущность расширения области применения и повышения производительности устройства заключается в том, что устройство в одном такте работы выдает две разнесенные во времени микрокоманды - короткую и длинную, причем короткая микрокоманда определяется внутренним состоянием регистра адреса устройства и входными сигналами (логическими условиями), а длинная - только внутренним состоянием регистра адреса устройства. Длительность короткой микрокоманды определяется продолжительностью тактового импульса, а длинной может определяться как переходом следования тактовых импульсов, так и временем срабатывания исполнительных устройств. Выдача в одном такте двух микрокоманд позволяет в одном такте выполнять две операции, а то обстоятельство, что короткая и длинная микрокоманды разнесены во времени, позволяет на протяжении такта дважды обращаться к одному и тому же устройству. Благодаря введению в схему указанных элементов и связей между ними запись адреса очередной микрокоманды в регистр адреса происходит только в момент окончания тактового импульса, что исключает возможность состязаний элементов памяти регистра адреса. Выдача длинной микрокоманды разрешается лищь после окончания переходных процессов в регистре адреса, что исключает возможность появления ложных сигналов на вторых выходах устройства. Возможность появления ложных сигналов на первых выходах устройства исключается тем, что короткая микрокоманда формируется в соответствии с входными сигналами (логическими условиями) и адресом предыдущей микрокоманды, хранящимся в регистре адреса. Короткая микрокоманда синхронизируется тактовым импульсом, а длинная - его инверсией, что исключает возможность одновременного появления управляющих сигналов на первых и вторых выходах устройства. На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - пример графа переходов автомата, реализуемого устройством; на фиг. 3 - временные диаграммы его работы. Устройство управления состоит из формирователя 1 адреса, регистра 2 адреса, дешифратора 3, формирователя 4 коротких микрокоманд, первого блока элементов И 5, элемента ИЛИ 6, элемента НЕ 7, формирователя 8 длинных микрокоманд (шифратора генератора 9 тактовых импульсов, первого элемента И 10, элемента 11 задержки, второго элемента И 12, второго блока элементов И 13, обозначены входы 14 устройства, первый и второй выходы 15 и 16 устройства соответственно. Формирователь 1 адреса

состоит из дешифратора 17 и шифратора 18, а формирователь 4 коротких микрокоманд состоит из дешифратора 19 и шифратора 20. На фиг. 2 и 3 использованы следуюш.ие обозначения: Si - состояния автомата; 5и - начальное состояние; Xij - входные сигналы; Р - сигналы синхронизации; YjP- длиннь1е микрокоманды; Zjj Р - короткие микрокоманды.

Устройство работает следующим образом. В исходном состоянии регистр 2 адреса обнулен, дешифратор 3 вырабатывает сигнал .соответствующий исходному состоянию регистра 2 адреса. Работа устройства начинается с приходом на входы 14 устройства входных сигналов (логических условий). По этим сигналам и состоянию регистра 2 адреса формирователь 1 адреса формирует адрес очередной микрокоманды, а формирователь 4 коротких микрокоманд формирует короткую микрокоманду (фиг. 3). Так как на выходах формирователя 1 адреса появились сигналы, элемент ИЛИ 6 выдает потенциальный сигнал на первый вход первого элемента И 10, разрещает тем самым прохождение тактового импульса от генератора 9 тактовых импульсов. Этот тактовый импульс проходит через первый элемент И 10 и поступает на второй вход (вход синхронизации) регистра 2 адреса, подготавливая его к записи адреса очередной микрокоманды, на вторые входы первой группы элементов И 5, разрещая выдачу короткой микрокоманды на первые выходы 15 устройства, и на вход элемента НЕ 7. На выходе элемента НЕ 7 единичный сигнал исчезает, вследствие чего исчезает единичный сигнал на выходе второго элемента И 12, поступивший на вторые входы второго блока элементов И 13, запрещая тем самым выдачу длинной микрокоманды на вторые выходы 16 устройства. Таким образом, достигается во времени разделение короткой и длинной микрокоманд.

По окончании тактового импульса исчезает сигнал на выходе первого элемента И 10. При этом запрещается выдача короткой микрокоманды и в регистр 2 адреса записывается адрес очередной микрокоманды. Так как запись адреса очередной микрокоманды в регистр 2 адреса производится задним фронтом тактового импульса, а время переходных процессов в регистре 2 адреса меньше, чем время распространения сигналов по цепи обратной связи (через дешифратор 3 и формирователь 1 адреса), то запись ложного адреса в регистр 2 адреса исключена.

В соответствии с адресом микрокоманды, поступающим на дешифратор 3, последний выдает сигнал, по которому формирователь 8 длинных микрокоманд формирует длинную микрокоманду. С пропаданием сигнала на выходе первого элемента И 10 на выходе элемента НЕ 7 появляется потенциальный сигнал, поступающий на первый вход второго элемента И 12 и на вход элемента И задержки, в.котором задерживается на время, не меньшее времени переходных процессов регистра 2 адреса. Сигнал с выхода второго элемента И 12 поступает на вторые входы второго блока элементов И 13, разрешая выдачу длинной микрокоманды на вторые выходы 16 устройства. Таким образом, на время переходных процессов в устройстве выдача длинной микрокоманды запрещается что повышает надежность функционирования устройства. Выдача длинной микрокоманды продолжается до тех пор, пока на входы 14 устройства не поступят входные сигналы (логические условия), позволяющие формирователю 1 адреса формировать (совместно с адресом предыдушей микрокоманды) адрес очередной микрокоманды. При этом на выходе элемента ИЛИ 6 появится сигнал, разрешающий прохождение такто-. вых импульсов через первый элемент И 10, и работа устройства повторится в указанной выше последовательности.

Таким образом, область применения устройства за счет указанной организации работы расширяется. Кроме того, возрастает производительность, так как увеличивается объем управляющей информации, выдаваемой устройством в единицу времени.

lunP

НО

Р

УоР

2г2

/,Р

фш.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1019449A1 |

| Микропрограммное устройство управления | 1981 |

|

SU955061A1 |

| Микропрограммное устройство управления | 1981 |

|

SU951306A2 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

. УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее формирователь адреса, регистр адреса, элемент задержки, первый дешифратор, генератор тактовых импульсов, первый блок элементов И, выход которого соединен с первым выходом устройства, выход hepBoro дешифратора и вход устройства соединены с первым и вторым входами формирователя адреса соответственно, выход которого соединен с D-входом регистра адреса, выход которого соединен с входом первого дешифратора, отличающееся тем, что, с целью расширения области применения за счет последовательного формирования управляющих сигналов разной длительности в одном такте работы, оно дополнительно содержит второй дешифратор, два шифратора, элемент ИЛИ, два элемента И, элемент НЕ, второй блок элементов И, причем вход устройства соединен с первым входом второго дешифратора, второй вход которого соединен с . выходом первого дешифратора и входом первого шифратора, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с вторым выходом устройства, выход формирователя адреса через элемент ИЛИ соединен с первым входом первого элемента И, выход генератора тактовых импульсов соединен с вторым входом первого элемента И, выход которого соединен с первым входом первого i блока элементов И и через элемент НЕ - с С-входом регистра адреса, первым входом (П второго элемента И и входом элемента задержки, выход которого соединен с вторым входом второго элемента И, выход которого соединен с вторым входом второго блока элементов И, выход второго дешифратора соединен с входом второго шифратора, выход которого соединен с вторым входом первого блока элементов И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Баранов С | |||

| И | |||

| Синтез микропрограммных автоматов | |||

| Л., «Энергия, 1974, с | |||

| Питательный кран для вагонных резервуаров воздушных тормозов | 1921 |

|

SU189A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство управления | 1978 |

|

SU675424A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-07—Публикация

1983-01-11—Подача