йий регистра микрокоманд, группа выходов сумматора по модулю два является второй группой управляющих выходов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

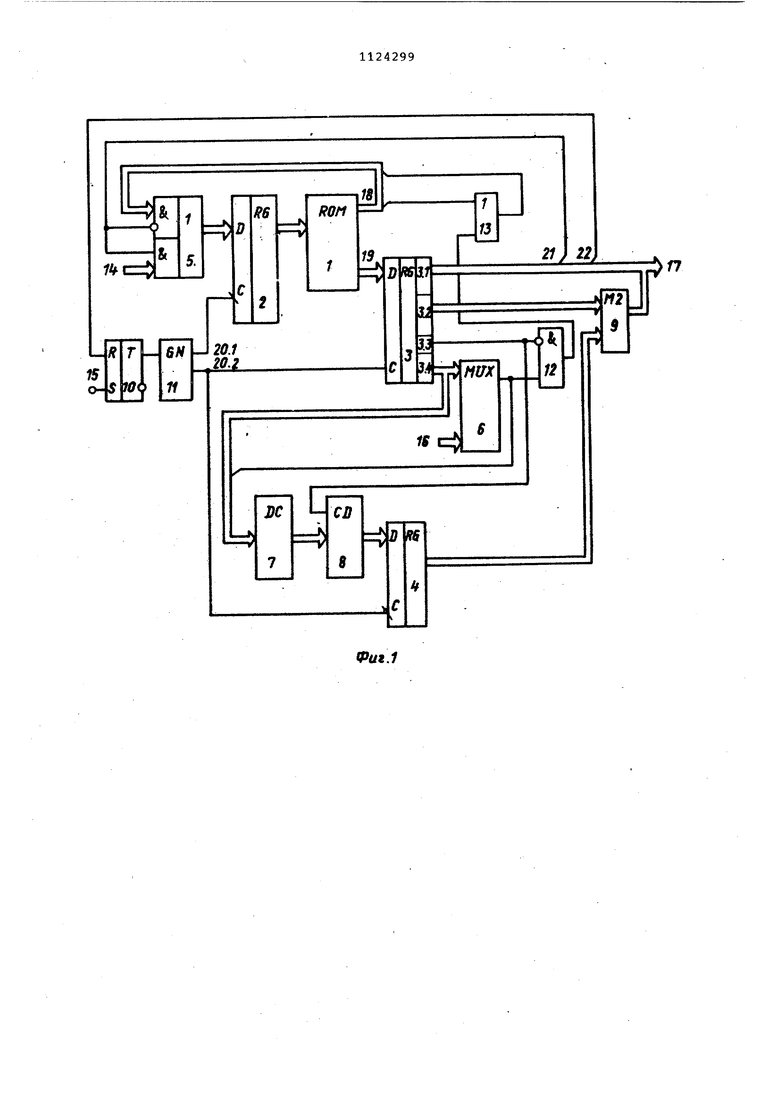

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, коммутатор, мультиплексор, триггер, генератор тактовЫх импульсов, элемент И, элемент ИЛИ, причем группа входов кода команды устройства соединена с первой группой информационных входов коммутатора, вход пуска устройства соединен с входом установки в единицу триггера, выход которого соединен с входом запуска генератора тактовых импульсов, первый выход которого соединен с входом синхронизации регистра адреса, информационный вход которого соединен с выходом коммутатора, выход регистра адреса соединен с адресным входом блока памяти микрокоманд, 1-й выход (i l,2,...,n,n - разрядность немодифицируемой части адреса) немодифицируемых разрядов адреса блока памяти микрокоманд соединен с 1-м информационным входсм второй группы коммутатора, (п + 1)-й информационный вход второй группы которого соединен с выходом элемента ИЛИ, (п + 1)-й выход модифицируемого разряда адреса блока памяти микрокоманд соединен с первым входом элемента ИЛИ, выход кода операции блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, вход синхронизации которого соединен с вторым выходом генератора тактовых импульсов, группа k-выходов (V- разрядность кода логических условий ) кода логических условий регистра микрокоманд соединена с группой управляющих входов мультиплексора, группа информационных входов которого является группой входов логических условий устройства, группа выходов немoдифициpye ttax разрядов кода микроопераций регистра микрокоманд является первой группой управляющих выходов устройства, выходы конца команды и конца работы регистра микроа S команд соединены соответственно с управляющим входом коммутатора и с (О входом установки в ноль триггера, отличающееся тем, что, с целью сокращения объема оборудования, устройство содержит регистр ко да модификации, сумматор по модулю два, дешифратор, шифратор, причем k-выходов кода логических условий регистра микрокоманд соединены с k-входами дешифратора, (v+ 1)-й N9 вход которого соединен с выходом 4; to е ;о мультиплексора и с прямым входом элемента И, инверсный вход которого соединен со стробирующим входом шифратора и с выходом признака модификации кода микроопераций регистра микрокоманд, выход элемента И соединен с вторым яходом элемента ИЛИ, выход дешифратора соединен с входом птифратора, выход которого соединен с информационным входом регистра кода модификации, вход синхронизации которого соединен с вторым выходом генератора тактовых импулвсов, группа выходов регистра кода модификации соединена с первой группой входов сумматора по модулю два, вторая группа входов которого соединена с группой выходов модифицируемых разрядов кода микроопера- .

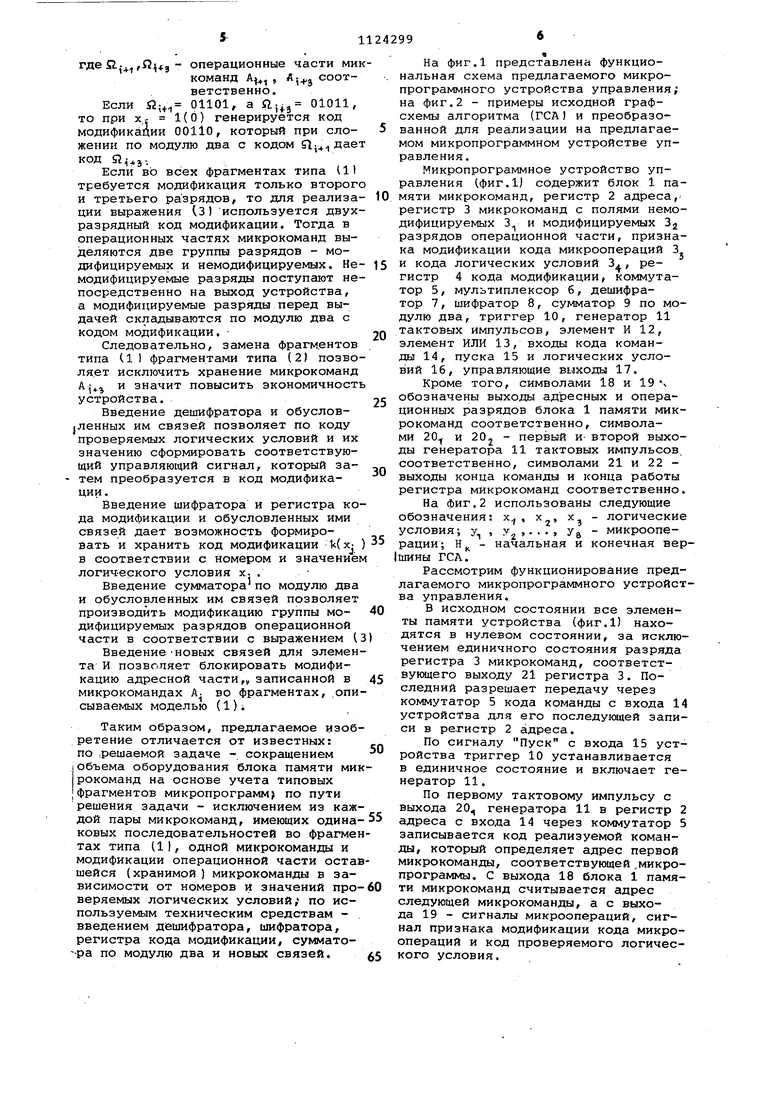

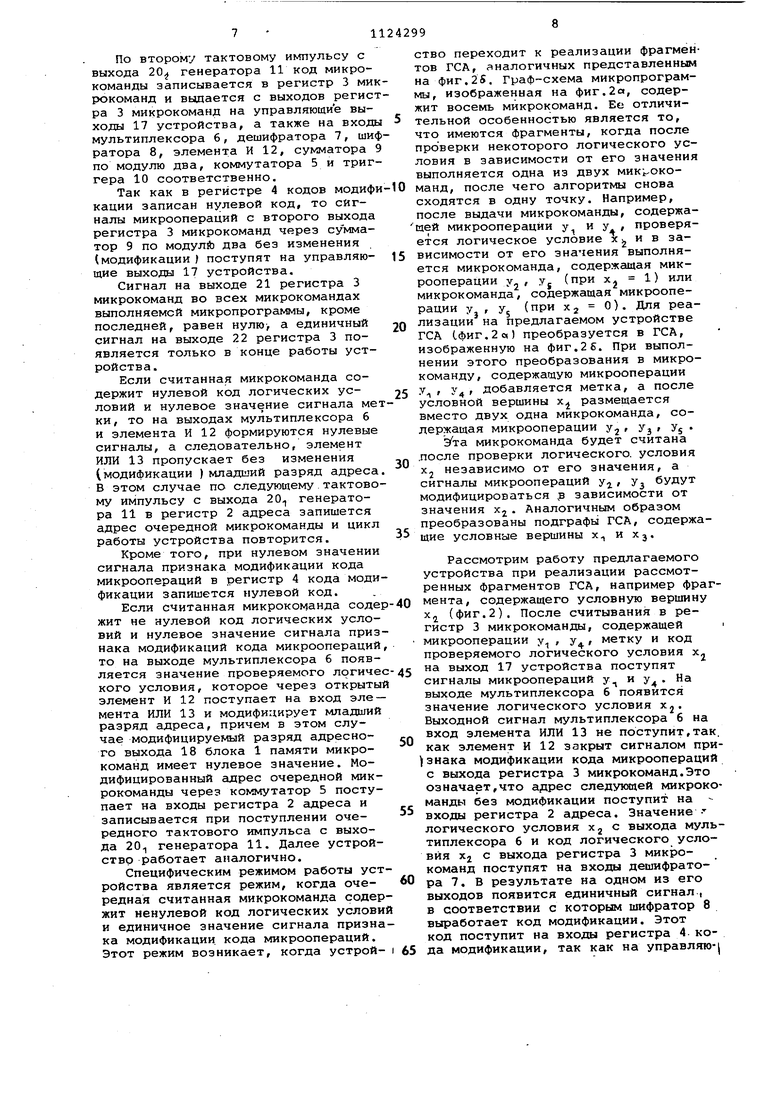

Изобретение относится к цифровой вычислительной технике и может быть использовано при проектировании мик ропрограммных устройств управления для ЭВМ и вычислительных систем. Известно микропрограммное устрой ство управления, содержащее блок па мяти, микрокоманд, регистр адреса, регистр микрокоманд, блок синхронизации, формирователь адреса, буферный регистр, элементы И, ИЛИ ClJНедостатл оМуказанного устройств является низкая экономичность, обус ловленная наличием избыточности в операционных частях микрокоманд. Известно микропрограммное устройство управления, содержащее регистры адреса и микрокоманд, блок памяти микрокоманд, генератор такто вых импульсов, триггер управления, блок формирования адреса, элементы И, ИЛИ, дешифратор С21. Недостатком этого устройства является низкое быстродействие, вызванное тем, что формирование очередной операционной микрокоманды осуществляется после считывания базовой микрокоманд путем циклического сдвига кода на заданное число разрядов. Наиболее близким к изобретению по технической сущности и достигаемому положительному эффекту является микропрограммное устройство, управления, содержащее лок памяти микрокоманд, регистры адреса и микрокоманд, триггер пуска, генератор тактовых импульсов, коммутатор, мультиплексор и элемент И, причем вход пуска .устройства и выход конца работы регистра микрокоманд соединены соответственно с единичным и нулевым входами триггера пуска, выход которого соединен с входом генератора тактовых импульсов, первый и второй выходы которого соединены с входами синхронизации регист ров адреса и микрокоманд соответственно, выход конца команды регист ра микрокоманд и вход кода операции устройства соединены соответственно с управля,кх(им и первь1м информационным входами коммутатора, выход которого соединен с информацион ным входом регистра адреса, выход которого соединен с входом блока памяти микрокоманд, первый выход которого соединен с информационным входом регистра микрокоманд, второй и третий выходы блока памяти микрокоманд соединены с вторым информационным входом коммутатора и первым входом элемента ИЛИ соответственно, выход которого соединен с третьим информационным входом коммутатора, выходы микроопераций и кода логических условий регистра микрокоманд и вход логических условий устройства соединены соответственно с выходом микроопераций устройства, адресным и информационным входами мультиплексора, выход которого соединен с вторым входом элемента . Недостатком указанного устройства является низкая экономичность, обусловленная избыточностью оборудования блока памяти микрокоманд, вы -званной тем, что структура устройства и имеющиеся технические средства недостаточно учитывают типовые фрагменты, встречающиеся в микропрограммах, реализуемых устройством. Примером такого типового фрагмента является фрагмент, описываемый следующей логической схемой алгоритма: ...А.Х.ГА.А.,..., ,,,и,,5... (1) где А., А., А).а , AV - микрокоманды;. X - логическое условие , от которого осуществляется переход к микрокомандам А(при или (при х- 0) ; LOg - тождественно ложч ноелогическое , , условие,которое обеспечивает безусловный . переход от микрокоманды к микрокоманде А,Оптимальной особенностью данного типового фрагмента является то, что микрокоманды, следующие в микропрограмме за ветвлением, имеют общего последователя. Следовательно, такие микрокоманды имеют одинаковые адресные части и идентичное .содержимое полей кода логических условий и отличаются только операционными частями, Поскольку операционные части указанных микрокоманд отличаются. как правило, небольшим числом ( двумя-тремя J разрядов, то, следовательно, такие фрагменты могут быть реализованы с использованием меньшего объема оборудования блока памя ти. Тогда объем избыточного оборудования блока памяти в прототипе мо но вычислить по формуле изЕ --™ V, ф.еФ где m - разрядность микрокоманд; Ф - множество типовых фрагментов, списываемых выражением (1) ; 6 - число типовых фрагментов для-i-ro логического условия. Таким образом, отсутствие в прототипе технических средств, которые учитывают наличие в микропрограммах фрагментов рассмотренного типа, сни жает его экономичность. Целью изобретения является сокра щение объема об6рудовани5т устройства .. Поставленная цельдостигается тем, что в микропрограммное устройство управления, содержащее блок па мяти микрокоманд, регистр адреса, р гистр микрокоманд, коммутатор, муль типлексор, триггер, генератор такто вых импульсов, элемент И, элемент И причем группа входов кода команды устройства соединена с первой груп прй информационных входов коммутатора, вход пуска устройства соедине с входом установки в единицу тригге ра, выход которого соединен с входо запуска генератора тактовых импульсов, первый выход которого соединен с входом синхронизации регистра ад реса, информационный вход которого соединен с выходом коммутатора, выход регистра адреса соединен с адре ным входом блока памяти микрокоманд 1-й выход (i 1, 2,..., п; п - раз рядность немодифицируемой части адреса ) немодифицируемых разрядов адреса блока Пс1мяти микрокоманд соединен с i-M информационньам входом второй группы коммутатора, (п+1)-й информационный вход второй группы которого соединен с выходом элемента ИЛИ, (п+1)-й выход модифицируемо го разряда адреса блока памяти микрокоманд соединен с первым входом элемента ИЛИ, выход кода операции блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, вход синхронизации которого соединен с вторым выходом генератора тактовых импульсов, груп па k-выходов (k- разрядность кода логических условий/ кода логических условий регистра микрокоманд соединена с группой управляющих входов мультиплексора, группа информацион;:ных входов которого является группой входов логических условий устройства, группа выходов немодифйцируемкх разрядов кода микроопераций регистра микрокоманд является первой группой управляющих выходов устройства, выходы конца команды к конца работы регистра микрокоманд соединены соответственно с управляющим входом коммутатора и с входом установки в ноль триггера, введены регистр кода модификации, сумматор по модулю два, дешифратор, шифратор, причем k-выходов кода логических условий регистра микрокоманд соединены с 1 -входами дешифратора, ()-и вход которого соединен с выходом мультиплексора и с прямым входом элемента И, инверсный вход которого соединен со стробирующим входом ; шифратора и с выходом признака модификации кода микроопераций регистра микрокоманд, выход элемента И соединен с вторым входом элемента ИЛИ, выход дешифратора соединен с входом шифратора, выход которого соединен с информационным входом регистра кода модификации, вход синхронизации которого соединен с вторым выходом генератора тактовых импульсов , группа выходов регистра кода модификации соединена с первой группой входов сумматора по модулю два, вторая группа входов которого соединена с группой выходов модифицируемых разрядов кода микроопераций регистра микрокоманд, группа выходов сумматора по модулю два является второй группой управляющих выходов устройства. Сущность изобретения состоит в повышении экономичности устройства путем сокращения оборудования блока памяти микрокоманд за счет исключения одной из микрокоманд А 5+ или Ai I входящих во фрагменты, описываемые алгоритмической моделью (1), и последующей модификации операционной части оставленной микрокоманды A;,(A--+J) для получения микрокоманды с операционной частью, соответствующей значению проверяемого логического условия. I . Реализуемые в предлагаемом устройстве фрагменты типа (1) преобразуются к следующему виду: ...А.А,(х .)А.,. ..A-J..., (2) ,-) А,, если X. 0(1) где А.(х;) (, если (0) . В этом случае логическому условию х ставится в соответствие код модификации 1с(х- 1, для которого справедливо выражение 1t(x; ) е где S2.., - операционные части мик A.J сооткоманд А, , ветственно. Если й; 01101, а Л)з 01011, то при Xt 1(0) генерируется код модификации 00110, который при сложении по модулю два с кодом дает ° . Если во всех фрагментах типа 111 требуется модификация только второго и третьего разрядов, то для реализации выражения (З) используется двухразрядный код модификации. Тогда в операционных частях микрокоманд выделяются две группы разрядов - модифицируемых и немодифицируемых. Не модифицируемые разряды поступают не посредственно на выход устройства, а модифицируемые разряды перед выдачей складываются по модулю два с кодом модификации. Следовательно, замена фрагментов типа (1 ) фрагментами типа (2) позво ляет исключить хранение микрокоманд Aj. и значит повысить экономичност устройства. Введение дешифратора и обусловленных им связей позволяет по коду проверяемых логических условий и их значению сформировать соответствующий управляющий сигнал, который затем преобразуется в код модификации. Введение шифратора и регистра ко да модификации и обусловленных ими связей дает возможность формировать и хранить код модификации MX в соответствии с номером и значение логического условия х. . Введение сумматорапо модулю два и обусловленных им связей позволяет производить модификацию группы модифицируемых разрядов операционной части в соответствии с выражением (. ВведениеНОВЫХ связей для элемен та И позволяет блокировать модификацию адресной части,, записанной в микрокомандах А. во фрагментах, .опи i сываемых моделью (1)i Таким образом, предлагаемое изобретение отличается от известных: по решаемой задаче - сокращением объема оборудования блока памяти мик рокоманд на основе учета типовых фрагментов микропрограмм) по пути решения задачи - исключением из каждой пары микрокоманд, имеющих одинаковых последовательностей во фрагмен тах типа (II, одной микрокоманды и модификации операционной части остав шейся (хранимой ) микрокоманды в зависимости от номеров и значений проверяемых логических условий; по используемым техническим средствам введением дешифратора, шифратора, регистра кода модификации, суммато--ра по модулю два и новых связей. На фиг.1 представлена функциональная схема предлагаемого микропрограммного устройства управления; на фиг.2 - примеры исходной графсхемы алгоритма (ГСА) и преобразованной для реализации на предлагаемом микропрограммном устройстве управления. Микропрограммное устройство управления (фиг.1) содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микрокоманд с полями немодифицируемых 3 и модифицируемых 3.j разрядов операционной части, признака модификации кода микроопераций 3 и кода логических условий 3, регистр 4 кода модификации, коммутатор 5, мультиплексор б, дешифратор 7, шифратор 8, сумматор 9 по модулю два, триггер 10, генератор 11 тактовых импульсов, элемент И 12, элемент ИЛИ 13, входы кода команды 14, пуска 15 и логических условий 16, управляющие выходы 17. Кроме того, символами 18 и 19 s обозначены выходы адресных и операционных разрядов блока 1 памяти микрокоманд соответственно, символа20-, - первый и- второй выхо11 тактовых импульсов ды генератора соответственно, символами 21 и 22 выходы конца команды и конца работы регистра микрокоманд соответственно. На фиг.2 использованы следующие обозначения; х -логические 2 3 -микроопеусловия; у Уг . У и конечная верначальная и рации; шины ГСЛГ Рассмотрим функционирование предлагаемого микропрограммного устройства управления. В исходном состоянии все элементы памяти устройства (фиг.1) находятся в нулевом состоянии, за исключением единичного состояния разряда регистра 3 микрокоманд, соответствующего выходу 21 регистра 3. Последний разрешает передачу через коммутатор 5 кода команды с входа 14 устройства для его последуквдей записи в регистр 2 адреса. По сигналу Пуск с входа 15 устройства триггер 10 устанавливается в единичное состояние и включает генератор 11. По первому тактовому импульсу с выхода 20 генератора 11 в регистр 2 адреса с входа 14 через коммутатор 5 записывается код реализуемой команды, который определяет адрес первой микрокоманды, соответствующей ,микропрограммы. С выхода 18 блока 1 памяти микрокоманд считывается адрес следующей микрокоманды, а с выхода 19 - сигналы микроопераций, сигнал признака модификации кода микроопераций и код проверяемого логического условия.

По второму тактовому импульсу с выхода 20 генератора 11 код микрокоманды записывается в регистр 3 микрокоманд и выдается с выходов регистра 3 микрокоманд на управляющие выходы 17 устройства, а также на входы мультиплексора 6, дешифратора 7, шифратора 8, элемента И 12, сумматора 9 по модулю два, коммутатора 5 и триггера 10 соответственно.

Так как в регистре 4 кодов модификации записан нулевой код, то сигналы микроопераций с второго выхода регистра 3 микрокоманд через сумматор 9 по модули два без изменения (модификации ) поступят на управляющие выходы 17 устройства.

Сигнал на выходе 21 регистра 3 микрокоманд во всех микрокомандах выполняемой микропрограммы, кроме последней, равен нулю-, а единичный сигнал на выходе 22 регистра 3 появляется только в конце работы устройства.

Если считанная микрокоманда содержит нулевой код логических условий и нулевое значение сигнала метки, то на выходах мультиплексора 6 и элемента И 12 формируются нулевые сигналы, а следовательно, элемент ИЛИ 13 пропускает без изменения (модификации ) младший разряд адреса. В этом случае по следующему тактовому импульсу с выхода 20 генератора 11 в регистр 2 адреса запишется адрес очередной микрокоманды и цикл работы устройства повторится.

Кроме того, при нулевом значении сигнала признака модификации кода микроопераций в регистр 4 кода модификации запишется нулевой код.

Если считанная микрокоманда содержит не нулевой код логических условий и нулевое значение сигнала признака модификаций кода микроопераций, то на выходе мультиплексора 6 появляется значение проверяемого логического условия, которое через открытый элемент И 12 поступает на вход элемента ИЛИ 13 и модифицирует младший разряд адреса, причем в этом случае модифицируемый разряд адресного выхода 18 блока 1 памяти микрокоманд имеет нулевое значение. Модифицированный адрес очередной микрокоманды через коммутатор 5 поступает на входы регистра 2 адреса и записывается при поступлении очередного тактового импульса с выхода 20 генератора 11. Далее устройство работает аналогично.

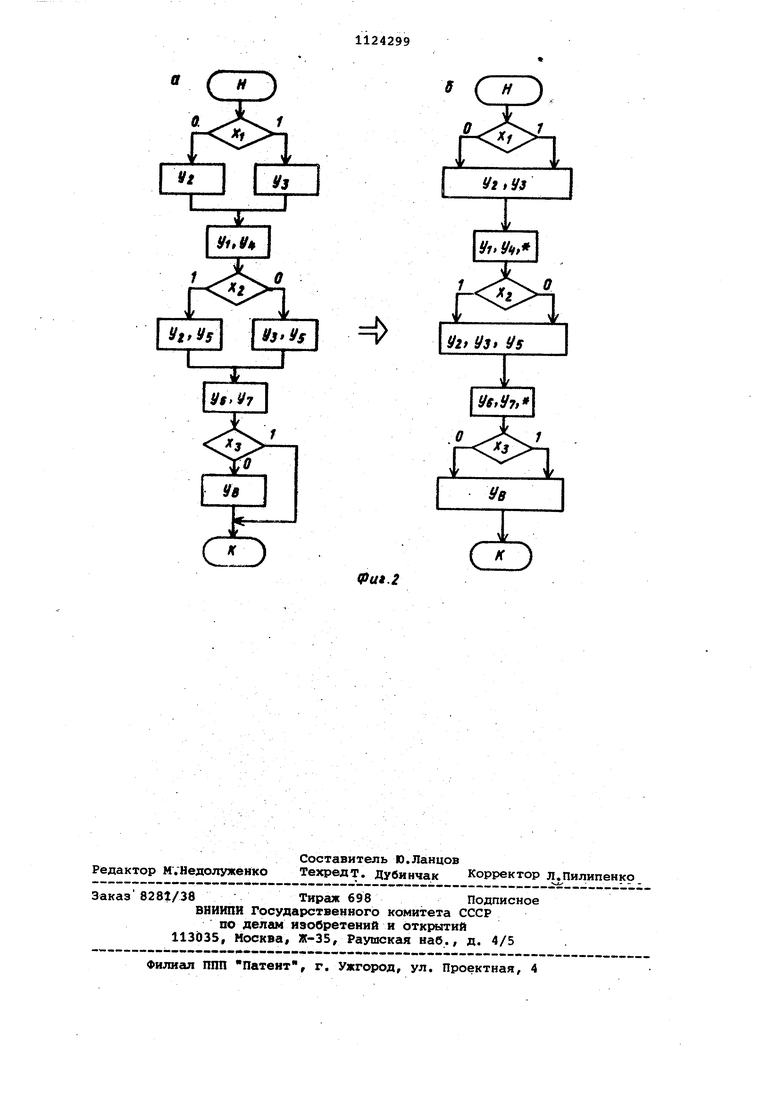

Специфическим режимом работы устройства является режим, когда очередная считанная микрокоманда содержит ненулевой код логических условий и единичное значение сигнала признака модификации кода микроопераций. Этот режим возникает, когда устройство переходит к реализации фрагментов ГСА, аналогичных представленным на фиг.2&. Граф-схема микропрограммы, изображенная на фиг.2а, содержит восемь микрокоманд. Ее отличительной особенностью является то, что имеются фрагменты, когда после проверки некоторого логического условия в зависимости от его значения выполняется одна из двух мик окоманд, после чего алгоритмы снова сходятся в одну точку. Например, после выдачи микрокоманды, содержа дей микрооперации у и у , проверяется логическое условие х и в зависимости от его значения выполняется микрокоманда, содержащая микрооперации у , Yj (при Xj 1) или микрокоманда, содержащая микрооперации У, г Уд Р 2 реализации на предлагаемом устройстве ГСА Сфиг.2с() преобразуется в ГСА, изображенную на фиг.2 Б. При выполнении этого преобразования в микрокоманду, содержащую микрооперации

УЧ добавляется метка, а после условной вершины х,, размещается вместо двух одна микрокоманда, содержащая микрооперации у, у, у , Эта микрокоманда будет считана .после проверки логического, условия

Xj независимо от его значения, а сигналы микроопераций у, у, будут модифицироваться ,в зависимости от значения Xj, . Аналогичным образом преобразованы подграфы ГСА, содержащие условные вершины х и Xj.

Рассмотрим работу предлагаемого устройства при реализации рассмотренных фрагментов ГСА, например фраг0 мента, содержащего условную вершину Xj (фиг.2). После считывания в регистр 3 микрокоманды, содержащей микрооперации у., , у , метку и код проверяемого логического условия х на выход 17 устройства поступят сигналы микроопераций у и у. На выходе мультиплексора б появится значение логического условия Xj. Выходной сигнал мультиплексора б на вход элемента ИЛИ 13 не поступит,так. как элемент И 12 закрыт сигналом при)знака модификации кода микроопераций с выхода регистра 3 микрокоманд.Это означает,что адрес следующей микрокоманды без модификации поступит на - входы регистра 2 адреса. Значение логического условия Xj с выхода мультиплексора б и код логического условия Х2 с выхода регистра 3 микрокоманд поступят на входы дешифрато0 ра 7. В результате на одном из его выходов появится единичный сигнал , в соответствии с которым шифратор 8 вьфаботает код модификации. Этот код поступит на входы регистра 4. ко5 да модификации, так как на управляю-1

щем входе шифратора 8 присутствует разрешающий сигнал.

Применительно к рассматриваемому фрагменту ГСА .(фиг. 2 б шифратором 8 будут сформированы следующие коды модификации:5

если Xj О, то в разряде кода модификации, соответствующем микрооперации у будет единица, а в остальных разрядах - нули/

если Х2 If то в разряде кода 10 модификации, соответствующем микрооперации yj , будет единица, а в остальных разрядах - нули.

По заднему фронту очередного тактового импульса с вьпсода 20, .генера- 5 тора 11 в регистр 2 адреса запишется адрес очередной микрокоманды, а по заднему фронту импульса с выхоа 202 генератора 11 эта микрокоманда запишется в регистр 3 микрокоманд.-дновременно по заднему фронту этого . е импульса в регистр 4 будет занесен код модификации. Немодифицируеые разряды микроопераций поступят непосредственно на выход 17 устрой- ства, а модифицируемые разряды - на ходы сумматора 9 по модулю два. С ыходов сумматора 9 по модулю два одифицированные разряды микроопеаций поступят на выходы 17 устройтва,30

При реализации рассматриваемого фрагмента ГСА (фиг.2 5).считанная микрокоманда будет содержать микрооперации у j у, и у , а на выходы 17 jj устройства поступят микрооперации у и у5 (при х, 1), либо микрооперации Уд и уу (при Xj 0). .

По очередному тактовому импульсу с выхода -202 генератора 11 в ре- ... гистр 2 адреса будет занесен адрес следующей микрокоманды, а по тактовому импульсу с выхода 20 генератора 11 эта микрокоманда будет записана в регистр 3 микрокоманд. Если предшествующая ей микрокоманда не 45 содержала единичный признак .модификации кода микроопераций, то на выходах дешифратора 8 будут нули и по заднему фронту импульса с выхода 20 генератора 11 в регистр 4 бу- 50 дет занесен нулевой код. Далее устройство функционирует аналогично, описанному.

Если в очередной микрокоманде будет записана единица в разряде, соответствующем выходу 21 регистра 3 микрокоманд, то очередной адрес в регистр 2 адреса будет записан с входа 14 устройства (т,е. начальный адрес следуквдей микропрограммы).

По окончании работы устройства в последней микрокоманде будет записана единица в разряде, соответствующем выходу 22 регистра 3 микрокоманд

|Эта микрооперация поступит на вход установки в ноль триггера 10, кото:рый возвратится в исходное состояние и остановит генератор 11,

Выигрыш в объеме оборудования, сокращаемого при использовании предлагаемого изобретения по отношению к прототипу оценивается выражением

(,,-Н

AW m

где N - число микрокоманд, хранимых в блоке памяти (в предлагаемом устройстве в формат вводится одноразрядная метка),

или

л«/ r--m - N,,r Е1.6; . Ф;еФ

Очевидно, 4ToaW70, если т

при N 200, m 32, г 10, 320-200 120,

Относительный выигрыш оценивается выражением

..ioo% -.,.,

mN

W

для рассмотренных значений параметров

266°35 100 18,75%.

Таким образом, предлагаемое устройство превосходит прототип и базовый объект по экономичности, Выигрьид в объеме оборудования растет по мере увеличения числа фрагментов типа (1),

Использование предлагаемого изобретения позволит повысить экономичность устройств, реализующих микропрограммы с рассмотренными типовыми фрагментами,,

Фиг.1

CZJ

Уг.Уз

Vi.yii,

У2 Уз. У5

Уб.Уъ

Ув

Фи.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Структура ЭВМ | |||

| Л., Машиностроение, 1975, с | |||

| Мяльно-трепальный станок | 1921 |

|

SU314A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1984-11-15—Публикация

1983-04-15—Подача