(S) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1278845A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммный процессор | 1977 |

|

SU717773A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

1

Изобретение относится к вычислительной технике и может быть, использовано при построении микропрограм;мных процессоров.

Известен микропрограммный процессор, содержащий блок управления, операционный блок, регистры адреса и микрокоманд, дешифратор ветвлений, элемент И и постоянную память ,

Однако данному устройству присуще низкое быстродействие из-за длительной реализации формирования адресов микрокоманд ветвлений.

Наиболее близким к предлагаемому по технической сущности и достигав- j мому эффекту является устройство, содержащее регистры адреса и микрокоманд, два элемента И, операционный блок, блок ветвления, постоянную, память и блок управления, первый вы- 20 ход которого подключен к первому входу первого элемента И, второй вход которого соединен с первым вы.ходом регистра микрокоманд, а выход - с первым входом регистра адреса , второй вход которого через второй элемент И подключен к первому выходу блока ветвлений, первый и второй выходы регистра адреса соединены соответственно с первым и вторым входами постоянной памяти, выход которой подключен к первому входу регистра микрокоманд, второй выход которого через операционный блок подключен ко второму входу блока ветвлений 2j

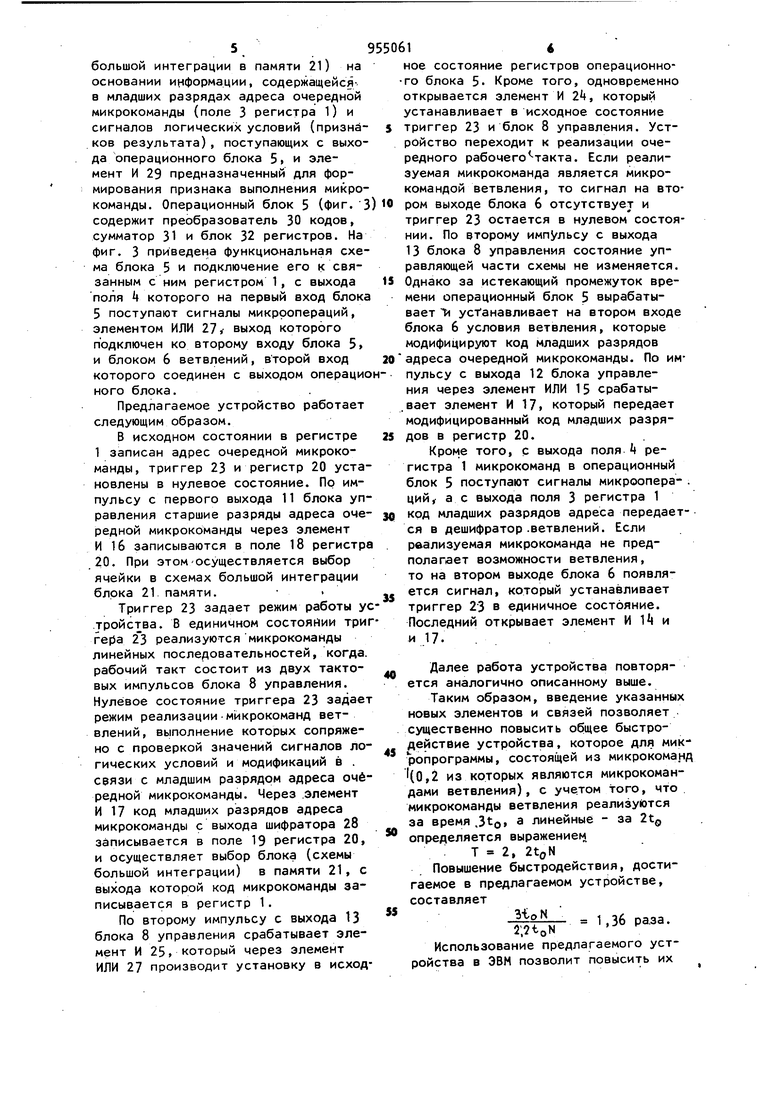

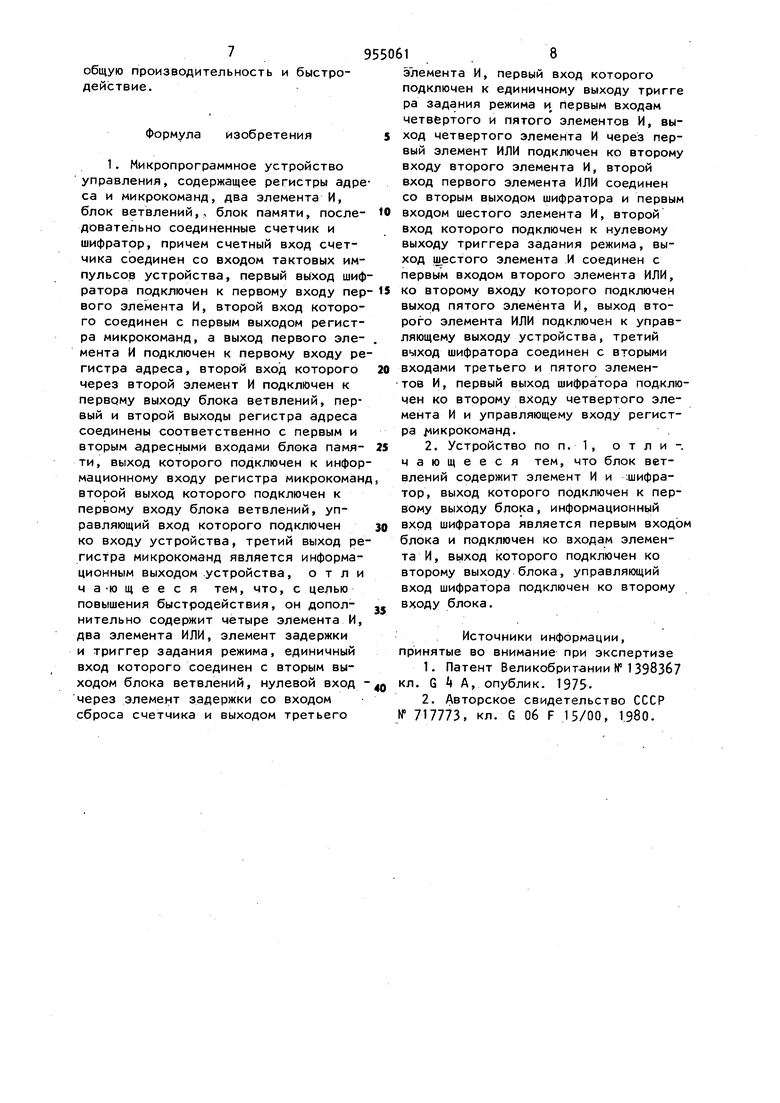

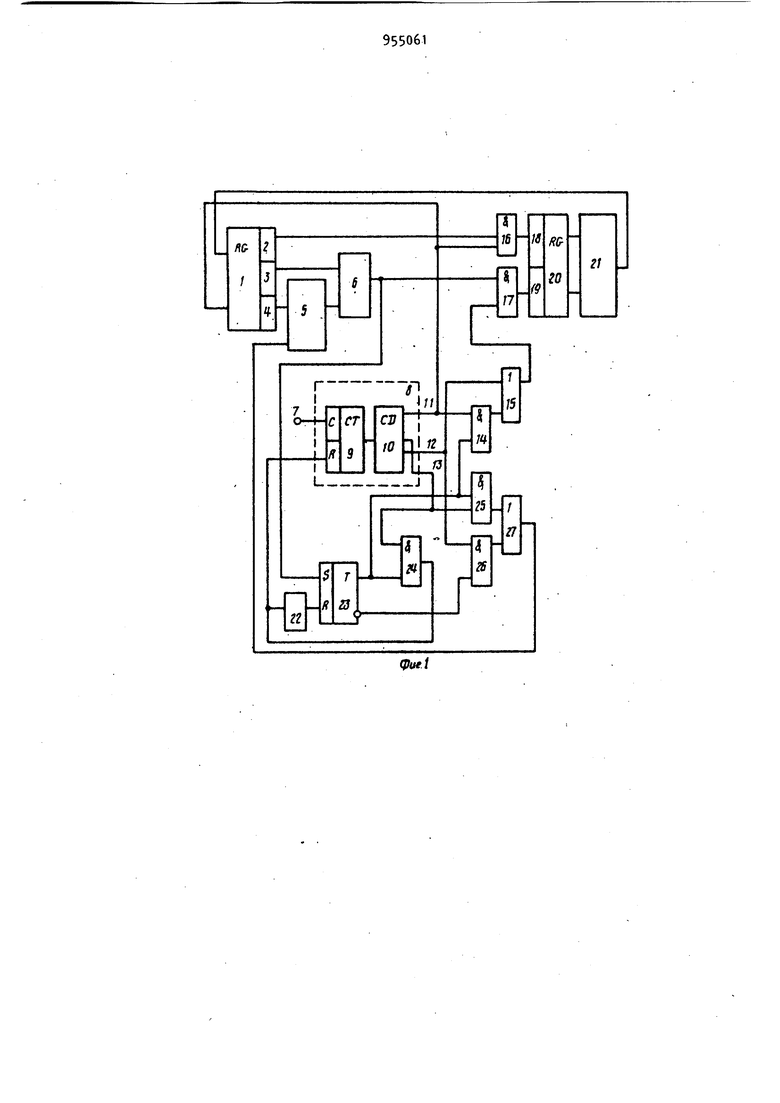

Недостатком указанного устройст- ва является низкое быстродействие обусловленное тем, что рабочий такт устройства (время между считыванием двух последовательных микрокоманд) одинаково как при реализации линейных последовательностей микрокоманд, так и микрокоманд ветвления, и подразделяется на три синхроимпульса, циклически выдаваемых блоком управления устройства. Однако реализация линейных микрокоманд может осуществляться в течение более короткого такта, поскольку в этом слунае не требуется проверка значений сигналов логических условий, поступающих с выхода операционного блока, а также формирование на их основе адреса очередной микрокоманды, как в случае реализации микрокоманд ветвления. Таким образом, отсутствие в данном устройстве элементов и средств управления рабочим тактом приводит к существенному снижению общего быстродействия устройства. Цель изобретения - повышение быстродействия микропрограммного устройства управления. Поставленная цель достигается тем, что микропрограммное устройство управления, содержащее регистры адреса и микрокоманд, два элемента И, блок ветвлений, блок памяти, последовательно соединенные счетчик и шифратор, причем счетный вход счетчика соединен со входом та товых импульсов устройства,.первый выход шифратора подключен к первому входу первого элемента И, второй вхо которого соединен с первым выходом регистра микрокоманд,,а &ыход первого элемента И подключен к первому входу регистра адреса, второй вход которого через второй элемент И подключен к первому выходу блока ветвле ний, первый и второй выходы регистра адреса соединены соответственно с пе вым и вторым адресными входами блока памяти, выход которого подключен к информационному входу регистра микро команд, второй вход которого подключен к первому входу блока ветвлений управляющий вход которого подключен к входу устройства, третий выход регистра микрокоманд является информационным выходом устройства, дополнительно содержит элемента И два элемента ИЛИ, элемент задержки и триггер задания режима, единичный вход которого соединен со вторым выходом блока ветвлений, нулевой вход через элемент задержки со входом сброса счетчика и выходом третьего элемента И, .первый вход которого под ключен к единичному выходу триггера задания режима и первым входом четвертого и пятого элемента И, выход четвертого элемента И через первый элемент ИЛИ подключен ко второму входу второго элемента И, второй вхо первого элемента ИЛИ соединен со вто рым выходом шифратора и первым входом шестого элемента И, второй вход которого подключен к нулевому выходу триггера задания режима, выход шестого элемента И соединен с первым входом второго элемента ИЛИ, ко второму входу которого подключен выход пятого элемента И, выход второго элемента ИЛИ подключен к управляющему выходу устройства, третий выход шифратора соединен со вторыми входами третьего и пятого элементов И, первый выход шифратора подключен ко второму входу четвертого элемента И и управляющему входу регистра микрокоманд. Блок ветвлений содержит элемент И и шифратор, выход которого подключен к первому выходу блока, информационный вход шифратора является первым входом блока и подключен ко входам элемента И, выход которого подключен ко второму выходу блока, управляющий вход шифратора подключен ко второму входу блока. Управление рабочим тактом ведут в. зависимости от типа микрокоманды: микрокоманды линейной последовательности реализуются за два (короткий рабочий такт), а микрокоманды ветвления - за три (длинный рабочи.й такт) тактовых импульса. Введение триггера задания режима позволяет задавать в каждом рабочем такте информацию о его длительности: короткий или длинный такт. На фиг. 1 приведена функциональная схема предлагаемого устройства управления; на фиг. 2 - функциональная схема блока ветвлений; на фиг.З функциональная схема операционного блока. Устройство содержит регистр 1 микрокоманд с полем 2 адреса, полем 3 ветвления и полем k операций, операционный блок 5 блок 6 ветвлений, вход 7 тактовых импульсов, блок 8 управления, содержащий счетчик 9, шифратор 10, первый 11, третий 12 и второй 13 выходы блока 8, элемент И 1, элемент ИЛИ 15 элементы И 16 и 17 вход 18 (старшие разряды) и вход 19 (младшие разряды) регистра 20 адреса, блок 21 памяти, элемент 22 заДержки, триггер 23, элементы И 24-2б и элемент ИЛИ 27. Блок 6 ветвлений (фиг. 2) содержит шифратор 28, предназначенный для выработки наполнительного адреса очередной микрокоманды (эдреса схемы большой интеграции в памяти 21) на основании информации, содержащейсяв младших разрядах адреса очередной микрокоманды (поле 3 регистра 1) и сигналов логических условий (признаков результата), поступающих с выхода операционного блока 5, и элемент И 29 предназначенный для формирования признака выполнения микрокоманды. Операционный блок 5 (фиг. З содержит преобразователь 30 кодов, сумматор 31 и блок 32 регистров. На фиг. 3 приведена функциональная схема блока 5 и подключение его к связанным с ним регистром 1, с выхода поля k которого на первый вход блока 5 поступают сигналы микроопераций, элементом ИЛИ 27, выход которого подключен ко второму входу блока 5 и блоком 6 ветвлений, второй вход которого соединен с выходом операцио ного блока. Предлагаемое устройство работает следующим образом. В исходном состоянии в регистре 1 записан адрес очередной микрокоманды, триггер 23 и регистр 20 установлены в нулевое состояние. По импульсу с первого выхода 11 блока управления старшие разряды адреса очередной микрокоманды через элемент И 16 записываются в поле 18 регистра 20. При этом-осуществляется выбор ячейки в схемах большой интеграции блока 21 памяти. Триггер 23 задает режим работы ус тройства. В единичном состоянии три гера 23 реализуются микрокоманды линейных последовательностей, когда, рабочий такт состоит из двух тактовых импульсов блока 8 управления. Нулевое состояние триггера 23 задает режим реализации-микрокоманд ветвлений , выполнение которых сопряжено с проверкой значений сигналов логических условий и модификаций в . сеязи с младшим разрядом адреса очередной микрокоманды. Через .Элемент И 17 код младших разрядов адреса микрокоманды с выхода шифратора 28 записывается в поле 19 регистра 20, и осуществляет выбор блока (схемы большой интеграции) в памяти 21, с выхода которой код микрокоманды записывается в регистр 1. По второму импульсу с выхода 13 блока 8 управления срабатывает элемент И 25, который через элемент ИЛИ 27 производит установку в исходное состояние регистров операционного блока 5. Кроме того, одновременно открывается элемент И , который устанавливает в исходное состояние триггер 23 и блок 8 управления. Устройство переходит к реализации очередного рабочего -такта. Если реализуемая микрокоманда является микрокомандой ветвления, то сигнал на втором выходе блока 6 отсутствует и триггер 23 остается в нулевом состоянии. По второму импульсу с выхода 13 блока 8 управления состояние управляющей части схемы не изменяется. Однако за истекающий промежуток времени операционный блок 5 вырабатывает устанавливает на втором входе блока 6 условия ветвления, которые модифицируют код младших разрядов адреса очередной микрокоманды. По импульсу с выхода 12 блока управления через элемент ИЛИ 15 срабатывает элемент И 17 который передает модифицированный код младших разрядов в регистр 20. Кроме того, с выхода поля регистра 1 микрокоманд в операционный блок 5 поступают сигналы микроопера-. ций ас выхода поля 3 регистра 1 код младших разрядов адреса передается в дешифратор .ветвлений. Если реализуемая микрокоманда не предполагает возможности ветвления, то на втором выходе блока 6 появляется сигнал, который устанавливает триггер 23 в единичное состояние. Последний открывает элемент И Т и и 17. Далее работа устройства повторяется аналогично описанному выше. Таким образом, введение указанных новых элементов и связей позволяет существенно повысить общее быстродействие устройства, которое для микропрограммы, состоящей из микрокоманд (0,2 из которых являются микрокомандами ветвления), с учетом того, что микрокоманды ветвления реализуются за время . линейные - за 2tg определяется выражением : Т 2, 2toN Повышение быстродействия, достигаемое в предлагаемом устройстве, составляет .36pa.3a. Использование предлагаемого устройства в ЭВМ позволит повысить их общую производительность и быстродействие. Формула изобретения 1. Микропрограммное устройство управления, содержащее регистры адре са и микрокоманд, два элемента И, блок ветвлений,, блок памяти, последовательно соединенные счетчик и шифратор, причем счетный вход счетчика соединен со входом тактовых импульсов устройства, первый выход шиф ратора подключен к первому входу пер вого элемента И, второй вход которого соединен с первым выходом регистра микрокоманд, а выход первого элемента И подключен к первому входу ре гистра адреса, второй вход которого через второй элемент И подключен к первому выходу блока ветвлений, первый и второй выходы регистра адреса соединены соответственно с первым и вторым адресными входами блока памяти, выход которого подключен к инфор мационному входу регистра микрокоман второй выход которого подключен к первому входу блока ветвлений, управляющий вход которого подключен ко входу устройства, третий выход ре гистра микрокоманд является информационным выходом .устройства, о т л и ч а-ю щ е е с я тем, что, с целью повышения быстродействия, он дополнительно содержит четыре элемента И, два элемента ИЛИ, элемент задержки и триггер задания режима, единичный вход которого соединен с вторым выходом блока ветвлений, нулевой вход через элемент задержки со входом сброса счетчика и выходом третьего 18 элемента И, первый вход которого подключен к единичному выходу тригге ра задания режима и Первым входам четвертого и пятого элементов И, выход четвертого элемента И через первый элемент ИЛИ подключен ко второму входу второго элемента И, второй вход первого элемента ИЛИ соединен со вторым выходом шифратора и первым входом шестого элемента И, второй вход которого подключен к нулевому выходу триггера задания режима, выход шестого элемента И соединен с первым входом второго элемента ИЛИ, ко второму входу которого подключен выход пятого элемента И, выход второго элемента ИЛИ подключен к управляющему выходу устройства, третий выход шифратора соединен с вторыми входами третьего и пятого элементов И, первый выход шифратора подключен ко второму входу четвертого элемента И и управляющему входу регистра /микрокоманд. 2. Устройство по п. 1, отличающееся тем, что блок ветвлений содержит элемент И и .шифратор, выход которого подключен к первому выходу блока, информационный вход шифратора является первым входом блока и подключен ко входам элемента И, выход которого подключен ко второму выходу блока, управляющий вход шифратора подключен ко второму входу блока. . Источники информации, принятые во внимание при экспертизе 1. Патент Великобритании № 1398367 кл. G k А, опублик. 19752. Авторское свидетельство СССР W 717773, кл. G Об F 15/00, 1.980.

Г

Л

II

физ.2

Г

SM 57

/(;

5П

Авторы

Даты

1982-08-30—Публикация

1981-01-26—Подача