Н0Я спедующей микрокоманды содержит первый, второй, третий, четвертый и пятый формирователи кода маски, первую, вторую, третью, четвертую, пятую и шестую группы элементов И, элемент И, элемент ИЛИ-НЕ, элемент задержки и дешифратор, причем первый вход блока соединен с первыми входами элементов И первой группы и через э юмент задержки - с первым входом элемента И и с первыми входами элементов И, второй, третьей, четвертой, пятой и шестой групп выходы элементов И первой группы образуют первую группу выходов блока, а выходы элементов И второй, третьей, четвертой, пятой и шестой групп образуют вторую группу выходов блока, первая группа входов блока соединена с входами

элемента ИЛИ-НЕ, с соответствующими, входами первого, второго, третьего, четвертого и пятого формирователей кода маски И с вторыми входами элементов И первой группы, выходы первого, второго, третьего, четвертого и пятого формирователей кода маски соединены с вторыми входами соответствующих элементов И соответственно второй, т-ретьей, четверо той, пятой и шестой групп, вторая группа входов блока соединена с входами дешифратора, выходы которого-соединены соответственно с третьими входами элементов И второй, третьей, четвертой, пятой и шестой групп и с вторым вх9Дом элемента И, выход элемента ИЛИ-НЕ является управляющим выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1130863A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

1.МИКРЬПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее регистр адреса, деши(|||}атор, бпок памяти, бпок формяроватш спедуюшей мнкрокомавФл, регистр мнкроксвкювооы, первый в второй эпемевты И, щячем ввформао овньш входы регЕстра соедввевы с пер; вой группой выходов регистра микрокоманды, едищчные входы регистра адреса соединены с первой гругоюй входов устройства, выходы регистра адреса соединены с входами дешиф{ атора, выход ш ВТОРОГО соединен с адресным ысодом 6no-i на памяти, выходы бпока тшмяти )йены с едишмными входами регистра - микрокома нпы, втбрая группа выходов которого соединена с первой группой вхр-; дов бпрка формирования спедующей ь осро-) команды пергвйя t ynfiB выходов которого является грушюй выходов мвкроопэг раций устройства, о т п и ч а го щ е в с я тем, что, с иепыр повыш|эшю досто- верности функционирования и расширес 1 фушшионапьных возможностей путем обеопечения формирования кодов микрсжомаШ Ъ различных режимах работы устройст&а. в него дополнительно введены- шиф{)атор, третий элемент И, кодовый щзеобрааова; тель, первый и второй впементы эадерж ки, счетчик, элемент И-НЕ, груша эпе; ментов И и элемент ИЛИ,а шдходы региотра адреса соединены с первыми входами элементов И группы, выходы KOTopoli соединены через кодовый преобразователь с ; инфо1 «апионными входами счетчика, вы; ходы счетчика через элемент И-НЕ соединены с 11в1шым входом первого элемен та И, выход которого является выходом сигнала отказа устройства, первый такто;вый вход устройства соединен с первым I входом второго элемента И, выход, кото;рсяго соединен с управляющим входом бло;ка памяти и через первый элемеегг эадер уЮЁк соединен с вторыми входами эпемен:т ж и группы и через второй элемент задержки соединен с входсв4 синхронизации адреса, первый выход блока фор Гмирования следующей шкрокоманды соедиюн с вторыми входами 1юрвого и втоi рого эп 1$ентов Н, вторая грушга выходов бпо фо1%а1рования следующей микрокоманды соединена с вокодами шиф1заCO гора, выход кок)рого соединен с нулевымЬ входами регистра мшфокоманды, (Вторая и третья группы выходов которо |iii iro соедине а 1 соответственно с входами со я®мевта ИЛИ и с второй группой входов .бйова формщювавия следующей микроюмашеы, второй тактовый вход устройства соединен спервым входом третьего эпемента И, выход которого соединен с входсы блока формирования микрокоманды и счет|&1м входе, счетчн ка, второй вход третьего элемента И соединен с выходом эпемента ИЛИ. Ж. yjcTfoucTBo по а. 1, о т li и ч а ;Ю щ е е с я . тем, что блок формирова

Изобретение относится к цифровой вычислительной технике и может быть иопользовано при разработке устройств управления ЭВМ и вычислительных систем с микропрограммным управлением.

Известно устройство управления, сочдержащее счетчик команд, регистр, адре са дешифраторы адреса, блокпамяти и приемнь1й регистр i }Недостатком устройства является низ- кая экономичность за счет задания ном&ров изменяемых разрядов не в позиционнном, а в десятичном коде.

Известно также устройство управления содержащее счетчик команд, регистр адреса, дешифраторы адреса, блок памяти -к приемный регистр 2.

Недостатками данного устройства явл .ются низкие функциональные возможности И низкая достоверность функционирования.

Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство управления, содержащее регистр адреса, дешифратор, блок памяти, блок формирования ел следующей микрокоманды,регистр микрокоманды, первый и второй элементы И, причем 1) -входы регистра адреса соединены с первой группой выходов регист ра микрокоманды, S-входы соединены с первой группой входов устройства, а выход соединен с входом дешифратора,

выход которого соединен с адресным входом блока памяти, выход которого соединен с : 5 -входами регистра микрокоманды, вторая группа выходов которого соединена с первой группой входов блока формирования следующей микрокоманды, первая группа выходов которогосоединена с выходами микроопераций устройства Сз}.

Недостатками известного устройства являются низкие функциональные возможности и достоверность функционирования, обусловленные большой избыточностью блока памяти за счет ограниченных возможностей кодирования микрокоманд (коды микрокоманд должны быть соседними и в серии отличаться разрядами только в порядке ихвЬз)эастания); низким быстродействием - число тактов опроса считанной базовой микрокоманды равно се разрядности (а не числу единиц в ней); асинхронным характером работы устройства; отсутствием контроля правильности функционирования устройства; ограниченными возможностями формирования одиночных микрокоманд.

Целью изобретения является повыше- . ние достоверности функционирования и , расширение функдиональкыч возможностей путем обеспечения формирования кодов микрокоманд в различных режимах работы устройства.

Поставпенная цепь достигается тем, то в -микропрограммное устройство jftiавпения, содержащее регистр адреса, ешифратор, бпок паксяти, бпок формировав ння следующей микрокоманды, регистр s икрокоманды, первый и второй элементы , 1фичем информаииотоле входы регистра дреса соединены с первой группой регистра микрокоманды, единичные входы. регистра адреса соединены с пер- tO вой группой входов устройства, а выходы регистра адреса соединены с входами дешифратора, выход которого соединен с адресным входом блока памяти, выходы бл(жа памяти соединены с единичными is входами регистра микрокоманды, вторая группа выходов которого соединена с первой группой входов бпока формирования следующей микрокоманды, первая группа выходов которого является группой .вы- 20 ходов микроопераций устройства, дополнительно введены шифратор, третий элемент И, кодовый преобразователь, первый и второй элементы задержки, счетчик, эпемент И-НЕ, группа элементов И, элемент 25 ИЛИ, причем выходы регистра адреса соединены с первыми входами элементов И группы выходы которой соединены через кодовый преобразователь с информационными входами счетчика, выходы счетчкжа jg через элемент И-НЕ соединены с первым входом первого элемента И, выход которого является выходом сигнала отказа устройства, первый тактовый вход устройства соединен с первым входом вторе го элемента И, выход которого соединен с управляющим входом блока памяти и через первый элемент задержки соединен с . вторыми входами элементов И группы, и через второй элемент задержки соединен с входом синхронизации регистра адреса, первый выход блока формирования следующей микрокоманды соединен с вторыми входами первого, и элементов И, вторая группа выходов блока формирования следующей микрокоманды соединена 5 с входами шифратора, выход которого соединен с нулевыми входами регистра мик- рокоманды, вторая и третья группы вы- , ходов которого соединены соответст вен1К . с входами элемента ИЩ и с второй гру пой входов блока формирования следую щей микрокоманды, второй тактовый ВХОЕ устройства соединен с первым входом третьего элемента И, выхрд которого соединен с тактовым входом блока формвро- 55 вания микрокоманды и счетиым входом счетчика, второй вход третьего эпеменга И соединен с выходом элемента ИЛИ.

Кроме того, блок формирования следующей микрокоманды, содержит первый, второй, третий, четвертый и пятый форм рователи кода маски, первую вторую, третью, четвертую пятую и шестую группы элементов И, элемент И, элемент . ИЛИ-НЕ, элемент задержки и дешифратор, причем первый вход блока соединен с первыми входами элементов И первой группы и через элемент задержки - с первым входом элемента И и с первыми входами элементов И второй, третьей, четвертой, пятой и шестой групи, выходы элементов И первой группы образуют первую группу выходов блока, а выходы элементов И второй, третьей, четвертой, пятой и шестой групп образуют вторую группу выходов блока, первая группа входов блока соединена с входами элемента ИЛИ-НЕ, с соответствующими входами первого, второго, третьего,четвертого и пятого формирователей кода маски и с вторыми входами элементов И первой группы, управляющие выходы первого, второго, третьего, четвертого и . пятого формирователей кода маски соединены с вторыми входами соответствую щих элементов И соответственно второй, третьей,четвертой,пятой и шестой групп, вторая группа входов блока соединена с входами дешифратора выходы которого соедигвены соответственно с третьими входами элементов И второй,третьей,четвертой,пятой и шестой групп и с вторым входом эле ента- И,выход элемента ИЛИ-НЕ является управляющим выходом блоки.

Сущность изобретения состоит в ш

вышении достоверности функционирования и - расширении функциональных возмож ;- ностей устройства управления за счет

: применения различных дисциплин формиро; вания кодов микрокоманд и организа1(иг контроля правильности функционирования. В предлагаемом устройстве приме1ш-

ются различные дисциплины формирования серий ми&рокоманд из базовс микроко; манды путем одновременной замены единиц как в одном, так и в двух разрядах.

При этом применяются два варианта формироваЕИя серии микрокоманд из базо; вой микрокоманды 101OJ.11O1, приведенные дпяэтой микр6комаш1ывтабл. 1 и 2. JT а б л И ц а 1

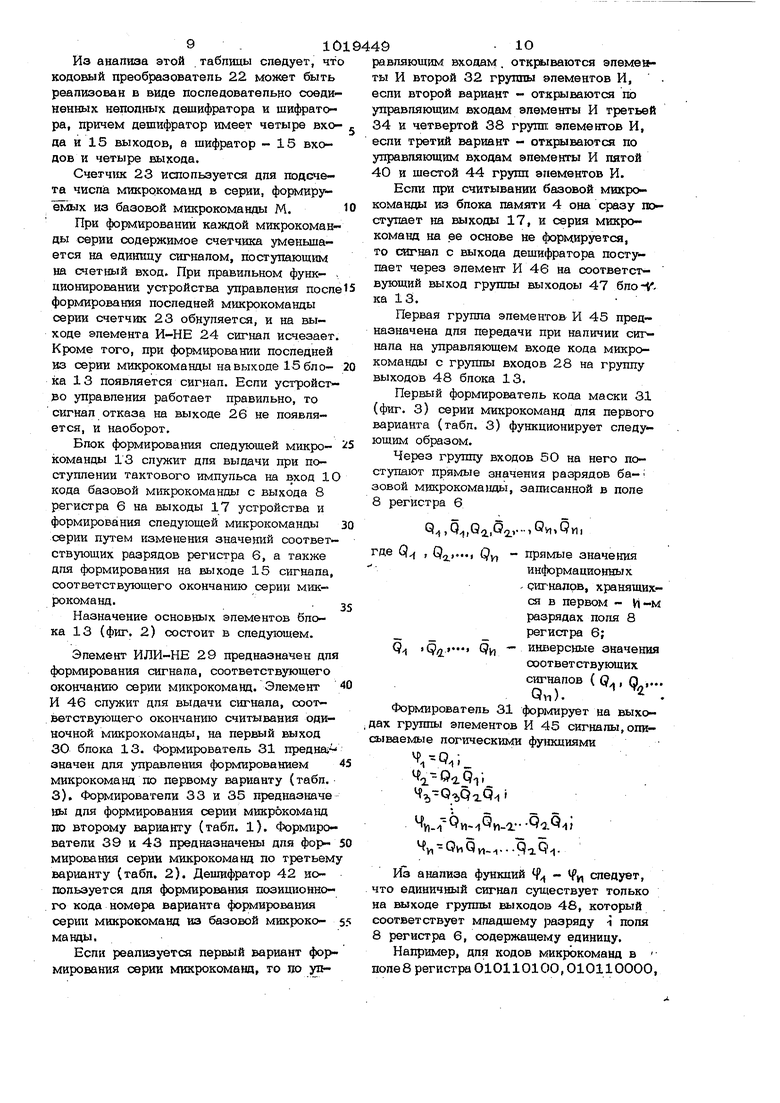

Табпица 2 Таким образом, чиспо; микрокоманд, формируемь1х из базовой микрокоманды, увепичивается. Это позволяет формировать большее чиспо микрокоманд либо при тех же фун ционапьных возможностях уменьшить чиопо базовых микрокоманд. Формирование серии микрокоманд иа базовой микрокоманды в известном устройстве осуществляется следующим образом. Поочередно, начиная с младшего разряда, Опрашиваются разряды базовой микрокоманды. Если в опрашиваемом разряде записан нуль, то микрокома1вда устройством не выдается, и наоборот. В очередном такте опрашивается следующий (старший) разряд базовой микрокоманды. После опроса всех разрядов базовой микрокоманды из блока памяти считывается очередная базовая микрокоманда, и устройство функционирует аналогично. Для приведенной базовой микрокомйнды тактов опроса будет десять, а сформированных микрокоманд - шесть. При опросе разрядов, содержащих нул микрокоманды на выход устройства не вы даются, и в этих тактах устройство простаивает. Так как чередование нулей и единиц в разрядах микрокоманды носит нерегулярный характер, то устройство формирует микрокоманды асинхронно, что требует дополнительных аппаратурных затрат для согласования его работы с ЦВМ Наличие пустых тактов (при опросе разрядов, содержащих нуль) снижает быстро действие устройства, т.е. устройство о&ладает существенной времетаой избыточностью. Эти недостатки устранятся, если в 1{аждом такте опрашивать толысо разряды базовой микрокоманды, содержащие единицу (табл. 3). При этом число тактов опроса базовой мгвсрОкоманды равно числ единиц в ней, и устройство фушшионир ет синхронно. Так как заранее известно сколько микрокоманд формируется при считывании из блока памяти базовой микрокоманды, то можно контролировать правильность функционирования устройства путем сравнения числа, импульсов опроса базовой микрокомавды с требуемым, и IB cny4iae их несравнения в конце формирования серии микрокоманд фиксировать отказ устройства. В реальньтх микропрограммах наряду с необходимостью формирования на основе считанной базовой микрокоманды серии микрокоманд требуется также одно-. кратное формирование базовых микрокомавд, т.е. последовательное формирование устройством толькр базовых микрокоманд. Однако такие трубования в известном устройстве не выполняются. Устройство может только однократно формировать микрокоманду, если в старшем разряде микрокоманды записана единица, а в остальныхнулв (т.е. двоичный код числа 2 , где - число разрядов базовой микроко -. манды). Указанное ограничение сужает область возможных приме тений устройства. На фиг. 1 представлена функциональная схема устройства; на }жг. 2 - функциональная схема блока формирования следующей микрокоманды; на фиг, 3 схема формирователя кода маски. Устройство микропрограммного уаравления (фиг. 1) содержит входы 1 кода операции, регистр 2 адреса, деши4 атор 3, блок 4 памяти, шифратор 5, регистр 6 микрокоманды, содержащий 7, вторую 8 и третью 9 группы выходов, второй тактовый вход 1О, eneK мент ИЛИ 11, третий элемент И 12, блок 13 формирования следующей микрокоманды с перЬой группой выходов 14, первым выходом 15, второй группой выходов 16, выходы микроопераций устройства 17, первый тактовый вход 18, второй элемент И 19, пер)вый элемент

задержки 20, группу элементов И 21, кодовый преобразоватепь 22, счетчик 23 элемент И-НЁ 24, первый эпемент И 25, вЬ1ход 26 сигкапа отказа, второй элемент задермоки 27.

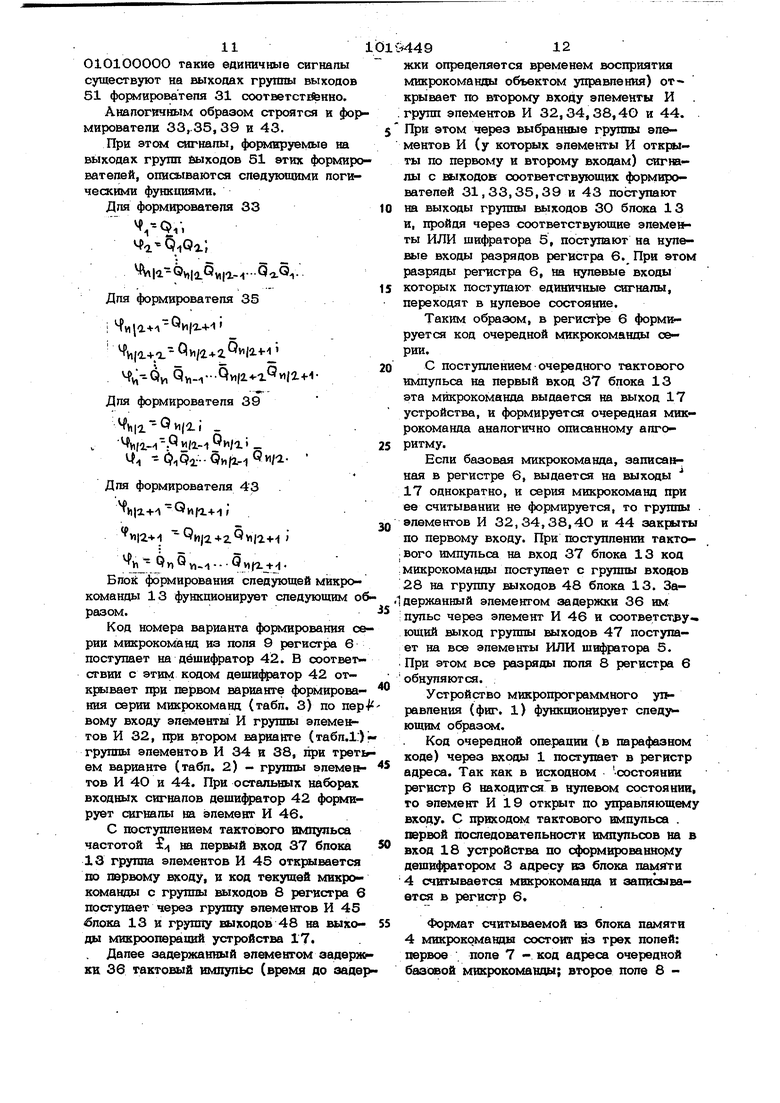

Блок формирования следующей микрокоманды 13 (фиг. 2) чсхэдержит первую грулпу входов 28, элемент ИЛИ-НЕ 29, выход 30 блока, первый формироватепь 31 кода масжи, вторую группу элементов И 32, второй формароватепь 33 кода маски, третью группу элементов И 34, третий формирователь 35 кода маски, элемент задержки 36, первый вход 37 блока, четвертую группу элементов И 38, четвертый формирователь 39 кода Маски, пятую группу элементов И 40, вт втогрую группу входов 41 блока, дешиф ратор 42, пятый формирователь 43 кода маски, шестую группу элементов И 44, первую группу элементов И 45, элемент И 46, вгорую группу выходов 47; первую группу выходов 48.

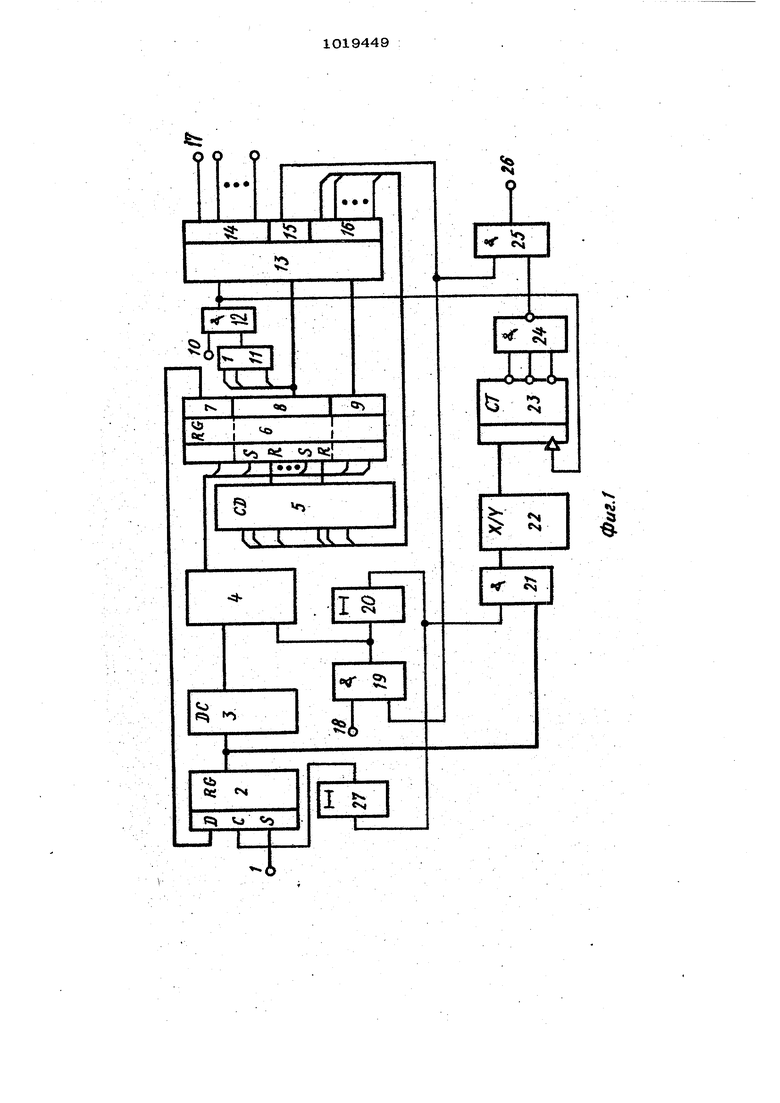

Первый формирователь код/а маски 31 (фиг. 3) содержит первый ()-й

элемеюгьГЙ 49, входы 50, выходы 51. Формирователи 33,35,39 и 43 построены аналогично.

Назначение основных элементов функциональной схемы устройства управления (фиг. 1) состоит в следующем.

Вхо№1 1 предназначены для подачи адреса микрокоманды на единичные входы регистра 2. Регистр 2 служит для хранения адреса считываемой базовой микрокоманды. Дешифратор 3 используется для формирования двоичного позиционного кода адреса базовой микрокоманды. Блок 4 памяти хранит коды базовых микрокоманд. Шифратор 5 служит для формирования сигналов обнуления соответствующих разрядов регистра 6 и шлдачи их на соответствующие нулевые входы. Регистр 6 используется для хранени базовых микрокоманд, считываемых с блока 4 памяти базовых микрокоманд, и выдачи их на блок 13. Элемент ИЛИ 11 позволяет получить сигнал окончания формирования серии микрокоманд и выдает его на элемент И 12. Элемент И 12

предназначен для управления выдачей вто:рой последовательности тактовых импуль сов на первый вход блока 13. Элемент И 19 служит для управления выдачей пе{хвой последовательности тактовых импульсов частотой f (i.,.) на управляющие входы блока 4 памяти и через эле. мент задержки 2О на группу элементов

И 21, и через /элемент задержки 27 на вход синхронизации регистра 2. Группа элементов И 21 используется для передачи кода адреса базовой микрокоманды с регистр 2 на кодошлй преобразователь 22.

Кодовый преобразователе 22 предназначен для формирования по коду адреса базовой микрокоманды, кода числа микрокоманд, формируемых из данной базовой микрокоманды в серии, и выдачи этой информации на информационный вход счетчвн ка 23..

Так как между кодом адреса -базовой микрокоманды и числом формируемых из нее микрокоманд существует взаимно однозначное соответствие, то кодовьтй преобразователь 22 можно реализовать в виде последовательно соединенных дешифратора и шифратора.

Пример построения кодового преобразователя 22 при следующих условиях: число базовых микрокслданд 15; таблица соответствия между адресами базовых микрокоманд и числом микрокоманд в серии X, реализуемой на основани) соогветствующей базовой микрокоманды М.

Таблица 4

Из анализа этой таблицы следует, что кодовый преобразоватепь 22 может быть реализован в виде поспедоватепьно соединенных неполных дешифратора и шифратора, причем дешифратор имеет четыре вхо

да и 15 выходов, а шифратор - 15 входов и четыре выхода.

Счетчик 23 используется дпя подсчета числ;а микрокоманд в серии, формируемых из базовой микрокоманды М.

При формировании каждой микрокоманды серии содержимое счетчика уменьшается на единицу сигналом, поступающим на счетный вход. При правильном функционировании устройства управления после формирования последней микрокоманды серии счетчик 23 обнуляется, и на выходе элемента И-НЕ 24 сигнал исчезает. Кроме того, при формировании последней из серии микрокоманды на выходе 15блока 13 появляется сигнал. Если устройство управления работает правильно, то сигнал отказа на выходе 26 не появляется, и наоборот.

Блок формирования следующей микрокоманды 13 служит для выдачи при поступлении тактового импульса на вход 10 кода базовой микрокоманды с выхода 8 регистра б на выходы 17 устройства и формирования следующей микрокоманды серии путем изменения значений соответствующих разрядов регистра 6, а также для формирования на выходе 15 сигнала, соответствующего окончанию серии микрокоманд..

Назначение основных элементов блока 13 (фиг. 2) состоит в следующем.

Элемент ИЛИ-НЕ 29 предназначен для формирования сигнала, соответствующего окончанию серии микрокоманд. Элемент И 46 служит для выдачи сигнала, соответствующего окончанию считывания одиночной микрокоманды, на первый выход 30 блока 13. Формирователь 31 предна;значен для управления формированием микрокоманд по первому варианту (табл. 3). Формирователи 33 и 35 предназначе ны для формирования серии микрокоманд по второму варианту (табп. 1). Формирователи 39 и 43 предназначены для формирования серии микрокоманд по третьем варианту (табп, 2). Дешифратор 42 используется для формирования позиционного кода номера варианта формирования серии микрокоманд из базовой микрокоманды.

Если реализуется пер1й 1й вариант формирования серии микрокоманд, то по управляющим входам, открываются элементы И второй 32 группы элементов И, если второй вариант - открываются по управляющим входам элементы И третьей 34 и четвертой 38 грухш элементов И, если третий вариант - открываются по утфавдяющим входам элементы И пятой 40 и шестой 44 групп элементов И.

Если при считывании базовой микрокоманды из блока памяти 4 она сразу поступает на выходы 17, и серия микрокоманд на ее основе не формируется, то сигнал с выхода дешифратора поступает через элемент И 46 на соответствующий выход группы выходоы 47 бло-V. ка 13.

Первая группа элементов И 45 предназначена для передачи при наличии сигнала на управляющем входе кода микрокоманды с группы входов 28 на группу выходов 48 блока 13.

Первый формирователь кода маски 31 (фиг. 3) серии микрокоманд для первого варианта (табп. 3) функционирует следующим образом.

Через группу входов 50 на него поступают прямые значения разрядов ба- зоБой микрокоманды, записанной в поле 8 регистра 6

Q.Q.Qa-Qcz. где Q , Qj,..., Qy - прямые значения информационнь х

. сигналов, хранящихся в первом - И-м разрядах поля 8 регистра 6;

Q iQ/j, f. QH - иш ерсные значения соответствующих сигналов (Q о ..

Qn).

Формирователь 31 формирует на выхо;Дах группы элементов И 45 сигналы, описываемые логическими функциями

%-Q.i

, , QгQгQ

,MQM.r--Qc.

4v,--QHQM-...9aQ-i.

Из анализа функций f - tfy, сэтедует, что единичнь1й сигнал существует только на выходе группы выходо)з 48, который соответствует младшему )эазряду i поля 8 регистра 6, содержащему единицу.

Например, дпя кодов микрокоманд в попе 8 регистра 010110100,010110000 11 OIOIOOOOO такие единичные сигналы существуют на выходах группы выходов 51 форлироватепя 31 соответст нно. Аналогичным образом строятся и фор мирователи 33,.35, 39 и 43. При этом сигналы, формируемые на вь1ходах групп выходов 51 этих формиро ватепей, описываются спедуюпшми погическими функциями. Дпя формирователя 33 . с1Р1С г; 4V,,|iQv,,a-f QaQv Дпя формирователя 35 ; Чц|а+( (a.+j.Qvi/a+A - - J %--QV, Qv,-v vчl г v1/lи Дпя формирователя 39 Mhii-Q Hj-l ( . и/1-1 и/г1 л -QiQ2.--QH|a-i M/a. Для формирователя 43 .ц-1 V)|2+i Qhji-t-i vija-H h QУ1Q vi-t - - vi(i. 1--j. Блок формирования следующей микрокоманды 13 функционирует следующим о разом. Код номера варианта формирования се рии микроком:анд из поля 9 регистра 6 поступает на дешифратор 42. В соответствии с этим 42 открывает при первом варианте формирования серии микрокоманд (табл. 3) по пер вому входу элементш И группы элементов И 32, при втором варианте (табл.1.) группы элементов И 34 и 38, при трет ем варианте (табл. 2) - группы элеме тов И 4О и 44. При остальных наборах входных сигналов дешифратор 42 формирует сигналы на элемент И 46. С поступлением тактового импульса частотой | на первый вход 37 блока 13 группа элементов И 45 открывается по первому входу, и код текущей микрокоманды с группы выходов 8 регистра б поступает через группу элементов И 45 блока 13 и группу выходов 48 на выходы микроопераций устройства 17. Далее задержанный элементом задерж ки 36 тактовый импульс (время до заде жки определяется временем восприятия микрокоманды объектом управления) открывает по второму входу элементы И групп элементов И 32,34,38,40 и 44. При этом через выбранные группы элементов И (у которых элементы И открыты по первому и второму вхогщм) сигналы с выходов соответствующих формирователей 31,33,35,39 и 43 поступают на выходы группы выходов 30 блока 13 и, пройдя через соответствующие элементы ИЛИ шифратора 5, поступают на нулевые входы разрядов регистра 6. При этом разряды регистра 6, на нулевые входы которых поступают единичные сигналы, переходят в нулевое состояние. Таким образом, в регистре 6 форм№руется код очередной микрокоманды серии. С поступлением очередного тактового импульса на первый вход 37 блока 13 эта микрокоманда выдается на выход 17 устройства, и формируется очередная микрокоманда аналогично описанному алгоритму. Если базовая микрокоманда, записанная в регистре 6, выдается на выходы 17 однократно, и серия микрокоманд при ее считывании не формируется, то группы элементов И 32,34,38,40 и 44 закрыты по первому входу. При поступлении тактоВого импульса на вход 37 блока 13 код микрокоманды постухюет с группы входов 28 на группу выходов 48 блока 13. Задержанный элементом задержки 36 им пульс через элемент И 46 и соответствую ютий выход группы выходов 47 поступает на все элементы ИЛИ шифратора 5. При этом все разряды поля 8 регистра 6 обнуляются. Устройство микропрограммного уп равления (фиг. 1) функционирует следу ющим образец. Код очередной операции (в парафазном коде) через входы 1 поступает в регистр адреса. Так как в исходном -состоянии регистр 6 находитсяв нулевом состоянии, то элемент И 19 открыт по управляющему входу. С приходом тактового импульса . первой последовательности импульсов на в вход 18 устройства по сформированному дешифратором 3 адресу вз блока памяти 4 считывается микрокоманда и записывается в регистр 6. Формат считываемой на блока памяти 4 микрокоманды состоит из трех полей: первое поле 7 - код адреса очередной базовой микрокоманд); второе поле 8 код базовой микрокоманды; третье попе 9код номера варианта форлированСга серии микрокоманд. Этот же тактовый импртьс, задержан-V ный элементом 20 задержки на время, определяемое временем считывания базовой микрокоманш 1 из блока памяти 4 и за записи ее в регистр 6, поступает на утьравняющий вход группы элементов И 21. При этом в счетчик 23 записывается код числа микрокоманд в серии, импульс с выхода элемента задержки 20 поступает также на элеме гг задержки 27 и задерживается в нем на время, определяемое временем записи информации в счетчик , 23 с регистра 2 при открытой по управляющему входу группе элементов И 21. При этом в-регистр 23 записывается адрес очередной базовой микрокоманды с поля 7 регистра 6. Так как содержимое поля 8 регистра 6 после записи в него базовой микро команды отлично от нуля, то на выходе 15 блока 13 сигнал исчезает, а на выхо де элемента ИЛИ 11 появляется. При этом элемент И 12 открывается, и тактовые импульсы частотой Е с входа 10 поступают через элемент И 12 на блок 13 и на счетный выход счетчика 23. При этом первая микрокоманда серии поступает с регистра 6 через блок 13 на выходы 17 устройства, в регистре 6 формиру ется вторая микрокоманда серии, и содержимое счетчика 23 уменьшается-на единицу. С поступлением очередного такт вого импульса на вход 1О устройство вы дает на выходы 17 вторую микрокоманду серии и формирует в регистре 6 третью микрокоманду серии. Далее устройство управления функци вирует аналогично. После выдачи последней микрокоманды серии поле 8 регистра 6 и счетчик 23 обнуляются. При этом на выходе 15 блока 13 появляется сигнал, разрешающий считывание очередной базовой микрокоманды по описанному алгоритму. Если серия микрокоманд состоит из одной микрокоманды, то она обрабатывается аналогично описанному алгоритму при поступлении на вход 1О одного тактового импульса. Контроль правильности функциойирования устройства производится следующим образом. Если устройство функционирует правиль но, то после выдачи на выходы 17 последней микрокоманды из серии на выходе 15 появляется сигнал, и счетчик 23 обнуляется. При этом на выходе 26 сигнал ошибки отсутствует. Если устройство функционирует неправильно (число сформированных в серии микрокоманд отличается от требуемого), то моменты обнуления счетчика 23 и появления сигнала на выходе 15 блока 13 не совпадут, и на выходе 26 устройства появится сигнал ошибки. Таким образом, в щ:)едлагаемом устройстве опрос в каждом такте только раорядов базовой микрокоманды, содержащих единичные сигналы, позволяет повысить быстродействие устройства и обеспечить синхронный характер его работы. Кроме того, формирование с базовой микрокоманды серии микрокоманд по одному из трех вариантов повышает гибкость устройства, при этом обеспечивается возможность формирования одиночных микрокоманд. Контроль соответствия числа формирую емых в серии микрокоманд требуемому позволяет повысить дос говерность функционирования устройства.

w

0t/2.J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 1972 |

|

SU416695A1 | |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство управления цифровой вычислительной машины | 1975 |

|

SU598076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-05-23—Публикация

1982-02-17—Подача