мента ИЛИ, вход начальной установки устройства подключен к четвертому входу первого элемента ИЛИ и к входам установки в нулевое состояние регистров группы, выходы каждого {-го регистра группы соединены с вторыми входами коммутирующих элементов И 1 -и группы, входы задания порогов i-и группы подключены к входам i-го регистра группы, выход первого элемента И соединен с третьими входами коммутирующих элементов И всех групп, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения выбора экстремальных значений сравниваемых чисел эа пределами поля допусков, в него введены дополнительные группы элементов И, элементы ИЛИ, элементы задержки, причем выход первого элемента ИЛИ через четвертьм элемент задержки соединен с вторым входом четвертого элемента ИЛИ и входами установки в нулевое состояние сдвигающего регистра и регистра числа, выход которого соединен с информационными входами элементов И пятой и шестой групп, управляющие входы которых через пятый и шестой элементы задержки соединены с выходами первого и N-ro элементов И четвертой группы соответственно,, а их выходы - с информационными входами первого и N-ro регистра группы, входы установки в нулевое состояние которых соединены соответственно с выходами пятого и шестого элементов ИЛИ, первые входы которых соединены с шиной начальной установки устройства, а их вторые входы - с выходами соответственно первого и N -го элементов И четвертой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1981 |

|

SU978143A1 |

| Устройство для задания программы обучения | 1986 |

|

SU1310874A1 |

| Устройство для сравнения двоичных чисел | 1982 |

|

SU1037241A2 |

| Устройство для контроля | 1986 |

|

SU1390617A1 |

| Устройство для сравнения двоичных чисел | 1980 |

|

SU943706A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| Трехкаскадная коммутирующая система | 1984 |

|

SU1226481A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Многоканальный цифровой коррелометр | 1985 |

|

SU1262523A1 |

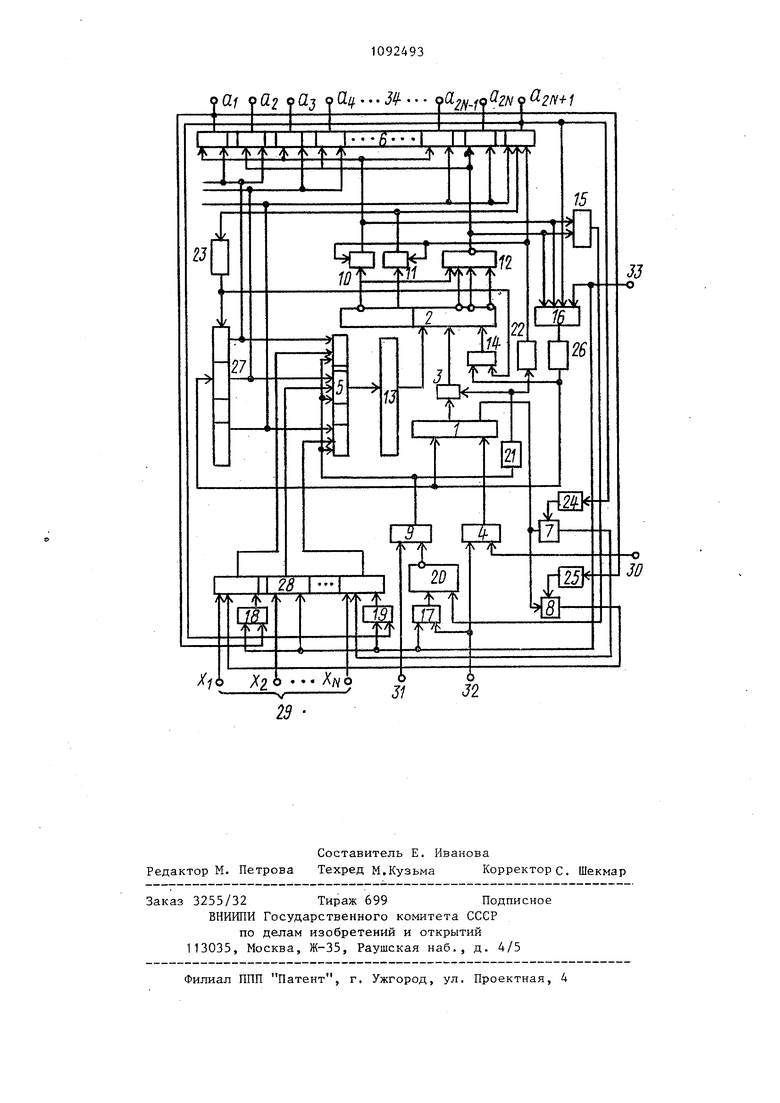

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ, содержащее регистр числа, сумматор, триггер, элементы задержки, элементы И, ИЛИ, ИЛИ-НЕ, группы элементов И, группу регистров задания допусков, кольцевой сдвигающий регистр, группу элементов ИЛИ и п групп коммутирующих элементов И, причем информационные входы устройства соединены с первыми входами элементов И первой группы, выходы которых подключены к информационным входам регистра числа, выходы которого соединены с первыми входами элементов И второй группы, выходы которых подключены к входам первой группы сумматора, инверсные выходы разрядов которого соединены с входами элемента ИЛИ-НЕ, выход которого подключен к первым входам элементов И третьей группы и первого элемента ИЛИ, вход разрешения записи устройства подключен . к вторым входам элементов И первой группы и первому входу второго элемента ИЛИ, выход которого соединен с входом установки в нулевое состояние триггера, инверсный выход которого подключен к первому входу первого элемента И, выход которого через первый элемент задержки соединен с вторыми входами элементов ,И второй группы и через второй элемент задержки с первыми входами второго, третьего и четвертого элементов И, вход тактовых импульсов устройства соединен с вторьм входом первого элемента И, инверсный и прямой выходы знакового разряда сумматора подключены к вторым входам второго и третьего элементов И соответственно , выход второго элемента И соединен с первыми входами элементов И четвертой группы, с вторым входо1 | первого элемента ИЛИ и первым входом третьего, элемента ИЛИ, выход которого подключен к входу установки в .единичное состояние триггера, выход третьего элемента И через третий элемент задержки соединен с первым входом четвертого элемента ИЛИ О и входом управления кольцевого сдви;о гающего регистра, каждый i-и выход N0 которого подключен к вторым входам i-x элементов И третьей и четвертой 4 групп, где i 1, 2, п и к первым со входам коммутрфующих элементов И {-и группы, выходы которых подключены к соответствующим входам элементов ИЛИ группы, выходы которых соединены с входами второй группы сумматора, выход четвертого элемента И подключен к третьему входу первого элемента ИЛИ, выход четвертого элемента ШШ подключен к входу установки в нулевое состояние сумматора, выход элемента ИЛИ-НЕ соединен с вторым входом третьего эле

1

Изобретение относите к автоматике и вычислительной технике, в частности к цифровым системам контроля.

Известно устройство для сравнения двоичных чисел, содержащее элементы И, ИЛИ, триггер, регистр, накапливающие сумматоры, элементы задержки, группы элементов И Cl}.

Недостатком этого устройства является низкая надежность за счет неоднозначного сравнения для отдельных значений сравниваемых чисел.

Наиболее близким к предлагаемому Является устройство для сравнения чисел, содержащее регистр, сумматор триггер, элементы задержки, элемент И, ИЛИ, ИЛИ-НЕ, группы элементов И, причем информационные входы устройства соединены с первыми входами элементов И первой группы, выходы которых подключены к информационным входам регистра, выходы которого содинены с первыми входами элементов И второй группы, которых подключены к входам первой rpyniai сумматора, инверсные выходы которого соединены с входами элемента ИЛИ-НЕ, выход которого подключен к

первым входам элементов И третьей группы и к первому входу первого элемента ИЛИ, выход которого соединен с входом установки в нулевое

состояние сумматора, первый вход управления устройства подключен к вторым входам элементов И первой группы и к первому входу второго элемента И, выход которого соединен с входом установки в нулевое состояние триггера, инверсный выход которого подключен к первому входу первого элемента И, выход которого через первый элемент задержки соединен с вторыми входами элементов И второй; группы и с входом второго элемента задержки, выход которого подключен к первым входам второго, третьего и четвертого элементов И, второй вход управления устройства соединен с вторым входом первого эл емента И, инверсный и прямой выходы знакового разряда сумматора подключены к вторым входам

второго и третьего элементов И соответственно, выход второго элемента И соединен с первыми входами элементов четвертой группы, с вторым входом первого элемента ИЛИ и с первым входом третьего элемента ИЛИ, йыход которого подключен к входу установк в единичное состояние триггера. Уст ройство содержит также группу регис ров, кольцевой сдвигающий регистр, группу элементов ИЛИ, и п групп коммутирующих элементов И, выход третьего элемента И через третий элемент задержки соединен с первым входом четвертого элемента ИЛИ и с входом управления кольцевого сдвигающего регистра, кадцый i-й выход которого подключен к вторым входам i-x элементов И третьей и четвертой групп, где 1 1, 2, ..., п , и с первыми входами коммутирующих элементов И i-й группы, выходы которы подключены к соответствующим входам элементов ИЛИ группы, выходы которых соединены с входами второй груп пы сумматора, выход четвертого элемента И подключен к третьему входу первого элемента ИЛИ, выход которого соединен с входом начальной установки кольцевого сдвигающего регистра и с вторым входом четвертого элемента ИЛИ, выход которого подключен к входу установки в нулевое состояние сумматора, выход элемента ИЛИ-НЕ соединен с вторым входом третьего элемента ИЛИ, вход начальной установки устройства подключен к четвертому входу первого элемента ИЛИ, к второму входу второго элемента ИЛИ и к входам установки в нулевое состояние регистров группы, выходы каждого i-го регистра группы соединены с входами второй группы входов коммутирующих элементов И i-й группы, входы задания порогов i-и группы подключены к входам i-ro регистра группы, выход первого элемента И соединен с треть ими входами коммутирующих элементов И всех групп С2. Недостатком этого устройства яв ляются его ограниченные функционал ные возможности. Цель изобретения - расширение функциональных возможностей устрой ства. Поставленная цель достигается тем, что в устройство для сравнени двоичных чисел, содержащее регистр числа, сумматор, триггер, элементы задержки, элементы И, ИЛИ, ИЛИгруппы элементов И, группу регистров задания допусков, кольцевой сдвигающий регистр, группу элементов ИЛИ и h групп коммутирующих элементов И, причем информационные входы устройства соединены с первы- ми входами элементов И первой группы, выходы которых подключены к информационным входам регистра числа, выходы которого соединены с первыми входами элементов И второй группы, выходы которых подключены к входам первой группы сумматора, инверсные выходы разрядов которого соединены с входами элемента ИЛИ-НЕ, выход которого подключен к первым входам элементов И третьей группы и первого элемента ИЛИ, вход разрешения записи устройства подключен к вторым входам элементов И первой группы и первому входу второго элемента ИЛИ, выход которого соединен с входом установки в нулевое состояние триггера, инверсный выход которого подключен к первому входу первого элемента И, выход которого через первый элемент задержки соединен с вторыми входами элементов И 1второй группы и через второй элемент радержки с первыми входами второго, третьего и четвертого элементов И, вход тактовых импульсов устройства соединен со вторым входом первого элемента И, инверсный и прямой выходы знакового разряда сумматора подключены к вторым входам второго и третьего элементов И соответственно, выход второго элемента И соединен с пepвы и входами элементов И четвертой группы, с вторым входом первого элемента ИЛИ и первым входом третьего элемента ШШ, выход которого подключен к входу установки в единичное состояние триггера, выход третьего элемента И через третий элемент задержки соединен с первым входом четвертого элемента ИЛИ и входом управления кольцевого сдвигающего регистра, каждый т-й выход которого подключен к вторым входам i-X элементов И третьей и четвертой групп, где i 1, 2, первым входам коммутирующих элементов И 1-й группы, выходы которых подключены к соответствующим входам элементов ИЛИ группы, выходы котоPbix соединены с входами второй группы сумматора, выход четвертого элемента Л подключен к третьему входу первого элемента ИЛИ, выход четверiToro элемента ИЛИ подключен к вход установки в нулевое состояние сумматора, выход элемента ИЛИ-НЕ соед нен с вторым входом третьего элеме та ИЛИ, вход начальной установки у ройства подключен к четвертому вхо ду первого элемента ИЛИ и к входам установки в нулевое состояние реги ров группы, выходы каждого i-го р гистра группы соединены с вторыми входами коммутирующих элементов И i-й группы, входы задания порогов i-Й группы подключены к входам i-r регистра группы, выход первого эле мента И соединен с третьими входами коммутирующих.элементов И всех групп, введены дополнительные груп пы элементов И, элементы ИЛИ, элементы задержки, причем выход первого элемента ИЛИ через четвертый элемент задержки соединен с вторым входом четвертого элемента ИЛИ и входами установки в нулевое состоя ние сдвигающего регистра и регистр числа, выход которого соединен с информационными входами элементов И пятой и шестой групп, управляющие входы которых через пятьй и шестой элементы задержки соединены с выходами первого и N-го элементов И четвертой группы соответстве но, а их выходы - с информационными входами первого и N -го регистра группы, входы установки в нулевое со.стояние которых соединены соответственно с выходами пятого и шестого элементов ИЛИ, первые входы которых соединены с шиной на чальной установки устройства, а их вторые входы - с выходами соответственно первого н N-ro элементов И четвертой группы. На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит регистр 1 параллельного действия, накапливаю щий сумматор 2, группы элементов И 3-8, элементы И 9, 10 и 11, элемент ИЛИ-НЕ 12, группу элементов ИЛИ 13, элементы ИЛИ 14-19, тригге 20, элементы 21-26 задержки, кольцевой регистр 27 сдвига, группу регистров 28, группу информационны шин 29, информацис ную шину 30, ши ны 31-33 управления, выходные шины 34. Устройство работает следующим образом. Б исходное состояние устройство приводится установочнь м импульсом, который, посгупая на шину 33 управления, очищает группу регистров 28, триггер 20, регистр 1, сумматор 2 и устанавливает кольцевой регистр 27 сдвига по цепи 33- 16-27в исходное состояние, при котором все разряды регистра находятся в состоянии О, кроме первого младшего разряда (на схеме верхний разряд), находящегося в состоянии Далее работа устройства происходит в следующей последовательности: запись значений допусков Х, X , . . . , Х, в группу регистров 28, причем Х , запись очередного сравниваемого числа X в регистр 1j сравнение числа X с допусками |Х-,, Х2 J jAM. запись значения (числа X в регистр 28, если X Х или . I Каждое число Л сравнивается с величинами X-j , Х , ...,Л|у за один цикл сравнения, который состоит из N тактов. Значения допусков Л-, , Х2 , .... поступают по информационной шине 29 и записываются в группу регистров 28. При подаче управляющего импульса на вход 32 разрешения очередное число X по цепи 30-4-1 записывается в регистр 1. Сравнение числа X с полем допусков К- , Y. , ..., Х|у 5 вьщача на вькоды 34 устройства о,:ного из сигналов: а., ( X Л) 1 2 С X Х ) 1 01. (Х,, X Х2 ) ; «4 2); °f2N lX-X,y) , ( X X|v, ) осуществляется за N тактов. В каждом цикле сравнения очередного числа X с полем допусков на шину 31 подается N тактовых импульсов (ТИ), ТИ1, ТИ25 ..., TMN, ТИ поступает по цепи 31-9 группы элементов И 5, при этом открывается первая подгруппа элементов И из этой группы, так как на эту подгруппу с триггера мттадшего разряда регистра 27 сдвига поступает высокий поте нциал. Значение первого допусках переписывается из первого регистра группы 28 по цепи 28 - первая подгруппа И 5 - 13-2 в сумматор 2. ТИ поступает также по цепи 31 9 - 21 - 3 на группу элементов И 3, элементы И 3 открываются и число X в обратном коде переписывается в су матор 2. В сумматоре в обратном коде образуется разность чисел ( В зависимости от соотношения величин Х,Х сумматор 2 может находить ся в одном из трех возможных состояний: отрицательный результат, когда Х-, Х ; отрицательный ноль, когда Д-, X, положительный результат, когда . Состояние сумматора анализируетс элементами И 10, 11 и Ш1И-НЕ 12. Если Л-, в этом случае в сумматоре 2 будет положительньш резуль тат, открывается элемент И 10 и ТИ поступает на нечетные (кроме 2,-г элементы И группы элементов И 6, од нако из этих элементов открывается лишь первый элемент группы, так как на этот элемент поступает разрешающий потенциал с триггера младшего разряда регистра 27 сдвига. В резул тате на выходе устройства будет пол чен сигнал С( ( X X., ) . Импульс с выхода ч поступает на левьй регистр группы регистров 28 по цепи СЛ - 18 - 28 и очищает его, а так же на группу элементов И 8 по цепи 01 -25-8, элемент И 8 открывается и значение числа X переписывается в левый регистр группы 26 по цепи 1 - 8 - 28. Теперь значение X становится нижним значением допуска для очередного числа X . Импульс с выхода элемента И 10 по цепи 10 - 15 - 20 поступит также на единичный вход триггера 20. Триггер устанавливается в состояни 1, при этом элемент И 9 закрывается и дальнейшее поступление ТИ в устройство прекращается до начала нового цикла сравнения. Кроме этого, с выхода элемента И 10 импульс по цепям 10-16-26-142- 10 - 16 - 26 - 1; 10 - 16 - 26 27 очищает сумматор 2, регистр 1 и устанавливает регистр 27 в исходно состояние. Если , то в сумматоре 2 будет отрицательный ноль, когда вс триггеры сумматора находятся в еди ничном состоянии. Такое состояние сумматора выявляется элементом ИПИ-НЕ 12, входы которого подключены к нулевым выходам триггеров сумматора. При наличии в сумматоре 2 отрицательного нуля на выходе элемента ИЛИ-НЕ 12 появляется сигнал, который подается на четные элементы И в группе 6. Однако при подаче ТИ1 открыт будет лишь второй элемент И в группе 6, что обеспечивается разрешающим потенциалом, поступающим с младшего разряда регистра 27 сдвига. В результате на выходе устройства появляется сигнал «2 (X Х). Кроме того, сигнал с выхода элемента ИЛИ-НЕ 12 по цепи 12-15-20 поступает на единичный вход триггера 20, который устанавливается в состояние 1, при этом элемент И 9 закрывается и дальнейшее поступление ТИ в устройство щ)екраш;ается до начала нового цикла сравнения. С выхода элемента ИЛИ-НЕ 12 импульс по цепям 12 - 16 - 26 - 14 - 2j 12 - 16 - 26 1; 12-16-26-27 очищает сумматор 2, регистр 1 и устанавливает регистр 27 в исходное состояние, Если X Х , то в сумматоре 2 будет отрицательный результат. При поступлении ТИ1 открывается элемент И 11, импульс с выхода И 11 сдвигает на один разряд единицу в кольцевом регистре 27 сдвига по цепи 11 23 - 27 и очищает сумматор 2 по цепи п - Z3 - 14 - 2. В результате этого устройство будет подготовлено ко второму такту. При подаче ТИ2 осуществляется сравнение числа X с Х2 При этом работа устройства аналогична работе при поступлении ТИ1, однако во втором такте в сдвигающем регистре 27 1 будет записана во втором триггере, поэтому при поступлении ТИ2 в сумматор 2 из группы регистров 28 будет выдано число Х, . На выходе устройства во втором такте могут быть выработаны сигналы 0 () или с ( X Xj) тшс как в группе элементов И 6 во втором такте открыты 3 и 4-й элементы И. Если X Х2 то во втором такте импульсы с выхода И 11 по цепям 11 - 23 - 27 и 11 - 23 - 14 - 2 подготавливают устройство к третьему такту, сдвигая 1 на один разряд в регистре 7 и очищая сумматор 2. Процесс сравнения числа X с допусками X , Х продолжается до N -го такта, если . В N-м такте вырабатьшается один из сигналов: 2N-1 ( V,) ; «2« ( t ) i «iN4r . - Если ,(| , В сумматоре 2 после подачи ТИ будет положительный резуль тат, в этом случае (2 -1)-й элемент И группы 6 будет открыт разрешакнцим потенциалом, подаваемым с N -го триггера регистра 27, и импульс с выхода И 10 по цепи 10-(2Н-1)-й элемент И группы 6 поступит на выход устройства. Сигнал выходе устройства появится в N -м такте, если (. Если , то в этом случае в N-м такте трехвходовый элемент И группы б будет открыт, так как на его трех входах будут сигналы поступающие с регистра 27, с выхода элемента И 11 (так как при в сз мматоре 2 будет отрицательный результат и элемент И 11 открыт) и с выхода элемента 22 задержки. На .выходе (2N + 1)-го элемента И группы 6 появится сигналс(| СХ XN ) . Импульс с выхода элемента И с(., посту пит на правый регистр 28 группы по цепи (ot2(s|4-t) - 19 - 28 и очистит его, а также на группу элементов И 7 По цепи ((.1) 24 - 7, элементы И 7 открываются и значение числа X переписывается в правьй регистр 28 группы. Теперь значение X становится верхним значением допуска для очередного числа X, Импульс с выхода элемента цепямо - 16 26 - 14 - 2;02N+ - 16 - 26 - 1-, 16-26-27 устанавливает сумматор 2, регистры 1 и 27 в исходное состояние к следующему циклу сравнения очередного числа X с величинами Х , X,., , X J , . .. , X f поля допусков и в этом случае Х-, наименьшее значение X и - наибольшее значение X из предыдущего цикла сравнения. Таким образом, предлагаемое устройство обеспечивает сравнение двоичных чисел с полем допусков Х , Х , X|v, и сохранение экстремальных значений чисел X , значение которых выходит за пределы заданных нижнего и верхнего допусков , . Изобретение позволяет расширить функциональные возможности и области применения устройства, так как предложенное техническое решение позволяет выполнить сравнение текущих значений двоичных чисел Л с полем допусков Хтакже выбрать экстремальные значения X при выходе их за пределы заданного поля, т.е. , X,Xfy .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сравнения двоичныхчиСЕл | 1979 |

|

SU830375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сравнения чисел | 1981 |

|

SU978143A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-15—Публикация

1982-12-10—Подача