ческого адреса, вторые управляющие входы которых соединены с выходами соответствующих блоков обнаружения ошибок, первые выходы регистров математического адреса канала соединены через счетчик адреса коммутируемого

канала с ыходами этих регистров, а вторые выходы - с вторыми входами соответствующих блоков сравнения, первые выходы которых подключены к входам соответствующих регистров физического адреса канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для преобразования временных интервалов в двоичный код | 1980 |

|

SU945980A1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 2001 |

|

RU2216760C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

| Система для решения задач математической физики | 1979 |

|

SU868768A1 |

РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ИНТЕГРАЛЬНЫХ УРАВНЕНИЙ, содержащее первый блок сравнения, -г первый вход которого соединен с первым выходом счетчика адреса значений ядра, второй вход - с выходом регистра порядка, а выход - с первым входом блока управления, второй блок сравнения, первый вход которого соединен с первым выходом счетчика адреса коммутируемого канала, второй вход - с выходом регистра порядка, а выход - с вторыт/ входом блока управления, коммутируемые каналы, каждый из которых содержит регистр физического адреса, блок памяти значений ядра, первый коммутатор, третий блок сравнения, сумматор, узел выделения приращений, счетчик значений функции и блок обнаружения ошибок, первый, второй и i-ретий входы которого соединены соответственно с выходом блока памяти значений ядра, с первыми входами сумматора и счетчика значений функции, а выход через элемент ИЛИ - с третьим входом блока управления, первый вход третьего блока сравнения соединен с вторым выходом счетчика адреса KONiMyTHpyeMoro канала, первый выход - с управляющими входами блока обнаружения ошибок, блока памяти значений ядра, сумматора и сч -т-чика значений функции, входная шина устройства подключена через буферный регистр к входам первых коммутаторов и непосредственно к входам установки счетчиков значений функции, входам сумматоров и к информационным входам блоков памяти значений ядра, адресные входы которых соединены со счетчиком адреса значений ядра, а информационные выходы через соответствующие первые коЯмутаторы - с первыми входами соответствующих сумматоров, выходы которых подключены соответственно к входам узлов выделения прираа1ений, (Л выходы которых подключены к входам соответствующих сумматоров, счетчиков значений функции и соответств лощим информационным входам второго коммутатора,управляющий вход которого подключен к вторым выходам блоков сравнения, а выход - к управляющим входам соответствующих ico сумматоров, а выходы счетчиков значений функции подключены к выходной N3 СП шине устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит буферный счетчик математического адреса канала, буферный регистр физического адреса, канала, общий регистр Лизического адреса канала, дешифратор, а в каждом канале по одному регистру математического адреса, первый выход регистров физического адреса канала соединен с установочными входами соответствующих регистров математического адреса канала, а второй выход - с входами реконфигурации общего регистра физического адреса канала, выход которого через дешифратор соединен с первыми управляющими входами регистров математи

. .1 Изобретение относится к вычисли тельной технике и может быть применено для построения высоконаде,жных устройств для интеграл ных уравнений. Известно устройство для решения интегральных уравнений, в котором используется для повышения надежнос ти резервирование размещением. Устройство содержит блок управления, рабочие и замещающие их резервные группы блоков, состоящие из блока памяти, связанного с сумматором, и блока обнаружения ошибок, входы которого соединены с блоком памяти и сумматором, блоки сдвиговых регистров, по одному блоку на каждую основную и замещающие ее резервны группы блоков, прич-ем вход каждого блока сдвиговых регистров соединен с выходами блоков обнаруже ния ошибок соответствующих рабочей и замещающих ее резервных групп бло ков, а выходы каждого блока сдвигов регистров связаны с управляютиими входами блока обнаружения .ошибок, блока памяти и блока сумматора соот ветст вующей рабочей и замещающих ее резервных групп блоков Недостатком такого устройства является то, что резервные группы блоков, замещающие одну из рабочих групп, не могут быть использованы для замещения других рабочих групп Закрепление резервных групп блоков за определенными рабочими группами требует большого количества резервных групп для обеспечения необходимой надежности. Известно также устройство для ре шения интегральных уравнений, в котором использовано скользящее резер вирование. Это устройство содержит группы блоков, состоящие из процесс ров и связанных с ними аварийных ка налов, каналы ввода-вывода и запоми нающие устройства, соединенные с каждым из процессоров, и блок прерываний. В устройстве в случае отказа одного из процессоров исправный процессор через аварийный канал снимает задачу с отказавшего пр цессора и сам приступает к ее выполнению 2 . Недостатком устройства является то, что задача в данный момент может выполняться только на одном процессоре и не может на нескольких. Это снижазт произзодительность устройства на отдельных задачах. Наиболее близкиг 1 к изобретению по технической сущности является устройство, которое содержит регистр порядка, счетчик адреса значений ядра, первый бло1с сравмения, один вход которого соединен со счетчиком адреса значений ядра, другой вход с регистром порядка, а выход подключен к блоку управления, счетчик адреса коммутируемого канала, второй блок сравн-ения, один вход которого соедишен со счетчиком адреса KOMf- iyтируемого канала, другой вход - с регистром порядка, а выход подключен к блоку управления, каналы, состоящие из регистра физического адреса, ,блока памяти значений ядра, ког.1мутатора, сумматора, узла выделения приращений, реверсивного счетчика, блока обнаружения ошибок, входы которого соединены с блоком памяти значений ядра, сумглатором и реверсивным счетчиком, а выход подключен через элемент ИЛИ к блоку управления, II блока сравнения, один вход которого связан со счетчиком адреса KOMiviyтируемого канала, а один выход подключен к управляющему входу блока обнаружения ошибок, блока памяти значений ядра, сумматора и реверсивного счетч1:ика, входную шину, подключенную через регистр к коммутаторам и непосредственно к реверсивным счетчикам, к блокам сумглатора к к информационным входам блоков памяти значений ядра, адресные входы которые соединены со счетчиком адреса значений ядра, а информационные выкоды связаны через соответствующие KO№viyтаторьт с одними входами соответствующих сумматоров, выходы которых подсоединены к входам узлов выделения приращений, выходы которых подключены через другой KOMi/iyTaTOp, связанный с другим выходом блоков сравнения, к управляющим входам соответствукхцих С5ЛОКОВ сумматора и непосредственно к другим входам соответствующих блоков сумматора и к реверсивным счетчикам, выходную шину, .связанную с выходами реверсивных счетчиков. Устройство обеспечивает выполнение задачи на нескольких каналах, при этом остальная часть всех каналов, имеющихся в устройстве, может не использоваться Сз1.

Однако в случае отказа одного из рабочих каналов наступает отказ всего устройства, так как в нем отсутствует аппаратура, обеспечивающа подключение неиспользуемых (неработающих) каналов вместо отказавших рабочих каналов.

Цель изобретения - повышение надежности и упрощение устройства за счет использования неработающих каналов в качестве скользящего резерва для рабочих каналов.

Поставленная цель достигается тем, что устройство для решения интегральных уравнений, содержащее первый блок сравнения, первый вход которого соединен с первым выходом счетчика адреса значений ядра, вторюй вход - с выходом регистра порядка, а выход - с первым входом блока управления, второй блок сравнения, первый вход которого соединен с первым выходом счетчика адреса коммутируемого канала, второй вход - с выходом регистра порядка, а выход с вторым входом блока управления, коммутируеглые каналы, каждый из которых содержит регистр физического адреса, блок памяти значений ядра, первый коммутатор, третий блок сравнения, сумматор, узел вьщеления приращений, счетчик значения функции и блок обнаружения ошибок, первый, второй и третий входы которого соединены соответственно с выходом блока памяти значений ядра, с перВЕЛМИ выходами сумматора и счетчика значений функции, а выход через элемент ИЛИ - с третьим входом блока управления, первый вход третьего блока сравнения соединен с вторым выходом счетчика адреса коммутируемого канала, первый выход - с управляющими входами блока обнаружения ошибок, блока памяти значений ядра, сумматора и счетчика значений функции, входная шина устройства подключена через буферный регистр к входа первых коммутаторов и непосредственно к входам установки счетчиков значений функции, входам сумматоров, и к информационным входам блоков памяти значений ядра, адресные входы которых соединены со счетчиком адреса значений ядра, а информационные выходы через соответствующие первые коммутаторы - с первыми входами соответствующих сумматоров, выходы

которых подключены соответственно к входам узлов выделения приращений, выходы которых подключены к входам соответствующих сумматоров, счетчиков значений функции и соответствуюошм информационным входам второго коммутатора, управляющий вход которого подключен к вторым выходам блоков сравнения, а выход - . к управляющим входам соответствующих сумматоров, а выходы счетчиков значений функции подключены к выходной шине устройства, содержит буферный счетчик математического адреса канала, общий регистр физического адреса канала, буферный регистр физического адреса канала, дешифратор, а в каждом канале по одному регистру математического адреса, первый выход регистров физического адреса канала соединен с установочными входами соответствующих регистров математического адреса канала, а второй выход - с входами реконфигурации общего регистра физического, адреса канала, выход которого через дешифратор соединен с первьлии управляющими входами регистров математического адреса, вторые управляющие входы которых соединены с выходами соответствующих блоков обнаружения ошибок, первые выходы регистров мате.матического адреса канала соединены через счетчик адреса коммутируемого канала с входами этих регистров,а вторые выходы - с вторыми входами соответствующих блоков сравнения,первые выходы которых подключены к входам соответствующих регистров физического адреса канала .

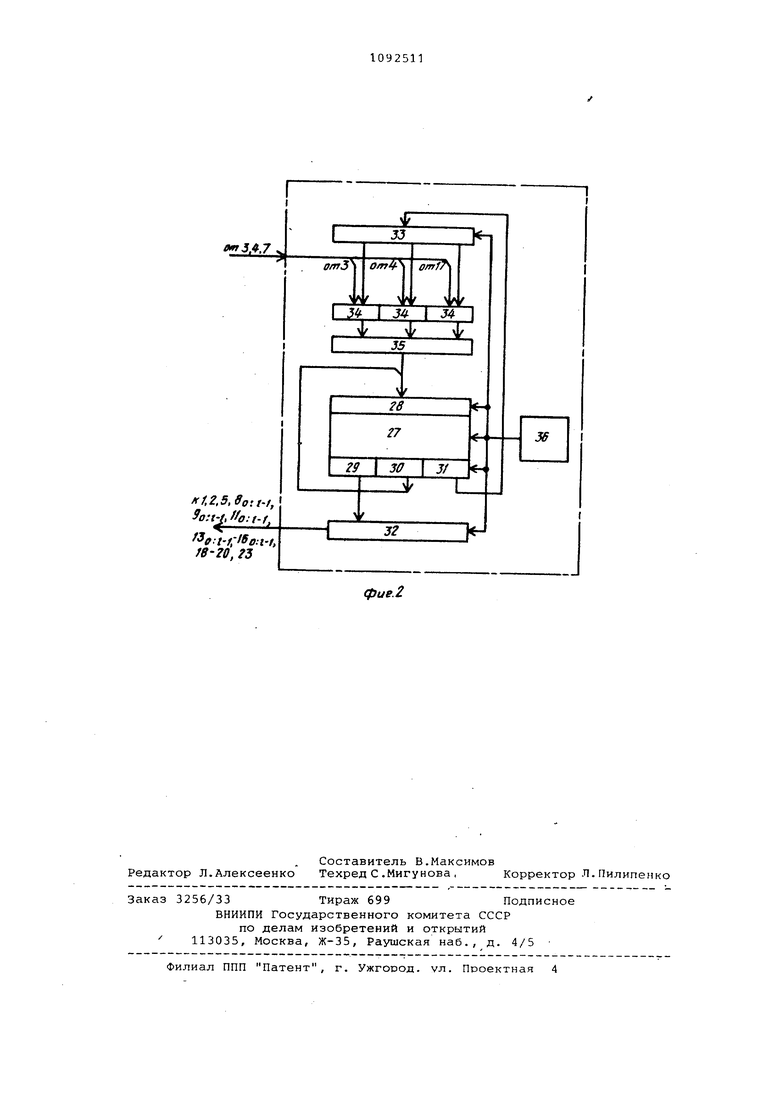

На фиг.1 представлена блок-схема предлагаемого устройства для решения интегральных уравнений; на фиг.2 - блок-схема блока управления.

Устройство (фиг.1) содержит счетчик 1 адреса значений ядра, счетчик 2 адреса коммутируемого канала, первый и второй блоки 3 и 4 сравнения, регистр 5 порядка, входную шину б, блок 7 управления, i групп О-С-1, каждая из которых состоит из третьего б.покл g. сравнения, регистра , математического адреса, регистра Юд-Юр,., физического адреса, блока llo-llp. памяти значений ядра, первого коммутатора 12p-12j,, сумматора ,., узла 14д-14р вьщеления приращений счетчика 15о-15., значения функции и блока 16jj-16р.обнаружения ошибок, первый элем.ент ИЛИ 17, буферный счетчик 18 математического адреса канала, общий регистр 19 физического сщреса канала, буферный регистр 20 физического адреса канала, дешифратор 21, первые выходы .блоков 8о-8р сравнения, буферный регистр 23, второй коммутатор 24, вторые выходы . блоков р. сравнения и выходную щину 26.

Блок 7 управления фиг,2,1 содержит узел 27 памяти микрокоманд с регистром 28 адреса микрокоманды и регистрами микроо.перации 29, адреса следующей микрокоманды 30 и кода вставления 31, дешифратор 32 микрооперации/ дешифратор 33 кода ветвления, элементы И 34, второй элемент ИЛИ 35 и блок 36 синхросигналов .

В устройстве (фиг. II первые выходы счетчиков 1 и 2 связаны с первыми входами блоков 3 и 4 сравнения соответственно, с вт «рыми входами которых соединен выход регистра 5 порядка, связанный с входной шиной 6. Выходы блокскв 3 и 4 сравнения соединены с первым входом блока 7 управления. Информационные выходы блоков ll(j-ll памяти ; сумматоров 1.3р-13, и счетчиков 15 д-15 подключены к соответствующим входам блоков 16(j--16.g-i обнаружения ошибок. Выходы блоков 16()-16 g непосредственно подключены к вторым управляющим входам соответствующих регистров через элемент ИЛИ 17 к третьему входу блока 7 управления Счетчик 2 связан с буферным счетчиком 18 математического адреса группы. Вход счетчика 2 соединен с первыми выходами регистров Эр-У,, а выход - с первыми входами регистров 9o-9g. и вторыми входами соответствующих блоков .сравнения, с первыми входами которых связаны первые выходы соответствующих регистров 9о-9 егистр 19 физического адреса канала связан с буферным регистром 20 физического адреса канала. Вход реконфигурации регистра 19 соединен с первыми выходами регистров lOjj-lOg-, а выход через дешифратор 21 - с вторыми управляющими входами регистров 9p-9f, с другими вхоцами которых связаны другие выходы соответствующих регистров lO j-lOg,. Управляющие входы блоков р связаны с выходом 22 соответствующих блоков .сравнения. Адресные входы блоков 11 -11 памяти подключены к выходу счетчика 1, а управляющие входы - к выходу 22 соответствующих блоков 8 o-8g -Информационные входы блоков lljj-llj. соединены с входной шиной 6, а информационные выходы - с входами коммутаторов 12д12 g.-( . Управляющие входы коммутаторов 12р-12„ связаны с регистром 23 подключенным к входной шине 6, а выходы коммутаторов 12g-12f соединены q входами сумматоров 13 |-13f , подключенных к входной шине 6 и одними управляющими входами к выходу

22 соответствующих блоков 8o-8j..Выходы сумматоров 13p-13g соединены с узлами р.-, выделения приращений. Выходы узлов 14(j-14g. подключены к другим входа.м сумматоров 13д-. 13.-( к реверсивным счетчикам 15о15,- и через коммутатор 24,связанный с выходами 25 блоков 8д-8.-( , к другим управляющим входам сумматоров 13р-13.Входы реверсивных счетчиков

15р-15 соединены с входной шиной 6, управляющие входы - с выходами 22 соответствующих блоков Вд-В. ц,а выходы - с выходной шиной 26. Блок 7 Iуправления подключен к счетчикам

5 J1, 2,15о-15 g. , 18, регистрам 5, 9g9g,, 10j,-10g, 20, 23, блокам 8 - . 8(ь-1, 13Q-13g, , 16o-16g.;, , устройствам llg-llg И узлам 14и-14, . В блоке 7 управления (фиг.21 вы0 ход регистра 29 связан через дешифра тор 32 микрооперации с выходом блока 7, а выход регистра 30 соединен с регистром 28. Выход регистра 31 подключен iepes дешифратор 33 кода

5 ветвления к одним входам элементов И 34, с другими входами которых связаны входы блока 7. выходы элементов И 34 через элемент ИЛИ 35 соединены с регистром 28. Узел 27 памя0 ти, регистры 28, 29, 30, 31 и дешифраторы 32 и 33 связаны с блоком 36 синхросигналов.

Принцип работы устройства состоит в следующем.

5 Для решения интегральных уравнений Фредгольма вида

1(х)+Д ls)-k(x,s)ds()Cl а

где у(х ) - искомая функция;

Д - численный параметр; с(ЬЗ- участок интегрирования с пределами айв;

K:(x,sl- известная функция, называемая

f(х)- известная функция; в устройстве реализуется итерационный алгоритм

г(01/

r(((x,-)fl; (i.ei

.(K,,.(x,, , у(Р(х.(х,)-...(Р(х,.);

e((x,)(x,H.(x.)

М.,,-)(.,„;

Р(7,1,.,со ,

где - координаты точек участка интегрирования а,в. h - порядок, число точек Х( участка интегрирования а,в, причем Ь, где - некоторое целое положительное ЧИСЛО; р - номер итерацииj f(Xj)- значение известной функ ции в точке ; ; (} - значение невязки в точ ке х на р-й итерации} IP1. , значение искомой функци Ч; в точке к на,р-й итераДУ (х-|- значение приргидения ис мой функции в точке х, на р-й итерации,п - разрядность представления кодов; функция определения зн ка,некоторое целое положительное число, определе нов из условия 2 ,,.5:Е(п) ; .п значение Функции-ядра в Ч.)точке x,-5j. р,,| Определение значенийд Е(Х-) на каждой итерации осуществляется соответствующим блоком в каждом рабочем канале, число которы равно Ь , остальные l-h каналов являются скользящим резервом и в вычи лительном процессе не участвуют. По мере возникновения отказов рабочих каналов, образующих, будем считать простейший поток отказов, резервные каналы становятся рабочими, а отказавшие каналы переводятся в нерабочее состояние и не принимают учас тия в вычислительном процессе. Когда откажут -1л рабочих каналов, весь резерв будет исчерпан и отказ нового рабочего канала приведет к останову в связи с исчерпанием резерва и отказом всего устройства. Работа устройства при решении ин тегрального уравнения начинается с режима Загрузка, далее оно переходит к режиму Обработка, и если ошибка не возникла, переходит в режим Выгрузка и останавливается. В случае появления ошибки в режиме Обработка устройство переходит в режим Реконфигурация, затем в режим Загрузка, потом Обработка , в котором анализируется появление ошибок и т.д. В режиме 3агрузка устройство за гружает с входной шины 6 значения порядка Ь , ядра К (;,9;) начальные значения невязки ) и начальные приближения искомой функции (х, включает Ь блоков 16 обнаружения ошибок, а также загружает число 2 В режиме Обработка устройство в соответствии с описанным выше алгоритмом выполняет некоторое чис(К;|И ло итераций, в каждой из которых оно определяет значения приращения искомой функции Jv (х;) значения искомой функции (х-| и невязки (X,-1 , а также контролирует с помощью Ъ блоков 16 появление отказов в п блоках 11, 13 и 15. В режиме Выгрузка устройство выгружает полученные Ь значений искомой функции(К(1на выходную шину 26. В режиме Реконфигурация устройство осуществляет подключение резервных каналов пу-тем смены математических адресов отказавшего рабочего -и резервного каналов таким образом, что отказавший рабочий канал получает максимальный математический адрес исправного резервного канала, а исправный резервный канал - математический адрес отказавшего рабочего канала, который он заменяет. Устройство работает следующим образом. Перед началом работы каналам присваиваются математические адреса (МА, равные их физическим адресам (ФА), т.е. канал с получает , канал с - , . . . , канал с - . Это осуществляется путем занесения по сигналу с блока 7 в регистры .математического адреса адресов из регистров Юр-Ю Физического адреса. А в счетчик 18 по сигналу из блока 7 заносится максимальный математический адрес исправной резервной страницы f-1, который также указывает на то, что число рабочих ti и резервных C-1i групп в сумгле равно € . В процессе работы устройства в режиме Загрузка с входной шины 6 в регистр 5 загружается значение порядка h (фактически загружается код , которое выбирается из условия является постоянньлм для данного устройства . Перед загрузкой значений ядра k(X(,j счетчики 1 и 2 сбрасываются в О, значения ядра k(xoi5j)3aписываются с входной шины 6 в блок 11 памяти с по адресу j , находящемуся в счетчике 1, причем после записи очередного значения содержимое счетчика 1 увеличивается на единицу. Запись значений ядра в этот блок 11 памяти производится до тех пор, пока содержимое j счетчика 1 не станет равным содержимому .h-l регистра 5. После этого счетчик 1 сбрасывается в О, а содержимое i счетчика 2 увеличивается на единицу и начинается запись значений ядpak x,SJ)в блок 11 памяти с . Запись значений ядра в следукхцие блоки 11 памяти с MA 2-(h-l) производится до тех пор, пока содержимое ) счетчика 2 и содержимое счетчика 1 не станут равны содержимому Ъ -1 регистра 5. Перед загрузкой начальных значений невязок (xj) счетчик 2 сбрасывается в О. Значение невязки I записывается с входной шины б и сумматора 13 с по адресу находящемуся в счетчике 2, причем после записи содержимое счетчика 2 увеличивается на единицу. Запись значений невязки в следующие блоки и с (Ъ-1 производится до тех пор, пока содержимое i счетчика 2 не станет равным содержимому регист ра 5. Перед загрузкой начальных прибли жений функции (xjl счетчик 2 сбрасывается в О. Значение прибли жения функции )записывается с входной шины 6 в счетчик 15 с по адресу i , находящемуся в счетчике 2, причем после записи содержимо t счетчика 2 увеличивается на единицу. Запись значений приближения функции в следующие счетчики 15 с производится до тех пор, пока содержимое счетчика 2 не станет равным содержимому h-l регистра 5. Для обнаружения ошибок в работе устройства 11, блоков 13 и счетчиков 15 с (h-l) блок 7 управления обеспечивает включение с помощью счетчика 2 первых h блоков 16 с MA 0-t1i-l). Таким образом, последние f-fi устройств 11, блоков 13 и счетчиЛов 15 с (-, входящих в соответ ствующие каналы с (-1), не загружаются и соответствующие им блоки 16 с (P-l) не включаются, оставаясь в резерве. Этот режим работы завершается загрузкой с входной шины б в регист 23 числа , которое постоянно выдаетсяна управляющие входы коммута ров 12. В режиме Обработка, к которому устройство переходит после загру ки, происходит следующее. Блок 7 управления отключает (бло кирует ) выходы 22 всех блоков сра нения 8o-8f., на которых появляется 1 независимо от содержимого счетчика 2 и регистров .-j, в то же время 1 на выходе 25 всех С блоков 8д-8р опр еделяется равенством содержимого счетчика 2 и регистров 9о-9м. По сигналу с блока 7 узлы 14 с (Р-1 выделяют приращения .(( (х,-), Эти приращения поступают на соответствующие счетчики 15 с (в-1) , в сумматоры 13 с .(S-1) и в коммутатор 24. Далее они на счетчиках 15 с ) суммируются со значением интегрируемой функцииз)1 |полученной на предыдущей итерации, а в блоках 13 с ( вычитаются из соответствующих значений невязок (х;).Затем из блоков 11 памяти с (Р-11 последовательно по адресам счетчика 1, адреса равны 0-(1т-1) , считываются зн чения ядра 1(х, Sj/ , сдвигаются на коммутаторах 12 и (-1)и поступают в сумматоры 13 с . Одновременно последовательно по тем же адресам счетчика 2, адреса равны О- (Ь-11, через коммутатор 24 в сумматоры 13 с (Р-1} поступают приращения dv {Sj ЬТаким образом, последние f-h приращений из узлов 14 через коммутатор 24 не проходят, что позволяет исключить их из вычисли льного процесса. В сумматорах 13 с МА 0-{f--1) происходит вычисление новых значений невязок ,) . Блоки неиспользуемых кг.налов с МА h-(f-1,работают вхЬлогтую, так как они никак не влияю- на ход вычислительного процесса. Итерация заканчивается, когда содержимое счетчика 1 станс- вится равным содержимому h -1 регистра 5. Выполнение итерации сопровождается контролем с помощью блоков 16 с (Ь-1| наличия ошибок, вызванных отказами типа Генератор О или Генератор 1 в блоках 11, 13 и 15 с MA 0-{h-ll . В качестве блоков 16 могут быть использованы элементы свертки по модулю 2. При возникновении сигнала Ошибка. в одном из блоков 16 с (ti-ll, одновременное. возникновение сигналов Ошибка 3 нескольких блоках 16 невозможно, так как предполагается,что поток отказов простейший, блок 7 переводит устройство в режим РеконЛигурация. В режиме Реконфигурация блок 7 управления включает (разблокирует/ выходы 22 всех I блоков 8 fl-8j., сравнения, 1 на которых при этом имеет место при равенстве содержиг/шх счетчика 2 и соответствующего регистра 90-9 р. . Затем блок 7 управления передает на счетчик 2 из счетчика 18 максимальный математический адрес исправной резервной страницы, который, кроме того, указывает на cyrvtMapHoe число рабочих и исправных резервных каналов и сравнивает этот адрес с порядком, находящимся в регистре 5, Если сщрес равен порядку, то происходит останов в связи с исчерпанием резерва и отказом Е:сего устройства. В противном случае производится смена математических адресов откгьзавшего и резервного каналов следующим образом. В счетчик 2 принимается, например, , выданный сигналом Ошибка блока 16 из соответствующего регистра 9. отказавшего канала, имеющего . По , на.х-одящемуся на счетчике 2, блок 7 CBOKIV: сигналом отключает блок 16 и сигнал Ошибка перестает вьщаваться. Дале по на счетчике 2 из регистра 10 в регистр 19 считывается соответствующий . Происходит обмен содержимым между счетчиками 18 и 2 и между регистрами 20 и 19 через со ответствующие связи. По , находящемуся на счетчике 2 в резуль тате обмена, из регистра Юр. в регистр 19 считывается соответствующий . Происходит обмен содержимым только между регистрами 20 и 19. По , находящемуся па регистре 19, с помощью дешифратора 21 на соответствующий регистр 9 из счетчика 2 записывается . Про исходит обмен содержимым между регистрами 19 и 20 и между счетчиками 2 и 18. По , находящемуся на регистре 19 в результате обмена с помощью дешифратора 21 на соответ ствующий регистр из счетчика 2 записывается . Таким образом, оказывается записанным в регистр 9 отказавпсго канала с в регистр 9. исправного резервного канала. Содержимое счетчика 18, равное С-1, уменьшается на единицу, в результате чего максимальный МА исправного резервного канала, который, кроме того, указывает на суммарное число рабочих и исправных резервных каналов, ста новится равным f-2. После режима Реконфигурация устройство переходит к режимам Загрузка и далее Обработка. При возникновении сигнала Ошибка в одном из блоков 16 О -{fl-1l блок 7 опять переводит устройство в режим Реконфигурация. При этом если резерв не исчерпан, максимальный МА исправного резервного канала, равный f-2, присваивается новому отказавшему каналу, в МА отказав шего канала присваивается этому исправному резервному каналу. Затем содержимое счетчика 18 уменьшается на единицу. В случае отсутствия ошибок во время выполнения требуемого числа итераций на счетчиках 15 находятся значения интегрируемой функции, и устройство переходит к режиму Быгрузка. Перед выгрузкой значений интегр руемой функции блок 7 управления включает (разблокирует / выходы 22 всех 2 блоков 8(,-8 «.сравнения, 1 на которых при этом имеет мест только при равенстве содержимого счетчика 2 и соответствующего регистра 90-9 p.-f. Затем счетчик 2 сбрасывается в О. Значение интегрируемой функции поступает на выходную шину 26 из счетчика 15с по v адресу 1, находящемуся в счетчике 2, причем после выдачи содержимое счетчика 2 увеличиваемся на единицу.. Выдача значений интегрируемой функции из следующих счетчиков 15 с (11-1/ :рои: йодится до тех пор, пока содержимое счетчика 2 не станет равным содержимому h-1 регистра 5, т.е. содержимое тоследних счетчиков 15 с (p-l) соответствую шх неиспользуемых каналов с (Р-11 на выходную шину 26 не выдается. Работа блока 7 управления (фиг. 21 происходит следую1чиг1 образом. В регистры 29, 30 и 31 из узла 27 памяти считывается очередная микрокоманда. Содержимое регистра 29 поступает в дешифратор 32, на выходе которого образуЕотся сигналы управления узлами устройства (сброс в О, увеличение на единицу содержимого счетчика, прием в регистр и т.д.). Содержимое регистра 30, представляющее собой старшие разряды адреса следующей микрокоманды, непосредственно поступает в регистр 28. Содержимое регистра 31 поступает через дешифратор 33 на элементы И 34, которые обеспечивают в соответствии с кодом ветвления и входными сигналами блока 7 формирование через элемент ИЛИ 35 младшего разряда адреса следующей микрокоманды. По вновь сформированному адресу считывается новая микрокоманда и т.д. Блок 7 управления ,выполняя микрокоманды микропрограмм, записанных в узле 27 памяти, реализует режимы работы предло хенно1о устройства. Технико-экойомический эффект изобретения состоит в том, что по сравнению с устройством-прототипом оно позволяет повысить надежность работы за счет наличия скользяо.его оезерва. Каналы устройства, являющиеся резер1вными резеовиоуют все рабочие каналы и заменяют их по мере возникновения отказов рабочих каналов. Кроме того, реализация скользящего резервирования в предложенном устройстве не связана с уменьшением производительности и не требует больших аппаратурных затрат по сравнению с известными устройствами.

фие.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент ачл № 3665418, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ограничитель крутящего момента | 1987 |

|

SU1434186A1 |

| С, 4 A,Q 06 К 11/00, опублик | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для решения интегральных уравнений | 1978 |

|

SU687452A1 |

| G, 06 J 1/02, 197S {прототип ) | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1984-05-15—Публикация

1981-09-11—Подача