(54) СИСТЕМА ДЛЯ РЕШЕНИЯ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Микропроцессор | 1977 |

|

SU943735A1 |

Изобретение относится к вычи.слительн.ой технике и может быть использовано при построении специализирован ных вычислительных средств для решени задач математической физики. Известна система для решения зада математической физики, содержащая устройство управления и матрицу реша ющих блоков l3 Недостатками этой системы являют ся низкие надежность и производител ность . Наиболее близкой к предлагаемой является система, содержащая устрой ство -управления, матрицу решающих блоков и матрицу узлов .диагностики 2 . Недостатком известной системы яв ляатся низкая надежность. Шель изобретения - повышение надежности системы. Поставленная цель достигается те что в систему для решения задач мат матической физики, содержащую устро ство управления, матрицу решающих блоков, соединенных между собой по строкам и столбцам информационными шинами, матрицу узлов диагностики, причем каждый узел диагностики соед нён двухсторонней связью с соответствующим решающим блоком, выход каждого узла диагностики соединен с первым входом устройства управления, первый и второй входы каждого узла диагностики соединены соответственно с первым и вторым выходами устройства управления., первый и второй входы каждого решающего блока соединены соответственно с третьим и четвертым выходами устройства -управления, второй вход которого соединен с выходом решающего блока, введены блок переадресации и на каждый решающий блок коммутатор блокировки строки и коммутатор блокировки столбца, причем каждый коммутатор блокировки строки под1 лю.чен к информационным шинам соответствующего решающего блока параллельно по строке, каждый коммутатор блокировки столбца подключен к информационным шинам соответствующего решающего блока параллельно по столбцу, вход каждого коммутатора блокировки строки соединен с соответствующим выходом первой группы блока переадрасации, вход каждого коммутатора блокировки столбца соединен с соотBeTCTBViomHM выходом второй группы блока переадресации, первый и второй выходы которого соединены соответстенно с третьим и четвертым входами аждого решающего блока, пятый и. естой выходы устройства управления оединены соответственно с первым и вторымвходами блока переадресации, третий выход которого соединен с третьим входом устройства управления.

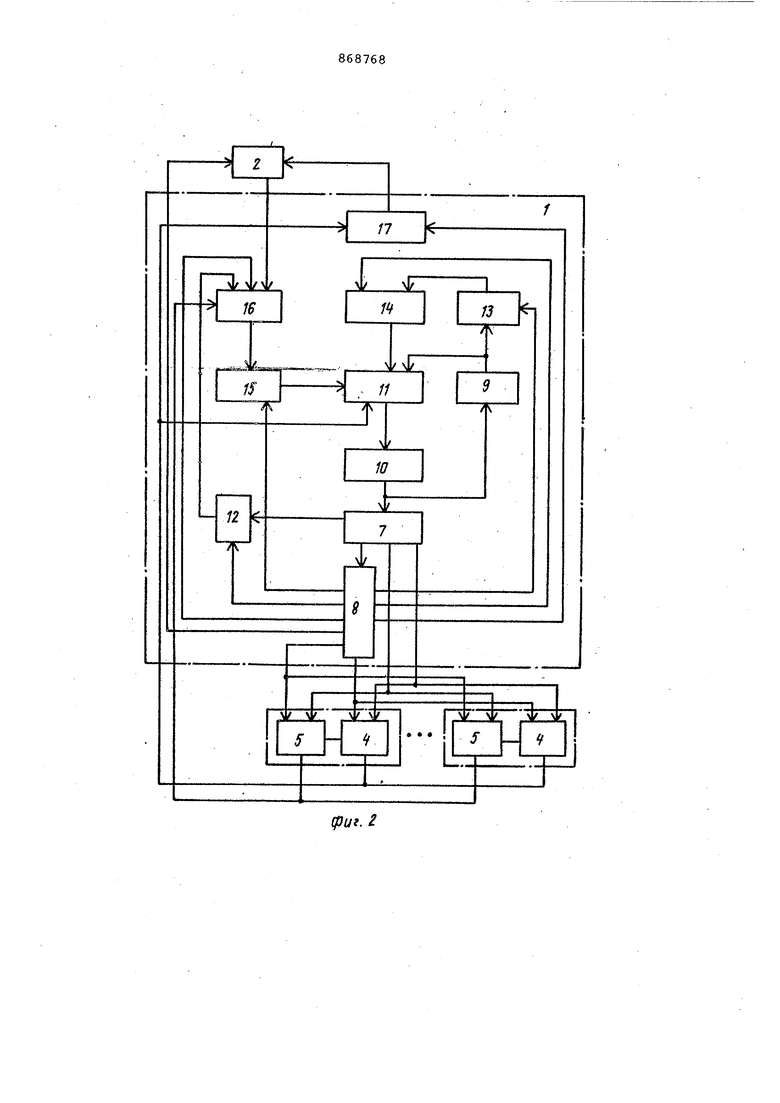

Устройство упра:вления содержит память, арифметико-логический блок, амять исключаемых строк и столбцов, регистр микрокоманд, регистр адреса, счетчик адреса, регистр условий, комутатор адреса ветвления, регистр адреса возврата, коммутатор условий и коммутатор выбора адреса, причем первый, второй, третий и четвертый выходы памяти соединены соответственно с вторым и четвертым выходами устройства и первыми входами арифметикологического блока и регистра микрокоманд, первый, второй и третий выходы которого соединены соответственно с первым, третьим и пятым выходами устройства, четвертый, пятый и шестой выходы регистра микрокоманд соединены соответственно с первыми входами памяти исключаемых строк и столбцов, коммутатора адреса ветвления и регистра адреса возврата,выход которого соединен с вторым входом коммутатора адреса ветвления,выход которого соединен с первым входом коммутатора выбора адреса, выход которого через регистр адреса соединен с первым входом памяти и входом счетчика адреса, выход которого соединен с вторыми входами регистра адреса возврата и коммутатора выбора адреса, третий вход которого и второй вход памяти исключаемых строк и столбцов соединены с вторым входом устройства, первый и третий входы которого соединены соответственно с первым и вторым входами регистра условий, выход которого и седьмой выход регистра микрокоманд через коммутатор условий соединены с четвертым входом коммутатора выбора адреса, восьмой выход регистра микрокоманд и выход арифметико-логического блока соединены Соответственно с третьим и четвертым входами регистра условий, второй вход арифметико-логического блока соединен с девятым выходом регистра микрокоманд.

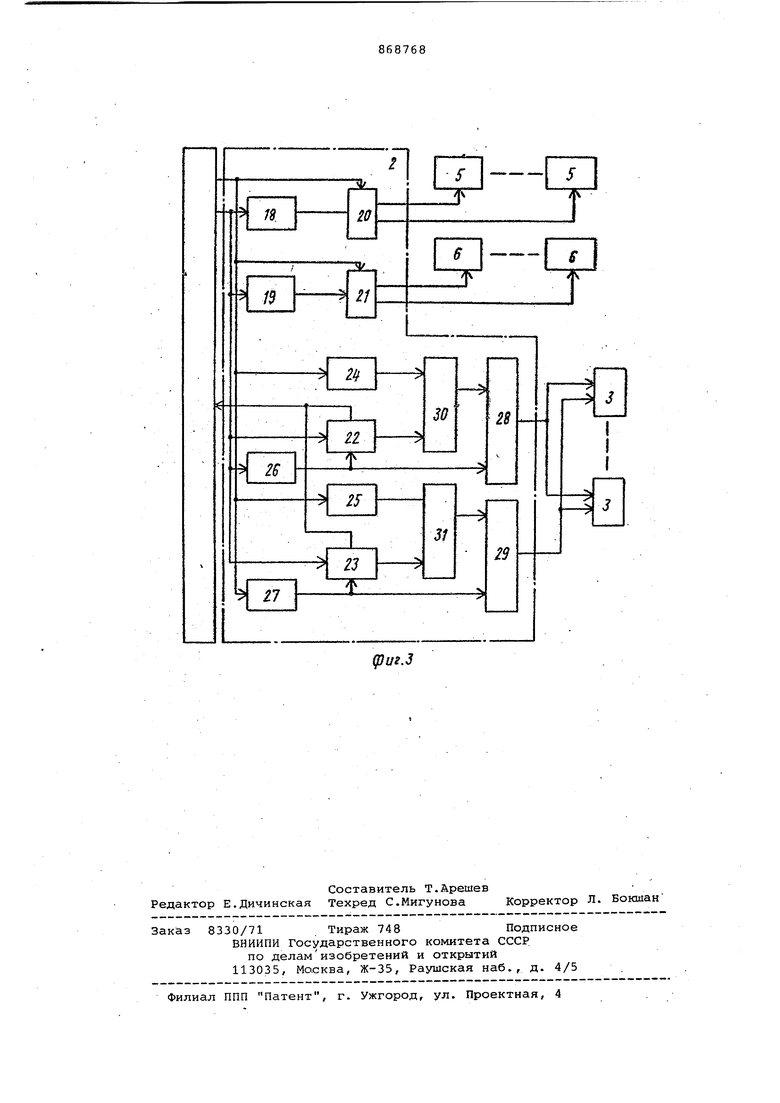

Блок переадресации содержит два дешифратора, два сумматора, регистр номера столбца, регистр номера строки, регистр модификации адреса строки,регистр модификации адреса столбца, регистр текущего адреса строки, регистр текущего адреса столбца,две схемы сравнения, два элемента И,причем входы регистров модификации адреса строки и столбца, регистров текущего адреса строки и столбца, первые входы регистров номера строки и столбца соединены с первым входом блока, входы дешифратора и первые

входы схем сравнения соединены со вторым входом блока, выходы первого и второго дешифраторов через регистр номера строки и регистр номера столбца соответственно соединены с первой и второй группами выходов блока,выход регистра модификации адреса строки и первый выход первой схемы сравнения через первый элемент И соединены с первым входом первого сумматора, выход которого соединен с первым выходом блока, выход регистра текущего адреса строки соединен с вторыми входами первого сумматора и первой схемы сравнения, выход регистра модификации адреса столбца и первый выход второй схемы сравнения через второй элемент И соединены с пер.вым входом второго сумматора, выход которого соединен с вторым выходом блока, выход регистра текущего адреса столбца соединен с вторыми входами второго сумматора и второй схемы сравнения, выходы которой и первой схемы сравнения соединены с третьим выходом блока.

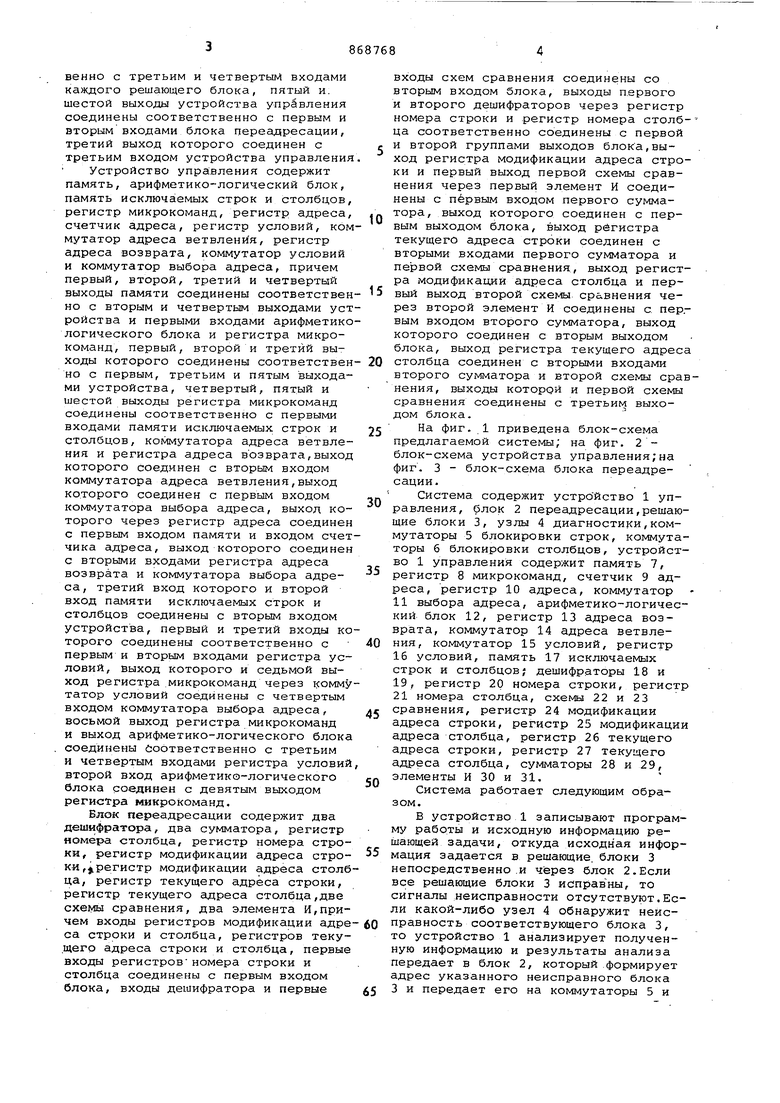

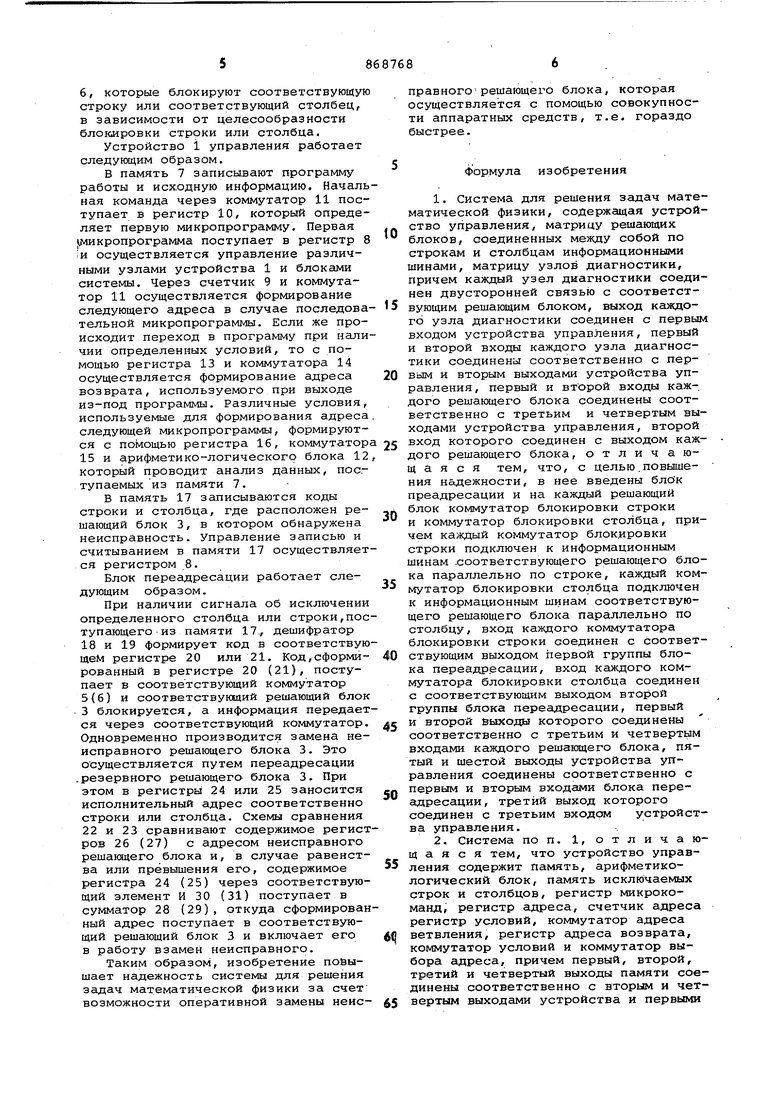

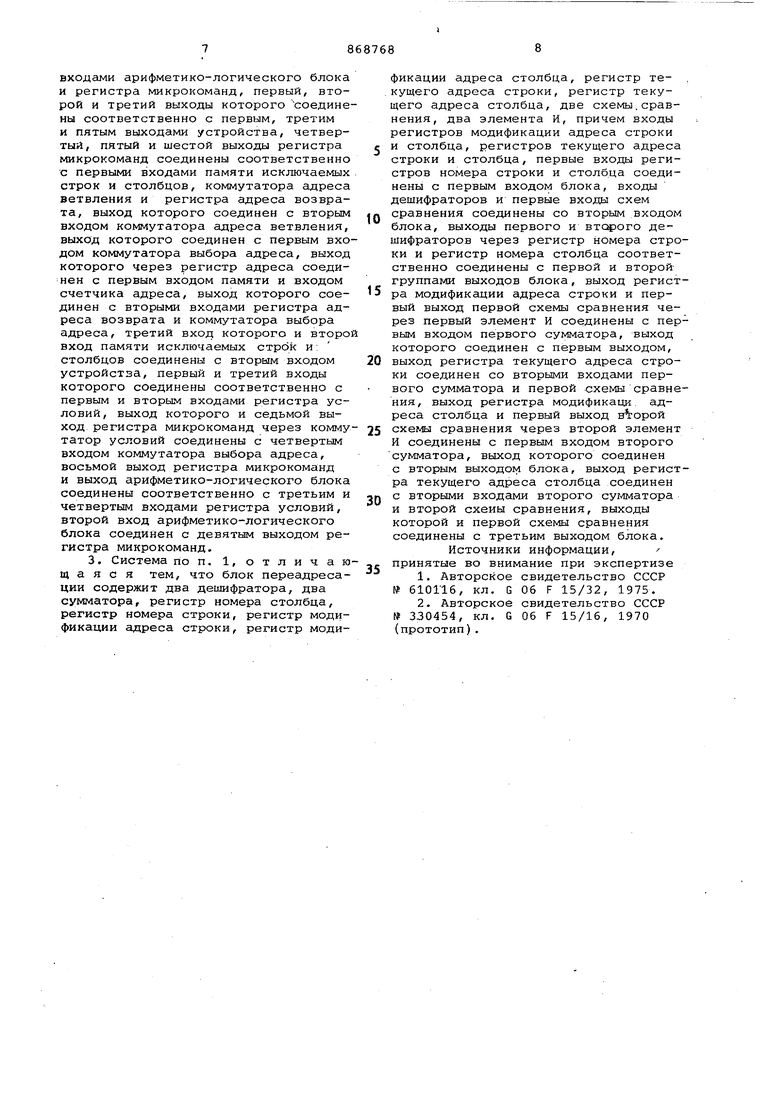

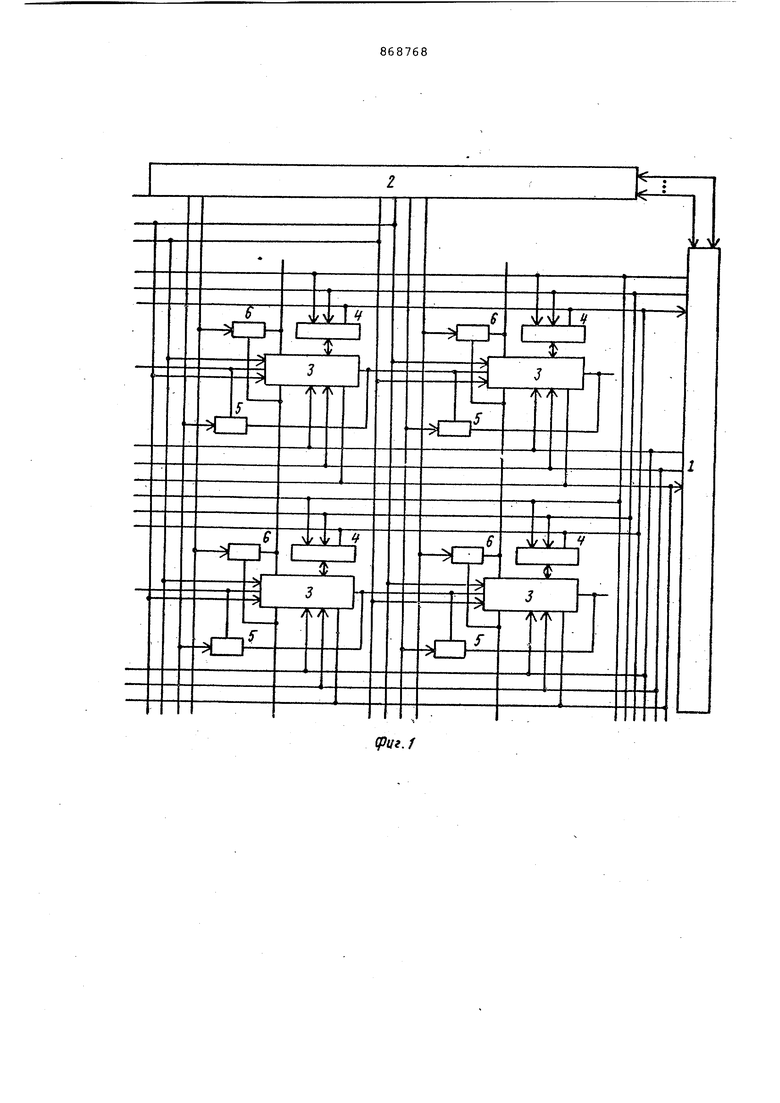

На фиг. 1 приведена блок-схема предлагаемой системы; на фиг. 2 блок-схема устройства управления;на фиг. 3 - блок-схема блока переадресации.

Система содержит устройство 1 управления, блок 2 переадресации,решающие блоки 3, узлы 4 диагностики,коммутаторы 5 блокировки строк, коммутаторы б блокировки столбцов, устройство 1 управления содержит память 7, регистр 8 микрокоманд, счетчик 9 адреса, регистр 10 адреса, коммутатор 11 выбора адреса, арифметико-логический блок 12, регистр 13 адреса возврата, коммутатор 14 адреса ветвления, коммутатор 15 условий, регистр 16 условий, память 17 исключаемых строк и столбцов; дешифраторы 18 и 19, регистр 20 номера строки, регистр 21 номера столбца, схемы 22 и 23 сравнения, регистр 24 модификации адреса строки, регистр 25 модификации адреса столбца, регистр 26 текущего адреса строки, регистр 27 текущего адреса столбца, сумматоры 28 и 29, элементь И 30 и 31,

Система работает следующим образом,

В устройство 1 записывают программу работы и исходную информацию решающей задачи, откуда исходная информация задается в решающие, блоки 3 непосредственно .и через блок 2.Если все решающие блоки 3 исправны, то сигналы неисправности отсутствуют,Если какой-либо узел 4 обнаружит неисправность соответствующего блока 3, то устройство 1 анализирует полученную информацию и результаты анализа передает в блок 2, который формирует адрес указанного неисправного блока 3 и передает его на коммутаторы 5 и

6, которые блокируют соответствующую строку или соответствующий столбец, в зависимости от целесообразности блокировки строки или столбца.

Устройство i управления работает следующим образом.

В память 7 записывают программу работы и исходную информацию. Начальная команда через коммутатор 11 поступает в регистр 10, который определяет первую микропрограмму. Первая микропрограмма поступает в регистр 8 ;и осуществляется управление различными узлами устройства 1 и блоками системы. Через счетчик 9 и коммутатор 11 осуществляется формирование следующего адреса в случае последовательной микропрограммы. Если же происходит переход в программу при наличии определенных условий, то с помощью регистра 13 и коммутатора 14 осуществляется формирование адреса возврата, используемого при выходе из-под программы. Различные условия, используемые для формирования адреса следующей микропрограммы, формируются с помощью регистра 16, коммутатор 15 и арифметико-логического блока 12 который проводит анализ данных, поступаемых из памяти 7.

В память 17 записываются коды строки и столбца, где расположен решающий блок 3, в котором обнаружена неисправность. Управление записью и считыванием в памяти 17 осуществляется регистром 8.

Блок переадресации работает следующим образом.

При наличии сигнала об исключении определенного столбца или строки,поступающего из памяти 17, дешифратор 18 и 19 формирует код в соответствующем регистре 20 или 21. Код,сформированный в регистре 20 (21), поступает в соответствующий коммутатор 5(6) и соответствующий решающий блок 3 блокируется, а информация передается через соответствующий коммутатор. Одновременно производится замена неисправного решающего блока 3. Это осуществляется путем переадресации .резервного решающего блока 3. При этом в регистры 24 или 25 заносится исполнительный адрес соответственно строки или столбца. Схемы сравнения 22 и 23 сравнивают содержимое регистров 26 (27) с адресом неисправного решающего блока и, в случае равенства или превышения его, содержимое регистра 24 (25) через соответствующий элемент И 30 (31) поступает в сумматор 28 (29) , откуда сформированный адрес поступает в соответствующий решающий блок 3 и включает его в работу взамен неисправного.

Таким образом, изобретение пойышает надежность системы для решения задач математической физики за счет возможности оперативной замены неисправного решающего блока, которая осуществляется с помощью совокупности аппаратных средств, т.е. гораздо быстрее.

Формула изобретения

входами арифметико-логического блока и регистра микрокоманд, первый, второй и третий выходы которого соединены соответственно с первым, третим и пятым выходами устройства, четвертый, пятый и шестой выходы регистра микрокоманд соединены соответственно с первыми входами памяти исключаемых строк и столбцов, коммутатора адреса ветвления и регистра адреса возврата, выход которого соединен с вторым входом коммутатора адреса ветвления, выход которого соединен с первым входом коммутатора выбора адреса, выход которого через регистр адреса соеди нен с первым входом памяти и входом счетчика адреса, выход которого соединен с вторыми входами регистра адреса возврата и коммутатора выбора адреса, третий вход которого и второ вход памяти исключаемых строк и: столбцов соединены с вторым входом устройства, первый и третий входы которого соединены соответственно с первым и вторым входами регистра условий, выход которого и седьмой выход регистра микрокоманд через коммутатор условий соединены с четвертым входом коммутатора выбора адреса, восьмой выход регистра микрокоманд и выход арифметико-логического блока соединены соответственно с третьим и четвертым входами регистра условий, второй вход арифметико-логического блока соединен с девятым выходом регистра микрокоманд.

Q сравнения соединены со вторым входом блока, выходы первого и второго дешифраторов через регистр номера строки и регистр номера столбца соответственно соединены с первой и второй группами выходов блока, выход регистра модификации адреса строки и первый выход первой схемы сравнения через первый элемент И соединены с первым входом первого сумматора, выход которого соединен с первым выходом,

0 выход регистра текущего адреса строки соединен со вторыми входс1ми первого сумматора и первой схемы сравнения, выход регистра модификаци адреса столбца и первый выход второй

5 схемы сравнения через второй элемент И соединены с первым входом второго сумматора, выход которого соединен с вторым выходом блока, выход регистра текущего адреса столбца соединен

п с вторыми входами второго суглматора и второй схемы сравнения, выходы которой и первой схемы сравнения соединены с третьим выходом блока. Источники информации,

. принятые во внимание при экспертизе

фиг, 2

(риг.З

Авторы

Даты

1981-09-30—Публикация

1979-03-21—Подача