Изобретение относится к электронным

дискретным устройствам систем автоматики, телемеханики, вычислительной техники и связи и может быть использовано в системах сбора, обработки и передачи многоканального потока информации.

Известно устройство для преобразования временных интервалов в двоичный код, содержащее код управления, генератор тактовых импульсов, подключенные к его выходу счетчики, блок вывода информации и логические элементы til

Работа этого устройства основана на подсчете числа периодов генератор а тактовых импульсов в измеряемые интерЬа- лы времени и представлении полученного числа в двоичном коде, однако оно не может обеспечить надежный прием и достоверную регистрацию поступающих с переменной интенсивностью мощных потоков данных, когда скорость поступления и объем информации значительно превышает пропускную способность средств обработки, и поэтому они не могут быть

использованы в современных системах вьпшслительной техники, предназначенных для приема и обработки данных, поступающих к ним по каналам связи от множества отдаленных терминалов.

Известно устройство для преобразования временных интервалов в двоичный код для процессора сбора, обработки и передачи многоканального потока информации, которое содержит процессор, входящие в состав процессора блок управления и блок памяти, а также схему сравнения, регистр ащзеса массива двоичных кодов, подключенный выходом к входу блока памяти процессора, буферный регистр 5 и счетчик с дешифратором на выходе Г23.

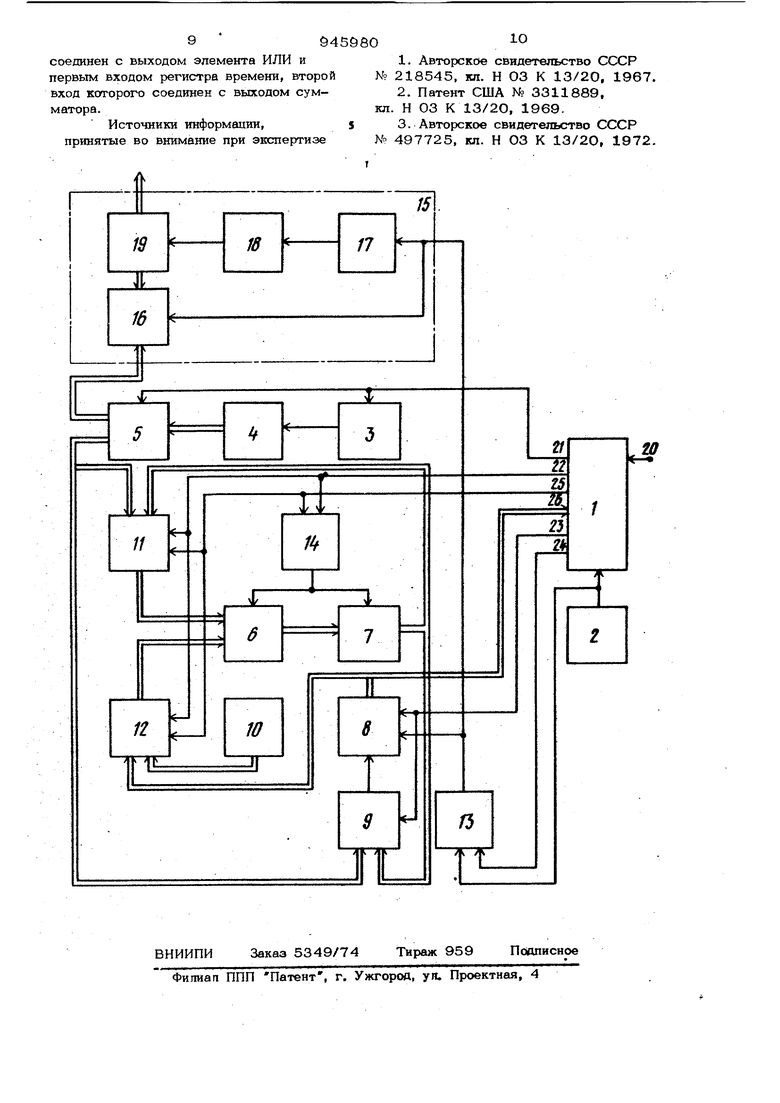

Недостатком известного устройства является отсутствие в нем средств для предотвращения ошибок, возникающих вследствие т робления кодовых посылок (а значит и срответствукщкх км временных интервалов) при передаче информации по каналам связг. Вследствие этого ло1жные изменения состояния канала воспринимаются устройством как истинные, что приводит к неверному принятию реше ния о значении единиц информации, содержащихся в дробленых временных интервалах. Наиболее близким по технической сущ ности является устройство для преофазования временных интервалов в двоичный код, содержащее блок управления с генератором тактовых импульсов на входе, регистр адреса, подключенный к вход блока памяти, регистр числа, блок вычитания, сумматор, блок скорости канала и блок вывода информации, в состав которого входят сдвиговый регистр (буферный регистр) и счетчик с дешифратором на выходе, причем первый выход блока управления подключен к входу регистра адреса и к первому входу регистра числа, второй вход которого соединен с выходом блока памяти, а также блок дополнения до бита, блок остатка преобразования, блок временного интерва Ла и схема сравнения. Блок управления, генератор тактовых импульсов, блок памяти, регист числа, блок вычитания и сумматор входят в состав процессора 3 . Недостатком этого устройства является низкая достоверность преобразовани в случае, если краевые искажения и/или дробление кодовых посылок таково, что длительность принятых временньхх интервалов отличается от длительности передаваемых (идеальных) кодовых посылок более, чем на половину длительности бита. Кроме того, известное устройство, в процессе преобразования производит большое количество операций, что связано с необходимостью сравнения между собой величин временного Интервала, дополнения до бита и остатка преобразования и с принятием тех или иных решений в зависимости от результатов сравне ния. Это ограничивает быстродействие устройства. Цель изобретения - повьпиение достоверности преобразования и быстродействия устройства. Поставленная цель достигается тем, что в устройство для преобразования вре менных интервалов в двоичный код, содерЖЕОдее блок управления, первый вход которого соединен с выходом генератора тактовых импульсов, регистр адреса, выход которого подключен к В(ходу блока памяти, регистр числа, блок вычитания, сумматор, блой скорости канала и блок вывода информации, первый выход блока управления подклкчен к входу регистра адреса и к первому входу регистра числа, второй вход которого соединен с выходом блока памяти, введены регистр времени, вычитающий счетчик, два коммутатора, элемент ИЛИ и элемент И, причем второй выход блока управления соединен с первыми входами коммутв горов и элемента ИЛИ, вторые входы которых подключены к третьему выходу блока управления, четвертый выход которого подключен к nepBbnvi входам блока вы читания и вычитающего счетчика, а пятый - к первому входу элемента И, второй- вход которого соединен с выходом генератора тактовых импульсов, а выход - с вторым входом вычитающего счетчика и первым входом блока вывода информации, второй вход которого подключен к первому выходу регистра числа, второй выход которого соединен с третьим входом первого коммутатора и с вторым входом блока вычитания, выход которого подключен к третьему входу вычитающего счетчика, а третий вход - к выходу регистра времени и четвертому входу первого коммутатора, второй вход блока управления соединен с выходом вычитающего счетчика и с третьим входом второго коммутатора, четвертый вход которого подключен к выходу блока скорости канала, выходы первого и второго коммутаторов ПОДКЛКУчены соответственно к первому и второму входам сумматора, третий вход которого соединен с выходом элемента ИЛИ и первым входом регистра времени, второй вход которого соединен с выходом сумматора. На чертеже представлена блок-схема устройства для преобразования временных интервалов в двоичный код. Устройство содержит блок 1 управления, генератор 2 тактовых импульсов, регистр 3 адреса, блок 4 памяти, регистр 5 числа, сумматор 6, регистр 7 времени, вычитающий счетчик 8, блок 9 вычитания, блок 10 скорости канала, два коммутатора 11 и 12, элемент И 13, элемент ИЛИ 14 и блок 15 вывода информации, содержащий сдвиговый регистр 16, счетчик 17, дешифратор 18, ключевой элемент 19, вход 20 пуска, выходы 21-25 блока 1 управления, второй вход 26 блока, Д управления. Блок 1 управления представляет собой конечный автомат, работающий от генератора 2 тактовых импульсов и содержащий, как правило счетчик, дешифратор и распределитель импульсов или же группу триггеров и связанных с ними логических элемевггов. Блок Ю скорости канала может быт вьшолнен в виде регистра, в котором хранится кодовая константа, отображающая представленную допогапггельным кодом половину длительности бита- и характеризующая скорость передачи данных по каналу связи. На чертеже двойными линиями обозна чены шины передачи данных, одинарными линии передачи управляющих сигналов. Устройство работает следующим об. разом; в блок 4 памяти предварительно заносят принятые по каналу связи данные в виде кода состояния канала в сопровож дении кода текущего времени, отобража ющего моменты t , изменения состояни канала. При этом масштаб отсчета време ни всегда можно выбрать таким, чтобы время было представлено в битах и доля бит. По команде Пуск, подаваемой на вход 2О блока 1 управления, последний посылает последовательно по тактам уп-г равляющие сигналы на соответствующие входы блоков ycTppifcTBa. Первый управляющий сигнал поступае с выхода 21 блока 1 управления на первый вход регистра 3 адреса и регистра 5 числа, в результате чего по адресу, хранящемуся в регистре 3 адреса, из блока 4 памяти в регистр 5 числа перецисьюается код времени t изменения состояния канала и код состояния (О или I), предшествующего этому иэменению. В это же время происходит модификация адреса в регистре 3. Затем блок 1 управления осуществляет безусло ный переход во второе состояние, и управляющий сигнал поступает с его выхода 22 на первые (управляющие) входы коммутаторов 11 и 12 и через элемент ИЛИ 14 - на управляющие входы (третий) сумматора 6 и (первый) регистра 7 времени, в результате чего через комму таторы 11 и 12 - на информационные входы (первый и второй) сумматора 6 из регистра 5 числа поступает код первого значения времени t-j изменения сос тояния канала, а из блока 10 скорости канала - код (дополнительный), отображающий отрицательное значение половины длительности бкта (), и результат X) с выхода сумматора 6 заносится в регистр 7 времени. После этого блок 1 управления осуществляет безусловный переход в Третье состояние, и управляющий сигнал с его выхода 21 снова поступает на входы регистра 3 адреса и регистра 5 числа, в результате чего по очередному адресу из блока 4 памяти в регистр 5 числа переписываются данные о втором време-ни t изменения состояния канала и о состоянии канала, предшествующем этому изменению. Далее блок 1 управления осуществляет безусловный переход в четвертое состояние и с его выхода 23 на входы счетчика 8 и блока 9 вычитания поступает сигнал, по которому блок 9 сятределяет разницу между значением времени t и Т поступившими на его информахшонные входы соответственнаиз регистра 5 числа и регистра 7 времени. Целая часть 1 числа, полученного в результате этой операции, отображающая выраженную в битах длительность истинной кодовой посылки, заносится в счетчик 8, с выхода которого эти данные поступают на третий информационный вход коммутатора 12 и на вход 26 блока 1 управления. Если N- О, что может быть только при условии и свидетельствует о дроблении кодовой посылки (истинного временного интервала), то блок 1 управления возвращается в третье состсяние, и повторяется уже сшисанный цикл операций со следующей группой Данных, извлеченных по очередному адресу из блока 4 памяти. Если , то блок 1 управления переходит в пятое состояние. При этом управляюиций сигнал с его выхода 25 поступает .на вторые входы коммутаторов 11 и 12 и через элемент ИЛИ 14 - на вхо.ды сумматора 6 и регистра 7 времени. В результате этого через коммутаторы 11 и 12 на входы сумматора 6 из регистра 7 времени поступает код времени Тх| , а из счетчика 8 - код целого числа N , отображающего длительность первого истинного временного интервала. Ре льтат суилмировйшш Т t заносятся в регистр 7 времени. Он отображает значение времени, соответствующего середине последнего бита первого в юменного интервала (первой кодовой посылки). В общем случае значение времени Т.гТ соответствует середине последнего бита i -ой кодовой посылки. Далее блок 1 управления осуществляет безусловйый переход в шестое состоя ние, и 4epi&3 его взаход 24. на вход элемента И 13 поступает сигнал, разрешакщий прохождение тактовых импульсов генератора 2 на счетный вход счетчика 8 и на сдвигаклций вход регистра 16 и вход двоичного счетчика 17 блока 15 вывода информации. Каждый из этих тактовых импульсов сдвигает влево на один разряд содержимое регистра 16 и при этом в его млад ший разряд заносится бит, значение (О или 1 ) которого соответствует соетрянию канала, зафиксированному в реги ре 5 числа. В то же время каждый тактовый импульс увеличивает на единицу содержимо двоичного счетчика 17 и уменьшает на единицу содержимое счетчика 8. Как только содержимое счетчика 8 станет равным нулю, блок 1 управления возвращается в третье состояние, после чего повторяется уже описанный цикл операций со следующей группой данных, извлеченных по очередному адресу из блока 4 памяти. Таким образом, число т актовых импульсов генератора 2, поступивших на управляющий вход блока 15 вывода информации, а значит и число бит, зарегистрированных в сдвиговом регистре 16 за один цикл, равно N,- . Когда сдвиговой регистр 16 блока 15 вывода информации полностью заполн ется, счетчик 17 переполняется, и на всех его выходах (на чертеже они обозначены одной линией) появляется О, в результате чего на выходе дешифратора 18 появляется сигнал, открывающий клю чевой эпемент 19, через который получе ные в результате преобразования данные выводятся из устройства. Таким образом, предлагаемое устройство, благодаря введению в него вычитающего счетчика, регистра времени, двух коммутаторов, элемента И, элемента ИЛИ и новых связей, позволяет, в от личие от известных устройств, отсчитывать единицы информации не от границ кодовых посылок, более всего подвержен ных искажениям, а от середины бит, где вероятность искажений минимальна, что на 30-80% (в зависимости от интенсив ности помех в канале связи) повышает достоверность обрабатываемой информации. При этом в предлагаемом устройстве отсутствуют операции, связанные с оцен кой дробноу части числа, отофажающего длительность реальных (т.е. имеющих ис кажения) временных интервалов. Вследствие этого на 20% повьшается быстро действие устройства по сравнению с известным устройством ГЗ . Повышение достоверности обрабатываемой информации уменьшает число переспросов и повторных передач данных по каналам связи, что так же, как и повышение быстродействия устройства, приводит к экономии машинного времени, которая в сумме составляет не менее 20%. ; Формула изобретения . Устройство для преобразования временных интервалов в двоичный код, содержащее блок управления, первый вход которого соединен с выходом генератора тактовых импульсов, регистр адреса, выход которого подключен к входу блока памяти, регистр числа, блок вычитания, сумматор, блок скорости канала, и блок вывода информации, первый выход блока управления подключен к входу регистра адреса и к первому входу регистра числа, второй вход которого соединен с выходом блока памяти, отличающееся тем, что, с целью повьпдения достоверности преобразования и быстродействия устройства, в него введены регистр времени, вычитающий счетчик, два коммутатора, элемент ИЛИ и элемент И, причем второй выход блока управления соединен с первыми входами коммутаторов и элемента ИЛИ, вторые входы которых подключены к третьему выходу блока управления, четвертый выход которого подключен к первым входам блока вычитания и вычитаюшего счетчика, а пятый - к первому входу элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, а выход - с вторым входом вычитаюшего счетчика и с первым входом блока вывода информации, второй вход которого подключен к первому выходу регистра числа, второй выход которого соединен с третьим входом первого коммутатора и с вторым входом блока вычитания, выход которого подключен к третьему входу вычитающего счетчика, а третий вход - к выходу регистра времени и четвертому входу третьего коммутатора, второй вход блока управления соединен с выходом вычитающего счетчика и с третьим входом второго коммутатора, четвертый вход которого подключен к выходу блока скорости канала, выходы первого и второго коммутаторов подключены соответственно к первому и второму входам сумматора, третий вход которого

соединен с выходом элемента ИЛИ и первым входом регистра времени, второй вход которого соединен с выходом сумматора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 218545, кп. Н ОЗ К 13/20, 1967.

2.Патент США № 3311889, кл. Н 03 К 13/2О, 1969.

3.Авторское свидетельство СССР

№ 497725, кл. Н ОЗ К 13/2О, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования временных интервалов в двоичный код | 1981 |

|

SU983638A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| СИСТЕМА УЧЕТА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2003 |

|

RU2247994C1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1612378A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

Авторы

Даты

1982-07-23—Публикация

1980-12-02—Подача