Изобретение относится к импульсно технике и может использоваться для обнаружения и восстановления потери импульса в двухтактной последовательности.

По основному авт. св. № 813742 известно устройство для обнаружения потери импульра, содержащее первый квазиселектор, выход которого подключен к одному из входов первого элемента И, второй квазиселектор, два элемента ИЛИ, второй элемент И, элемент НЕ и формирователь, причем .вход первого квазиселектора соединен с выходом второго элемента И, один из входов которого соединен с выходом элемента НЕ, вход которого соединен с выходом первого квазиселектора и одним из входов первого элемента ИЛИ, к второму входу которого . подсоединен выход второго квазиселектора, а его вхоод соединен -с выходом первого элемента И, втсйрюй вход которого соединен с вторым входом второго элемента И, выходной шиной и выходом второго элемента ИЛИ, первый вход которого соединен с входной шиной, а второй с выходом формирователя, вход которого подключен к выходу первого элемента ИЛИ 1.

Недостатком известного устройства является его неспдсобность контролировать и восстанавлнйать импульс в двухтактных последовательностях.

Чтобы проконтролировать двухтактные по-ёледовательности импульсов, необходимо использовать два известных устройства (для каждой последо- , вательности импульсов отдельно). Таким образом, известное устройство имеет ограниченные функциональные возможности.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения контроля двухтактных импульсных последовательноетей.

Поставленная цель достигается тем что в устройство дополнительно введены третий элемент ИЛИ, элемент задержки, счетный триггер и третий и четвертый элементы И, вторая входная шина, при этом первые входы введенных элементов И подключены соответственно к выходам счетного триггера, вторые входы - к выходу элемента задержки, вход которого соединен с входом счетного триггера и подключен к выходу второго элемента ИЛИ, входы третьего элемента ИЛИ соединены соответственно с первой и второй входными шинами, а выход соединен с первым входом второго элемента ИЛИ

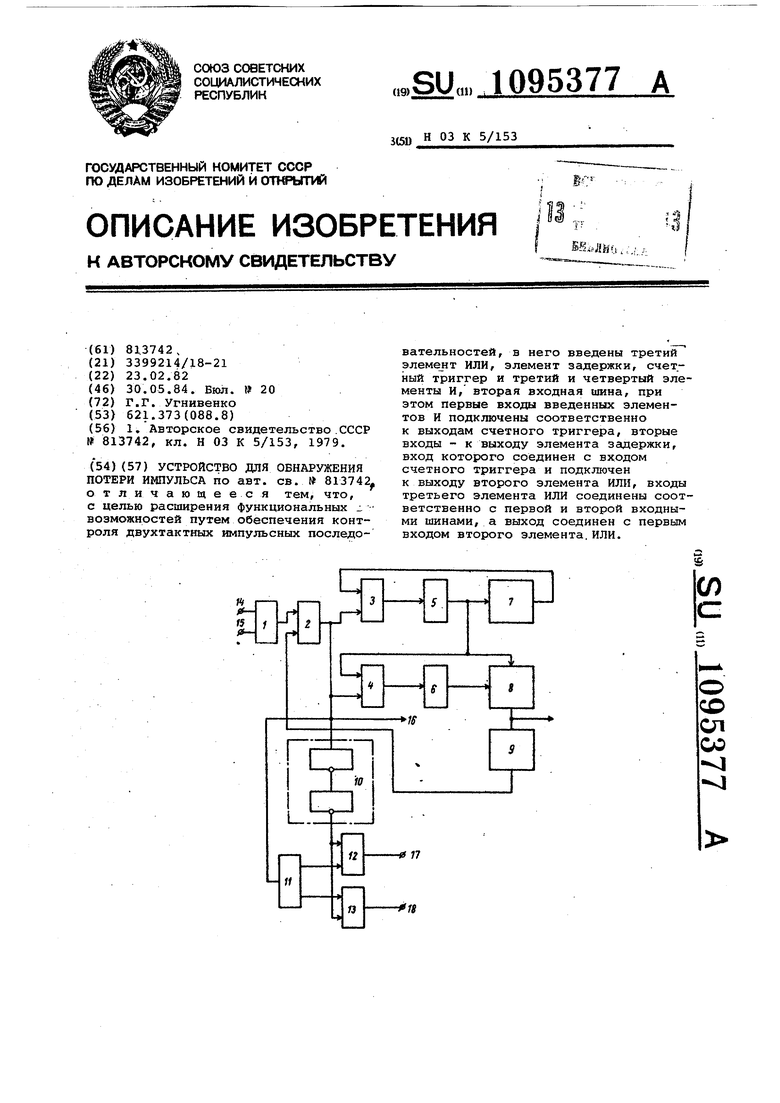

На чертеже приведена структурная схема устройства.

Устройство для обнаружения потери импульса содержит третий, второй элементы ИЛИ 1, 2, первый, второй

элементы И 3, 4, квазиселекторы 5 и 6, элемент НЕ 7, первый элемент ИЛИ 8, формирователь 9, элемент 10 задержки, счетный триггер 11, третий и четвертый элементы И 12 и 13.

Входы элемента ИЛИ 1 подключены к входным шинам 14 и 15, а выход соединен с первым входом второго элемента ИЛИ 2, другой вход которого подключен к выходу формирователя 9, Выход элемента ИЛИ 2 соединен с первьаии входами элементов И 3 и 4, с входом элемента 10 задержки, входом счетного триггера 11 и выходной шиной 16 устройства. Другой вход элемента И 3 подключен к выходу элемента НЕ 7, а выход - к входу квазиселетора 5. Другой вход элемента И 4 связан с выходом квазиселектора 5, входами элементов НЕ 7 и ИЛИ 8, а выход с входом квазиселектора 6. Выход пои следнего подключен к другому входу элемента ИЛИ 8, выход которого соединен с входом формирователя 9. Выходы счетного триггера 11 связаны соответственно с первыми входами элементов И 12 и 13, вторые входы которых подключены к выхода; элемента 10 задержки, а выходы - соответственно к тактовым выходам 17 и 18 устройства. В качестве элемента 10 задержки можно использовать, например, два последовательно включенных элемента НЕ.

Устройство работает следующим образом.

В исходном состоянии на входах квазиселекторов 5 и б присутствуют сигналы, которые является запрещающи ми для элемента И 4.

Сигнал с выхода кваэиселёктора 5; пройдя через элемент НЕ 7, будет разрешающим для элемента ИЗ. Таким образом, в исходном состоянии иа одном из входов элемента И 3 присутствует раорешающий сигнал, а на входе элемента И 4 - запрещающий.

Двухтактные импульсы поступают на входы э лемента ИЛИ 1, а на его выходе создается прямая последовательность импульсов, так как элемент ИЛИ 1 преобразует двухтактные импульсы в прямую (однотактную) последовательность импульсов. Эти импульсы поступают на вход элемента ИЛИ 2, с выхода которого проходят далее на вход элементов И 3 и 4, также на вход элемента 10 задержки и счетного триггера 11.

Под воздействием импульса триггер И измеряет свое состояние на противоположное, при этом на один из элементов И, например И 12, поступает -; разрешающий сигнал, а на элемент И 13 - запрещающий.

После того, как триггер 11 переключил я, с небольшой задержкой во времени на другие входы элементов И 12 и 13 поступают тактовые импульсы. При поступлении следующего импуль 3109 са на вход триггера 11 и элемента ГО задержки работа последних полностью повторяется, но при этом выходной импульс появляется на другом тактовом выходе. В эти же моменты времени импульсы поступают также на входы элементов И 3 и . Так как на втором входе элемента И 4 присутствует запрещающий сигнал, а на втором входе элемента И 3 присутствует разрешающий сигнал, то входной импульс проходит на вход квазиселектора 5, срабатывает с задержкой, равной длительности входного импульса, что исключает одновременное воздействие входного сигнала на элемент И 4. Квазиселектор 5 переходит в режим измерения временного интервала между импульсами. При этом элемент И 3 запирается, а на элемент и 4 поступает разрешающий сигнал с выхода квазиселектора 5, тем самым подготавливая его к приему следующего импульса. Следующий импульс из импульсной последовательное1И может пройти только на вход квазиселектора 6, так как элемент И 4 . подготовлен,т. е. на одном из его входов присутствует сигнал разрешения с выхода квазиселектора 5. Как только импульс поступает на . вход квазиселектора 6, он без задержки переходит в режим измерения временного интервала между импульсами с учетом длительности импульса. Таким образом, на вход квазиселекторов 5 и б поочерёдно поступают импульсы, они срабатывают и на одном из входов элемента ИЛИ 8 все время имеется сигнал, и, следовательно, на его выходе сигнал не изменяется и не воздействует на формирователь 9. При потере одного из импульсов один из квазиселекторов не срабатывает, а другой возвращает в исходное состояние, при этом на выходе эле74мента ИЛИ 8 состояние сигнала иэменяётся. В ответ на изменение входного сигнала на выходе формирователя 9 появляется импульс, аналогичный входным. Этот импульс с-выхода формирователя 9 поступает на вход элемента ИЛИ. 2 и с его выхода - на выходную шину, к которой подключены входы элемента 10 задержки и счетного триггера 11. Последние срабатывают и, несмотря на потерю входного импульса, на одном из выходов 17 и 18 появляется выходной импульс, Таким образом, в нагрузке автоматически восстановлен исчезнувший импульс. Кроме того, импульс с выхода формирователя 9 или с выхода элемента ИЛИ 8, в случае необходимости, можно использовать для информации о имевшем место случае потери импульса, При потере полностью двухтактных входных импульсов на входе устройства квазиселекторы возвращаются в исходнов состояние и постоянный сигнал на выходе элемента ИЛИ 8 можно использовать как информацию о полной потере входной последовательности импульсов. Использование предлагаемого устройства для обнаружения потери импульса в двухтактных последователькостях импульсов по сравнению с известным позволяет контролировать двухтактные входные импульсы, восстанавливать импульс при его потере и выдавать информацию при отказах, Устройство - прототип может контролировать и восстанавливать импульспрямой последовательности, а предложенное устройство может также контролировать и двухтактную последовательность импульсов, что подтверждает его более широкие функциональные возможности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения потерииМпульСА | 1979 |

|

SU813742A1 |

| Устройство для обнаружения потери импульса | 1981 |

|

SU1046925A1 |

| Устройство для контроля последовательности импульсов | 1975 |

|

SU748843A1 |

| Устройство для обнаружения потери импульса | 1986 |

|

SU1406755A1 |

| Устройство для обнаружения потери импульса | 1977 |

|

SU621081A1 |

| Устройство для обнаружения потери импульса | 1983 |

|

SU1157670A1 |

| Селектор импульсной последовательности | 1978 |

|

SU790239A1 |

| Устройство для обнаружения потери | 1978 |

|

SU731572A2 |

| Устройство для контроля регистра сдвига | 1978 |

|

SU752487A1 |

| Устройство для обнаружения потерииМпульСОВ | 1979 |

|

SU834877A1 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПОТЕРИ ИМПУЛЬСА по авт. св. № 813742. отличающееся тем, что, с целью расширения функциональных L возможностей путем обеспечения контроля двухтактных импульсных последовательностей, в него введены третий элемент ИЛИ, элемент задержки, счетный триггер и третий и четвертый элементы И, вторая входная шина, при этом первые входы введенных элементов И подключены соответственно к выходам счетного триггера, вторые входы - к выходу элемента задержки, вход которого соединен с входом счетного триггера и подключен к выходу второго элемента ИЛИ, входы третьего элемента ИЛИ соединены соответственно с первой и второй входными шинами, а выход соединен с первым входом второго элемента,ИЛИ. S (Л СП со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-05-30—Публикация

1982-02-23—Подача