сд

4

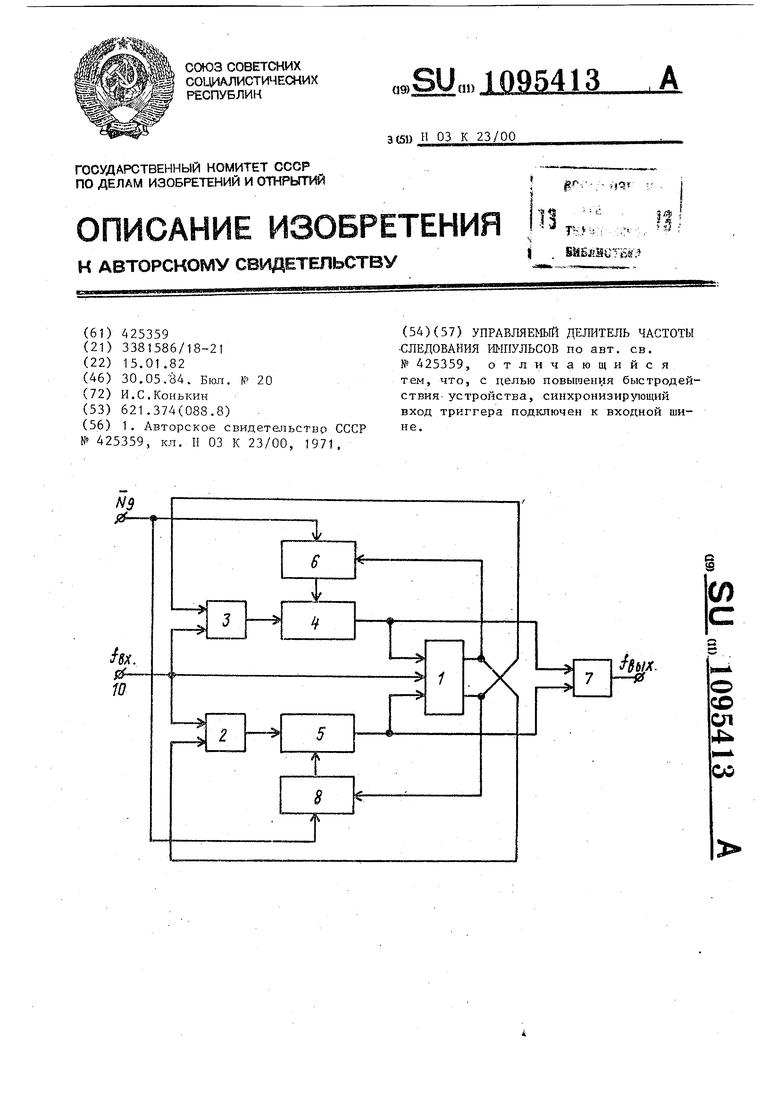

ОС 1 И;-1оГ)р етение (п-цгк.мп-ся к имт1ул1,сио технике и может ,зоваться п устройствах, где иеобходимп леление частоты слел.ования импу.льсов. По основному . св. № 425359 lis вестей управляемьй делитель частоты следования импульсов, содержл1П,ий пер вый счетчик нммульсов. инфop aцнoняы вход которого через ггервьп блок запи обратного кода соединен с шиной информационного входа, BTOpofi счетчик импульсов и второг блок записи обратного кода, элемент , два элеме та И и триггер, причем вхолдная тина, через элементы И соединена со счетными входами первого и второго счетчиков импульсов, ин(iк p aдиoIiньг r вход второго счетчика имнуди-.сов через вто рой блок записи обратного кода соеди нен с и.шпой информацио1и-юго входа нулевой выход триггера coe/aiiien с первьпч элементом и вторьм блоком записи обратного кода , :i счетчико.з импульсов соединеп с нулевым и единичным входамт-1 триггера и элеMeirroM ИЛИ, выхо/ которого подключен к выход1юй шине l . Однако данный делитель характеризуется н с д оста т о ч н ым б ые тр од е iic т в и с м Это обьясняется тем, что выходы счет чиков подключены к единичному и нуле вому входам триггера. При таком вклю чении триггера скорость переключе ;ия счетчиков определяется временем переключения этого триггер. и как ми никум триггера счетчика. Цель изобретения - повышерие быстродействия делителя. Поставлен; ая п,ель достигается тем что в управляемый .делитель частоты следования импульсов, с одержак ий первый счетчик импульсов, информанионньй вход, которого через первый блок записи обратггого кода соединен с ип.ной 1-пк1)орма1и1О1И1ого входа, второй счетчик импульсов и второй блок записи обратного кода, элемент ИЛИ, два элемента И и триггер, причем входная шина через эдементы И соединена со счетпымн входами первого и второго счетчиков импудьсов, информационный вход второго счетчика импульсов через второй блок записи обратного код соединен с шиной информационного вхо да, нулевой выход триггера еоединен первым элементом И и вторым блоком записи обратного кода, единичный выход триггера соединен с вторым элементом И и первым блоком записи обра 2 Н(1го кода, а выходы счетчиков импулт сов соедлнены с нулевым и единичным входами триггера и элементом ИЛИ. вьгход которого подтсиючен к выходной тине , глжхронизирующиГг, вход триггера тюдключе} к входной шине. Па чертеже представлена структурная схема предлагаемого устройства. Устройство содержит триггер 1, первый и второй элементы 2 и 3 И, первый и второй счетчики 4 и 5 импульсов, первый блок 6 записи обратного кода, элемент 7 ИЛИ, второй блок 8 записи обратного кода, причем информационные входы ечетчикоп 4 и 5 соединены через блоки 6 и 8 соответственно с шиной 9 информлцио июго входа, входная тина 10 через соответствующие эдементы 2 и 3 соединена со счетными входами счетчиков 4 и , нулевой выход триггера 1 соединен с элементом 3 и блоком 8, единичный выход триггера 1 соединен с элементом 2 и блоком 6, а выходы счетчиков 4 и 5 соединены с единичным и нулевым входами триггера 1 и элементом 7, выход которого подключен к выходной шине, а синхронизир тощий вход триггера 1 подключен к входной шине. Делитель работает следуюцим образом . Пусть триггер 1 находится в состоя1н-1И О, при котором на элемент 2 поступает сигнал запрета, а на элемент 3 сигнал разрешения. Импульсы входного сигнала Непрерывно поступают на входы элементов 2 и 3 и на синхронизир 10 1гий вход триггера 1 . Через открытый элемент 3 входнрле импульсы поступают в счетчик 4. В счетчик 5 в это время через открьггый блок 8 производится запись обратного кода К. Приняв N-1 входных импульсов, счетчик 4 заполняется, на выходе его возншсает сигнал заполнения, который поступает на единичный вход триггера 1 15 следуто 1):ий (М-й) входной импульс переключает триггер 1 в состояние 1. В таком состоянии ia элемент 3 поступает запрет, а на элемент 2 - разрешение и счетчик 5 на гинает счет входных импульсов. В счетчик 4 в это время через открытый блок 6 производится запись обратного кода. Когда счетчик 5, приняв М-1 входных импульсов, загюлпяется, на выходе его также возникает сигнал, который поступает на нулевой вход триггера 1 , и следутощий входной импульс переключает его в нуI 10954134

левое состояние. При этом цикл работыДанная схема управляемого делителя

делителя завершается. Выходной сигналчастоты следования импульсов позволяет

fgxсущественно повысить быстродействие

делителя gj,- формируется эле-управляемого делителя частоты, так

ментом 7, на входы которогос как скорость переключения счетчиков

подаются сигналы счетчиков 4определяется временем переключения

и 5.толького одного триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты | 1983 |

|

SU1173554A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Управляемый генератор импульсов | 1985 |

|

SU1267594A1 |

| Управляемый делитель частоты | 1975 |

|

SU524320A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU866748A1 |

| Устройство для измерения отношения частот последовательностей импульсов | 1988 |

|

SU1599793A1 |

| Устройство для тактовой синхронизации канала цифровой магнитной записи-воспроизведения | 1987 |

|

SU1432598A2 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2028728C1 |

| Устройство для воспроизведения цифровой информации | 1984 |

|

SU1167645A1 |

УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ -СЛЕДОВАНИЯ ИМПУЛЬСОВ по авт. св. № 425359, отличающийся тем, что, с целью повышения быстродействия устройства, синхронизирующий вход триггера подключен к входной шине.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1971 |

|

SU425359A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-05-30—Публикация

1982-01-15—Подача