режимами работы, пятый вход которого соединен с выходом второго переключателя и с третьим входом блока преобразования код - информация, четвертый вход которого соединен с седьмым выходом дешифратора, восьмой выход которого соединен с вторым входом блока управления частотой, третий вход которого соединен с вторым входом счетчика цикла и с девятью выходом дешифратора, десятьп в,1ход которого соединен с четвертым входом блока управления частотой, пятый вход которого соединен с первым выходом блока преобразования код информация, второй выход которого соединен с девятым входом дешифратора и с пятьм входом блока контроля, шестой вход которого, соединен с одиннадцатым выходом дешифратора, двенадцатый выход которого соединен с шестым входом блока управления режимами работы, седьмой вход которого соединен с десятым входом деш-гфратора, тринадцатьп1 выход которого Соединен с первым входом второго пере1члючателя, второй вход которого соединен с седьмым выходом блока управления ренсимами работы, причем первый вход третьего переключателя соединен с пятым входом блока преобразования код - информация и с вькодом блока преобразования информация - код, третий вход которого соединен с дополнительным выходом сдвигового регистра, третий вход которого соединен с третьим выходом блока управления приемо-передачей, четвертьй выход которого соединен с третьим входом блока контроля четности, выход которого соединен с одиннадцатым входом дешифратора и седьмт м входом блока контролЯэ восьмой вход которого соединен с первым входом сдвигового регистра и с третьим выходом блока преобразования код - информация, шестой вход которого соединен с четырнадцатым выходом дешифратора, пятнадцатый выход которого соединен с третьим входок счетчика цикла, вг гходы которого подключены к соответствуюиим входам дешифратора, шестнадцатый выход которого соединен с управляющим входом блока формирования контрольного кода, соответствуюш 1е входы которого соединены с соответствующими выходами блока входных переключателей, соответствующие входы которого соединены

10

4 с рь ходами буферного регистра и с

соответствуюш 1ми входами регистра управления, управляющие выходы которого подключены к управляющим входам блока входных переключателей, соответствующие выходы блока формирования контрольного кода подключены к соответствую1цим входам регистра сдвига, четвертый вход которого соединен с пятым выходом блока управления приемо-передачей, седьмой вход блока преобразования код - информация соединен с выходом третьего переключателя, второй вход которого соединен с семнадцатым выходом деиифратора.

2.Устройство по п. 1, о т л и ч а КЗ щ е е с я тем, что каждый переключатель содержит два усилителя, ключевой элемент, элемент И и элемент НЕ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом первого усилителя, вход которого соединен

с первым входом ключевого элемента, второй вход которого соединен с выходом второго усилителя, а управляющий вхо/д ключевого элемента соединен с входом элемента НЕ, причем вход первого усилителя, вход второго усилителя и вход элемента НЕ являются входами переключателя, выходом которого является выход элемента И.

3.Устройство по п. t, отличающееся тем, что блок управления частотой содержит три элемента НЕ, два элемента И-НЕ, элемент ИЛИ, два элемента 2И-ИЛИ-НЕ, триггер, элемент И и счетчик, выходы которого подгслючены к соответствующим входам первого элемента 2И-ИЛИ-НЕ, выход которого соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с входом первого элемента НЕ, выход которого соединен

с первым входом счетчика, второй вход которого соединен с выходом второго элемента НЕ, вход которого соединен с первым входом триггера второй вход которого соединен с выходом элемента И, первый вход которого соединен с выходом второго элемента И-НЕ, первьй вход которого соединен с выходом первого элемента И-НЕ и с первым входом элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента И-НЕ, с выходом триггера и с первым входом второго элемента 2И-ИПИНЕ, второй вход которого соединен с

выходом третьего элемента НЕ. вход которого соединен с третьим входом второго элемента 2И-ИЛИ-НЕ, выход элемента ИЛИ подключен к второму входу элемента И, причем вход второго элемента НЕ, вход первого элемента НЕ, третий вход триггера, вход третьего элемента НЕ и четвертый вход второго: элемента 2И-ИЛИ-НЕ являются соответственно первым, вторым, третьим, четвертым и пятым входами блока управления частотой, выходом которого является выход второго элемента 2И-ИЛИ-НЕ.

4. Устройство по п. 1, отличающееся тем, что блок преобразования код - информация содержит два элемента 2И-ИЯИ, восемь элементов НЕ, семь триггеров, пять элементов И, два элемента И-НЕ, шесть элементов ИЛИ, четыре элемента ИЛИ-НЕ, счетчик и элемент 4И-ИЛИНЕ, выход которого соединен с первым входом счетчика, второй вход которого соединен с первым входом первого элемента И и с выходом первого элемента НЕ, вход которого соединен с первыми входами первого и второго элементов И-НЕ и с выходом первого элемента ИЛИ-НЕ, первый вход которого соединен с выходом второго элемента Ш1И-НЕ, с первыми входами третьего и четвертого элементов ИЛИ-НЕ и с входом второго элемента НЕ, выход которого соединен с первым входом первого триггера, второй вход которого соединен с первым выходом второго триггера и с вторым входом третьего элемента ИЛИ-НЕ, третий вход которого соединен с выходом первого элемента 2И-ИЛИ, с первым входом третьего триггера и с входом третьего элемента НЕ, выход которого соединен с первым входом четвертого триггера -и с вторым входом четвертого элемента ИЛИ-НЕ, третий вход которого соединен с первым входом пятого триггера, с первым выходом первого триггера и с первым входом второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с первым выходом счетчика и с первым входом четвертого элемента И, второй вход которого соединен с вторым выходом счетчика, тре1

04

тйй выход которого соединен с первым входом шестого триггера и с первым входом пятого элемента И, второй вход которого соединен с вторым выходом первого триггера и с вторым входом пятого триггера, первый выход которого соединен с четвертым входом четвертого элемента ИЛИ-НЕ, выход которого соединен с вторым входом первого элемента ИЛИ-НЕ, с первым входом второго элемента ИЛИ и с вторым входом первого элемента И, третий вход которого соединен с выходом первого элемента И-НЕ, с вторым входом второго элемента И-НЕ, с первым и вторым входами элемента 4И-ИЛИНЕ и с входом четвертого элемента НЕ, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом пятого элемента НЕ и с третьим и четвер тым входами элемента 4И-ИЛИ-НЕ, пятый и шестой входы которого соединены с входом пятого элемента НЕ и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента НЕ, вход которого соединен с выходом второго элемента И-НЕ, с седьмым и восьмым входами элемента 4И-ИЛИ-НЕ, с вторым входом первого элемента И-НЕ и с четвертым входом первого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого соединен с первым входом второго триггера второй вход которого соединен с выходом четвертого элемента И, с вторым входом второго элемента И и с третьим входом пятого триггера, второй выход которого соединен с первым входом шестого элемента ШШ, второй вход которого соединен с первым выходом четвертого триггера, второй выход которого соединен с первым входом второго элемента ШВ-1-НЕ и с первым входом седьмого триггера, второй вход которого соединен с вторым входом второго элемента ИЛИ-НЕ и с первым выходом третьего триггера, Лорой выход которого соединен с вторым входом четвертого триггера, третий вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с. вторым входом третьего триггера и с выходом первого элемента ИЛИ, третий вход которого соединен с вторым входом пятого элемента ИЛИ и с вторым входом шестого триггера, выход которого соединен с вторым входом третьего элемента И, первый вход первого элемента 2И-ИЛИ соединен с выходом седьмого элемента НЕ, вход которого соединен с вторым входом первого элемента 2И-ИЛИ, выход седьмого триггера подключен к первому входу второго элемента 2И-ИЛИ, второй вход которого соединен с выходом восьмого элемента НЕ, вход которого соединен с третьим входом второго элеэлемента 2И-ИЛИ, выход пятого элемента И подключен к четвертому входу первого элемента ИЛИ, пятый вход которого соединен с выходом третьего элемента ИЛИ-НЕ, выход четвертого элемента ИЛИ соединен с третьим входом второго элемента И-НЕ, выход третего элемента ИЛИ подключен к третьему входу первого элемента И-НЕ, выход шестого элемента ИЛИ соединен с третьим входом третьего триггера, причем вход пятого элемента НЕ, вход восьмого элемента НЕ, четвертый вход второго элемента 2И-ИЛИ, второй вход пятого элемента ИЛИ, третий, второй и четвертый входы первого элемента 2И-ИЛИ являются соответственно первым, вторым, третьим., четвертым, пятым, шестым и седьмым входами блока преобразования код - информация, первым, вторым и третьим выходами которого -являются соответственно выход второго элемента ИЛИ-НЕ, выход шестого триггера и выход второго элемента 2И-ИЛИ.

5. Устройство по п. 1, отличающееся тем, что регистр управления содержит блок элементов И, блок элементов ИЛИ, блок элементов НЕ, первый и второй блоки элементов ИЛИ-НЕ, регистр, два элемента НЕ, элемент ИЛИ, элемент ИЛИ-НЕ триггер и элемент И, выход которого соединен с входом регистра, выходы которого соединены с первыми входами блока элементов И, выходы которого соединены с первыми входами блока элементов ИЛИ, выходы которого соединены с первыми входами первого блока элементов ИЛИ-НЕ и с входами блока элементов НЕ, выходы которого соединены с первыми входами второго блока элементов ИЛИ-НЕ, вторые входы которого соединены с вторыми входами первого блока элементов ИЛИ-НЕ и с первым входом элемента И, выход первого элемента НЕ,соединен с вторыми входами блока элементов И, с

первым входом элемента ИЛИ-НЕ и с первым входом элемента ИЛИ, выход которого соединен с первым входом триггера, выход которого подключен к вторым входам блока -элементов ИЛИ выход второго элемента НЕ соединен с вторым входом элемента ИЛИ-НЕ, выход которого соединен с вторым входом триггера, причем второй вход элемента ИЛИ, вход второго элемента НЕ, первый вход элемента И, вход первого элемента НЕ, второй вход элемента И и соответствующие входы регистра являются соответственно первым,-вторым, третьим, четвертым, пятым и соответствующими входами регистра управления, управляющими выходами которого являются выходы первого и второго блоков элементов ИЛИ-НЕ.

6. Устройство по п.

отличающееся тем, что блок преобразования информация - код содержит элемент И, элемент ИЛИ, элемент И-НЕ и триггер, первый вход которого соединен с выходом элемента И, первый вход которого соединен с выходом элемента И-НЕ, входы которого соединены с соотве ствующими входами элемента ИЛИ, выход которого соединен с вторым входом элемента И, причем второй вход триггера и входы элемента ИЛИ являются соответственно первым, вторым и третьим входами блока преобразования информация - код, выходом которого является вьгход триггера.

7. Устройство по П-. 1, о т л и ч а, ю щ е е с я тем, что дешифратор содержит элемент ЗИ-ИЛИ, два элемента 4И-Ш1И, два элемента 2И-ИЛИ, девять элементов ИЛИ, двенадцать элементов И, элемент ИЛИ-НЕ, два элемента НЕ, четыре триггера и элемент дешифрации, первый выход которого соединен с первым входом первого триггера, второй вход которого соединен с первым входом первого элемента первым входом второго элемента И и с первым входом второго триггера, второй вход которого соединен с выходом первого элемента ИЛИ и с первьм входом третьего триггера, выход которого соединен с первым входом третьего элемента И,второй вход которого соединен с вторым входом третьего триггера, с первым входом первого элемента 4И-ИЛИ, с

первым входом первогоэлемента 2И-Ш с первым входом второго элемента 2И-ИЛИ, с первым входом второго элемента. 4И-ИЛИ и с первым входом второго элемента ИЛИ, второй вход которого соединен с вторым входом первого элемента 4И-ИЛИ, с вторым входом второго элемента 4И-ИЛИ, с первым входом третьего элемента ИЛИ с первым входом четвертого элемента И, с первым входом пятого элемента И, с первым входом шестого элемента И, с первым входом седьмого элемента И и с первым .входом росъмого элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с первым входом первого элемента ИЛИ и с выходом девятого элемента И, первый вход которого соединен с третьим и с четвертым входами первого элемента 4И-ИЛИ и с вторым выходом элемента дешифрации, третий выход которого соединен с первым входом элемента ЗИ-ИЛИ и с вторым и третьим входами второго элемента 2И-ИЛИ, четвертьй вход которого соединен с первым входом пятого элемента ИЛИ, с вторым входом седьмого элемента И, с пятым и шестым входами первого элемента 4И-ИЛИ с третьим и четвертым входами второго элемента 4И-ИЛИ, с входом первого элемента НЕ и с вторым входом элемента ЗИ-ИЛИ, третий и четвертый входы которого соединены с четвертым выходом элемента дешифрации, пятьш выход которого соединен с пятым входом второго элемента 4И-ИЛИ, шестой вход которого соединен с выходом первого элемента НЕ, с пятым вхдом элемента ЗИ-ИЛИ и с седьмым входом первого элемента 4И-ИЛИ, восьмой вход которого соединен с седьмым входом второго элемента 4И-Ш1И, с выходом второго элемента ИЛИ, с шестым и седьмым входами элемента ЗИ-ИПИ и с первым входом элемента ИЛИ-НЕ, - второй вход которого соеди ней с вторым входом девятого элемента И с первым входом шестого элемента ИЛИ, второй вход которого соединен с первым входом десятого элемента И и с выходом элемента ЗИ-ИЛИ, восьмой вход которого соединен с пятым входом второго элемента 2И-Ш1И, с вторым входом пятого элемента ИЛИ, с девятым входом первого элемента 4И-ИЛИ, с восьмым

04

входом второго элемента 4И-ИЛИ, с вторым входом третьего элемента ИЛИ, с третьим входом элемента ИЛИ-НЕ, с вторым входом пятого элемента И-НЕ , и с вторым входом первого элемента 2И-ИЛИ, третий и четвертый входы которого соединены с выходом второго элемента И и с первым входом седьмого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента ИЛИ, первьй вход которого соединен с выходом седьмого элемента И, шестой выход элемента дешифрации соединен с девятым входом второго элемента 4И-ИЛИ и с десятым входом первого

элемента 4И-ИЛИ, одиннадцатьш вход которого соединен с седьмым выходом . элемента де1ш.1фрации и с десятым и одиннадцаты п1 входа т второго элемента 4И-ИЛИ, выход первого элемента 4И-Ш1И соединен с вторым входом первого элемента ИЛИ, второй вход четвертого элемента И соединен с первым и вторым входами четвертого триггера и с первь& входом одиннадцатого элемента И, второй вход которого соединен с первым выходом четвертого триггера, третий вход кото рого соединен с вторым входом десятого элемента И, третий вход которого соединен с выходом третьего элемента ИЛИ, выход первого триггера соединен с вторым входом первого элемента И, вьксод которого соединен с первым входом девятого элемента НИИ, второй вход которого соединен с выходом двенадцатого элемента И,/первый вход которого соединен с выходом пятого элемента ИДИ, выход седьмого элемента ИЛИ соединен с третьим входом девятого элемента ИЛИ, выход элемента ИЛИ-НЕ соединен с третьим входом первого, триггера и с входом второго элемента НЕ, выход которого соединен с вторым входом шес-того элемента И, выход второго триггере соединен с вторым входом второго элемента И, причем третий вход седьмого элемента И, первьй вход второго элемента И, второй вход второго элемента ИЛИ, второй вход третьего элемента И, второй вход пятого элемента ИЛИ, первый вход шестого элемента ИЛИ, третий вход четвертого триггера, вход первого элемента ИЕ, второй вход четвертого элемента И, второй вход восьмого элемента ИЛИ и второй вход восьмого элемента И являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмы восьмым, девятым, десятым и одиннадцатым входами дешифратора, соответствующими входами которого являются входы элемента депмфрации, а выход четвертого элемента ИЛИ, выход шестого элемента ИЛИ, выход десятого элемента И, второго элемента 4И1-ШИ, выход восьмого элемента ИЛИ, выход первого элемента 2И-И.Г1И, выход седьмого элемента ИЛИ, выход второго элемента 2И-ИЛИ, выход элемента ИЛИ-НЕ, выход четвертого элемента . И, выход четвертого триггера, выход второго элемента И, выход первого элемента 4И-ИЛИ, выход шестого элемента И, выход девятого элемента 1ШИ и выход пятого элемента И являются соотгзетственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым , девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым и шестнадцатым выходами дешифратора.

8..Устройство по п. 1, отличающееся тем, что, блок формирования контрольного кода содер лшт блок элементов И, блок элементов ИЛИ и элемент НЕ, выход которого соединен с первыми входами блока элементов И, вход элемента НЕ соединен с первыми входами блока элементов ИЛИ, npvraeM вход элемента НЕ и вторые входы блоков элементов И и элементов ИЛИ являются соответственно управляющим и cooтвeтcтвyюIUИ ш входами блока формирования контрольного кода, выходами которого являются выходы блоков элементов И и элементов ИЛИ,

9,Устройство по п. 1, отличаю рд 6 е.с я тем, что, блок управления режимами работы содержит два элемента НЕ, двенадцать элементов И, три элемента ИЛИ, двенадцать триггеров и счетчик, выходы которого соединены с входами первого элемента И, выход которого соединен с первым входом первого триггера, второй вход которого соединен с первым входом второго триггера и с выходом первого элемента МИ, первый вход которого соединен с первым входом второго элемента ИЛИ, с первыми входами третьего, четвертого, пятого шестого, седьмого и восьмого триггеpoSjC первым входом второго элемента И и с первым входом третьего элемента И, второй вход которого через

1

04 первый элемент НЕ соединен с вторым

входом второго элемента И, выход которого соединен с первь м входом третьего элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, с первым входом девятого триггера и с первым входом десятого триггера, второй вход которого соединен с вторым входом девя-того триггера и с выходом пятого элемента И, первый вход которого соедииен с выходом второго элемента НЕ, вход которого соединен с первым входом шестого элемента И, второй вход которого соединен с вторым входом пятого элемента И и с первым выходом пятого триггера, второй вход которого соединен с вторым входом шестого триггера, третий вход которого соеди Heii с выходом четвертого триггера, второй вход которого соединен с вторым входом третьего триггера, с первым входом одиннадцатого триггера и с выходом седьмого элемента,И, первый вход которого соединен с первым выходом первого триггера и с вторым входом второго элемента I-fflM, выход которого соединен с первым входом счетчика, второй вход которого соединен с выходом восьмого элемента И, первый вход которого соединен с первым выходом второго триггера, второй -- выход которого соединен с первыми входами девятого, десятого и одиннадцатого элементов И, вторые входы девятого и десятого элементов И подключены к выходу двенадцатого элемеЕ{та И, первый вход которого соединен с первым выходом седьмого триггера и с вторь м входом восьмого триггера, первый выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым входом первого элемента ИЛИ, с втрым входом седьмого триггера и с третьим входом восьмого триггера, второй выход которого соединен с вторым входом одиннадцатого элемента И, второй выход первого триггера соединен с вторым и с третьим входами одиннадцатого триггера, выход которого по ключен к третьему входу третьего триггера, первый и второй выходы которого подключены соответственно к третьему входу четвертого триггера и к третьему входу пятого триггера, третий вход девятого элемента И соединен с выходом десятого триггера и с третьим входом девятого триггеpa, четвертый вход которого соединен с выходом шестого элемента И и с третьим входом десятого триггера, четвертый вход которого соединен с выходом девятого триггера и с третьим входом десятого элемента И, выход третьего элемента И соединен с первы входом двенадцатого триггера, второй вход которого соединен с выходом третьего элемента ИЛИ, второй выход седьмого триггера подключен к третьему входу седьмого триггера, выход двенадцатого триггера соединен с вторым входом двенадцатого элемента И, причем второй вход седьмого элемента И, второй вход третьего элемента И, вход второго элемента НЕ, второй вход пятого триггера, второй вход первого элемента ИЛИ и первый вход второго элемента ИЛИ являются соответственно первым, вторым, третьим, четвертым, пятым, шестым и седьмым входами блока управления режимами работы, первым, вторым, третьим, четвертым, пятым, шестым и седьмым выходами которого являются соответственно выход десятого элемента И, выход девятого элемента И, выход одиннадцатого элемента И, первый выход первого триггера, выход шестого триггера, второй выход пятого триггера и второй выход первого триггера.

10, Устройство по п. 1, отличающееся тем, что блок контроля содержит два элемента ИЛИ, два элемергта И, восемь триггеров и два счетчика, выходы которыгг подключены соответственно к первому и второму входам первого элемента ИЛИ, третий вход которого соединен с выходом первого триггера, первый

вход которого соединен с выходом второго триггера, второй вход которого соединен с выходом восьмого триггера, первый вход которого соеди нен с выходом второго элемента Ш1И, первый вход которого соединен с первым выходом четвертого триггера, второй выход которого соединен с первым входом четвертого триггера, второй вход которого соединен с выходом первого элемента И и с вторым входом третьего триггера, третий вход которого соединен с вторьп ш входами первго и второго триггеров, с первым: входами пятого, шестого и седьмого триггеров и с первым входом первого счетчика, второй вход которого соединен с вторым входом пятого триггера, выход которого соединен с вторым входом шестого триггера, вь0сод которого соединен с четвертым входом первого элемента ИЛИ, пятый вход которого соединен с выходом седьмого триггера, второй вход которого соединен с выходом восьмого триггера, первый вход которого соединен с первым входом второго элемента И, выход которого подключен к первому .входу второго счетчика, второй вход которого соединен с первым входом первого элемента И, второй вход восьмого триггера соединен с третьим входом четвертого триггера, причем второй вход -второго элемента И, первьй вход восьмого триггера, первьп вход первого счетчика, пе.рвый вход первог элемента И, второй вход первого счетчика и второй вход второго элемента И являются соответстверпю первым, вторым, третьим, четвертым, пяты,, (шестым, седьмым и восьмьгл входам блока контроля, выходом которого является выход, второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1131035A1 |

| Многоканальное приоритетное устройство | 1980 |

|

SU896624A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1800481A1 |

| ЭЛЕКТРОННЫЙ РЕНТГЕНОВСКИЙ СПЕКТРОМЕТРИЧЕСКИЙ КАНАЛ | 1999 |

|

RU2157553C1 |

| Формирователь последовательности импульсов | 1980 |

|

SU966871A1 |

| Устройство для отладки и контроля хода программ | 1988 |

|

SU1529227A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1981 |

|

SU999062A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

1. УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДАННЫХ, содержащее блок формирования контрольного сигнала четности, который соединен со сдвиговым регистром, первый вход которого, соединен с первым входом блока контроля четности, второй вход которого соединен с первым выходом блока управления приемо-передачей, второй выход которого соединен с вторым входом сдвигового регистра, соответствую щие выходы которого соединены с соответствующими входами буферного регистра, отличающееся тем, что, с целью повышения достоверности, в него введены блок управления режимами работы, счётчик циклов, дешифратор, блок преобразования код информация, блок преобразования информация - код, три переключателя, блок управления частотой, блок формирования контрольного кода, блок входных переключателей, регистр управления и блок контроля, выход которого соединен с первым входом дешифратора, второй вход которого соединен с первым входом блока управления режимами работы, с первым входом блока управления частотой, с первым входом блока преобразования код информация, с первым входом блока преобразования информация - код и. с первым входом блока контроля, второй вход которого соединен с первым входом регистра управления,; с первым входом первого переключателя, с первым выходом блока управления режимами работы и с третьим входом депшфратора, четвертый вход которого соединен с вторым входом регистра управления и с вторым выходом блока управления режимами работы, третий выход которого соединен с третьим входом блока контроля и с пятым входом дешифратора, шестой вход которого соединен с вторым входом блока преобразования код-информация, с третьим входом регистра управления и с четвертым ВЫХОДОМ блока управления режимами работы, пятый выход которого соединен с четвертым входом регистра управления, пятый вход которого соединен с управляющим входом буферного регистра и с первым выходом дешифратора, второй, третий, четвертьй, пятьш и шестой выходы которого ) ключены к cooтвeтcтвyioщIiм входам бло00 ка управления приемо-передачей, управляющий вход которого соединен с о вторым входом блока преобразования информация - код, с выходом блока управления частотой, с первым вхо-о . дом счетчика цикла, с вторым входом блока управления режимами работы, с четвертым входом блока контроля и с седьмым входом дешифратора, восьмой вход которого соединен с третьим входом блока управления режимами работы, шестой выход которого соединен с вторым входом первого переключателя, выход которого соединен с четвертым входом блока управления

1

Изобретение относится к технике связи и может быть использовано в вычислительных системах для передачи информации по каналам связи

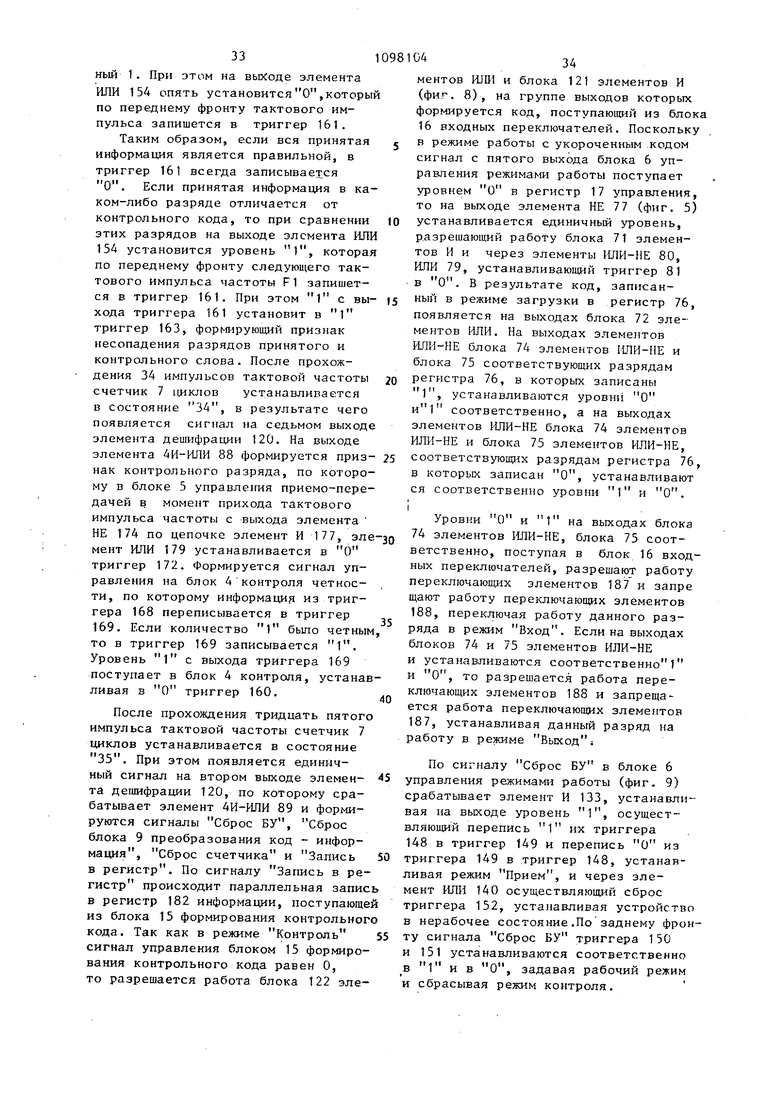

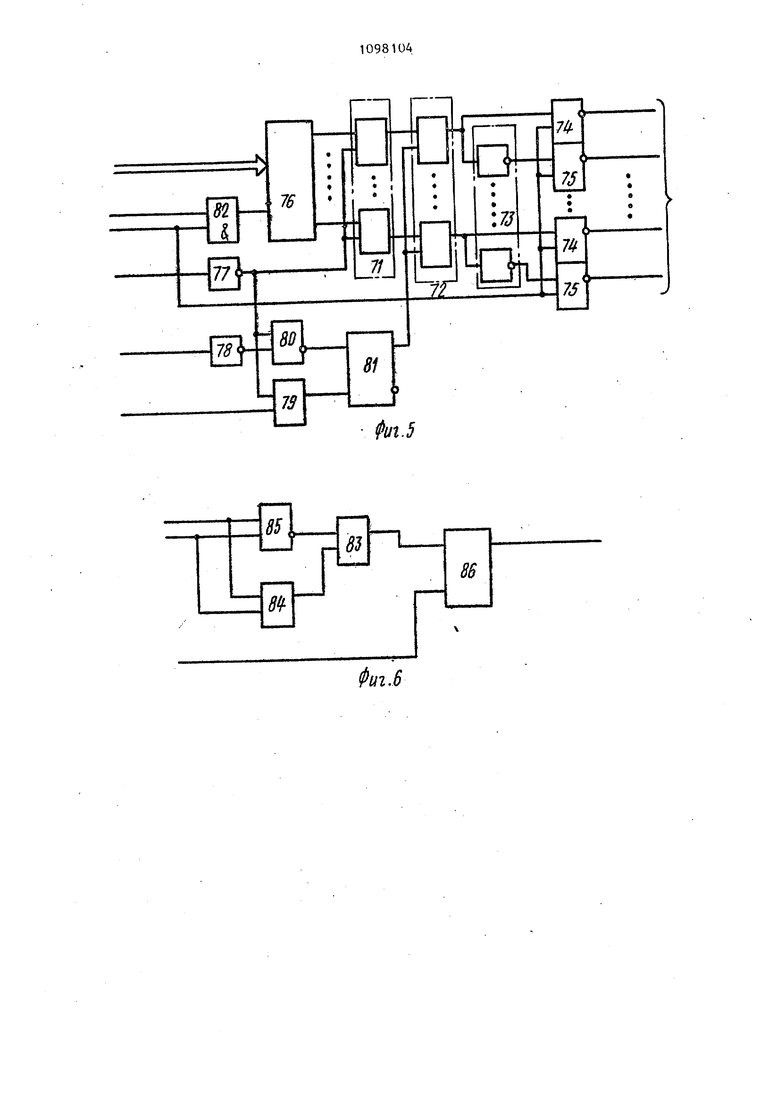

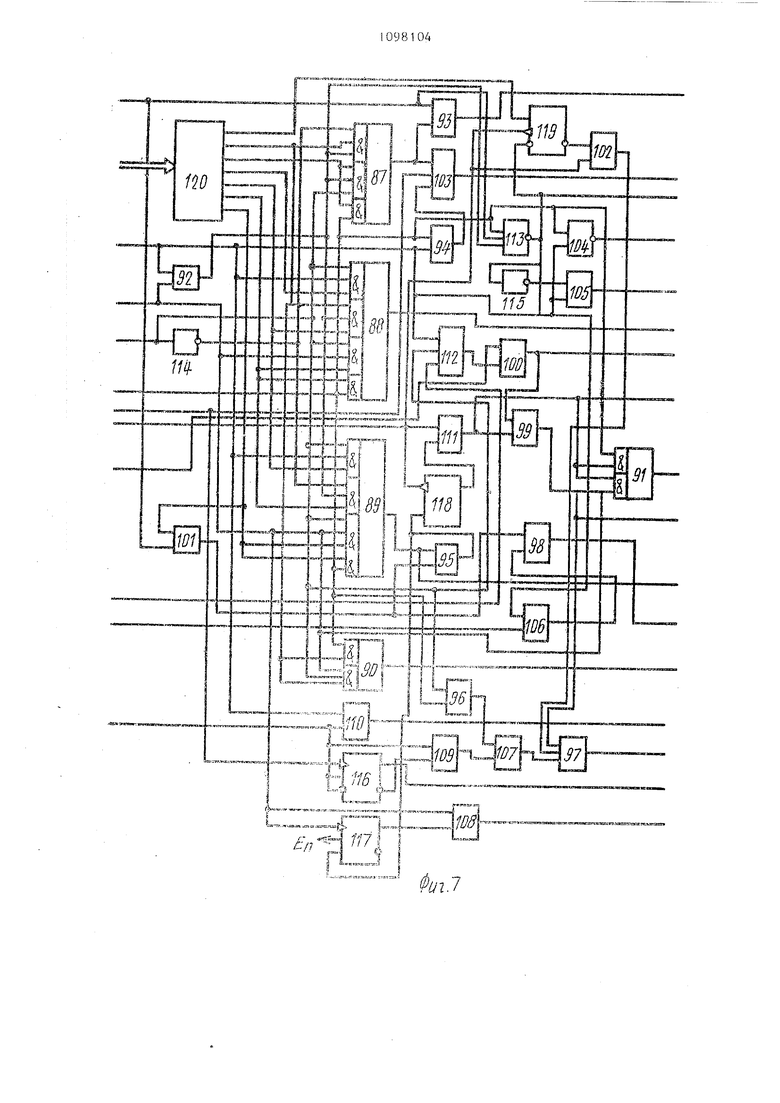

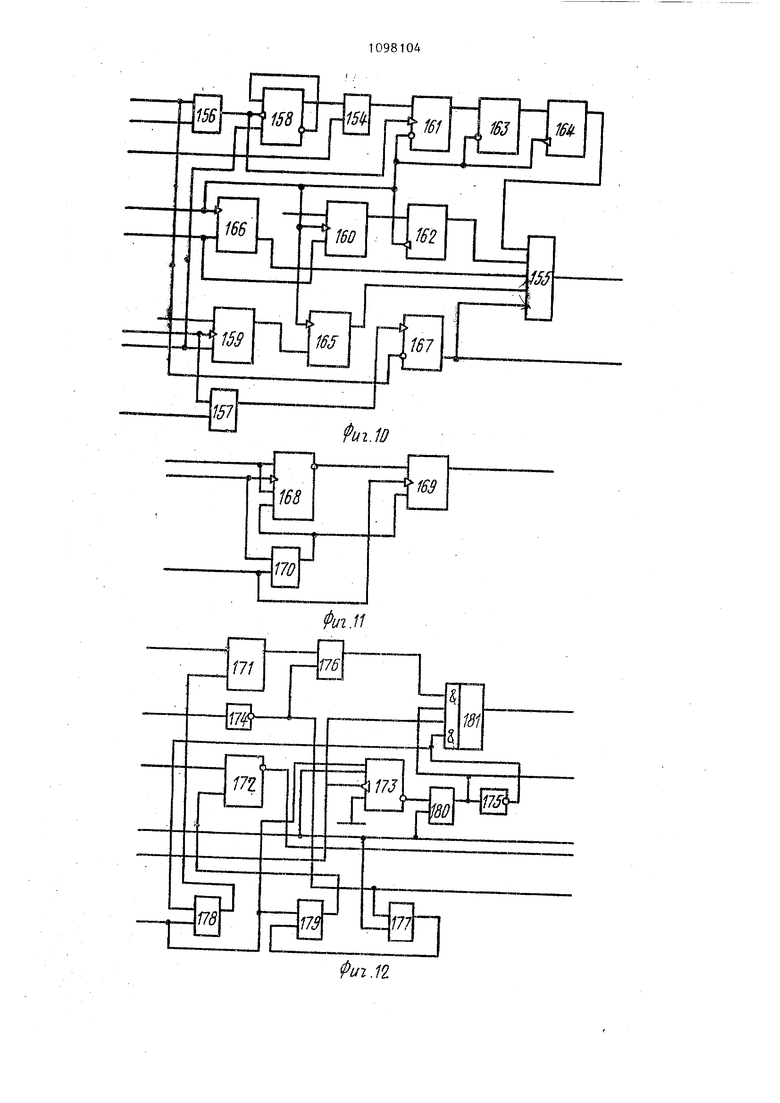

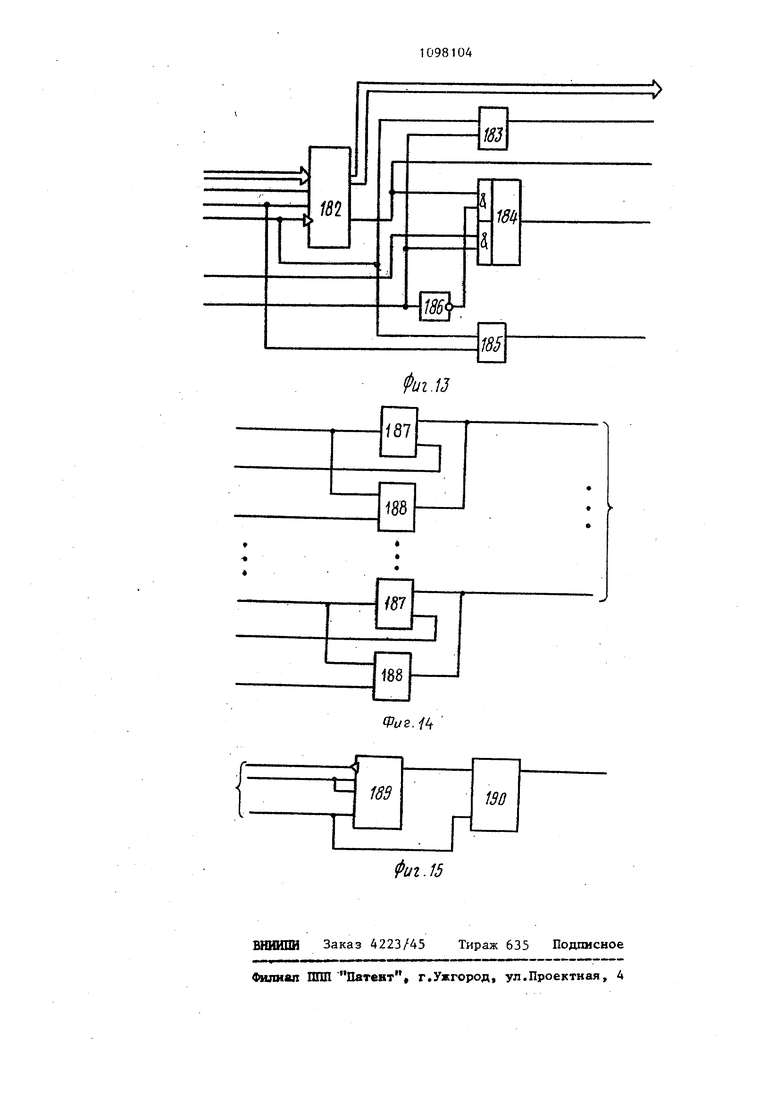

Известно устройство для передачи информации, содержащее сдвиговый регистр, входы которого соединены с магистралью данных , а выход сдвигового регистра подключен к линии связи, счетчик циклов, соединенный с блоком управления, cooтвeтcтвyюш й выход которого соединен с соответствующим входом регистра сдвига 1J. 3 Однако это устройство отличается низкой помехозап ищенностью. Наиболее близким по технической сущности к изобретению является уст ройство для передачи и приема данны содержащее блок формирования контрольного сигнала четкости, который соединен со сдвиговым регистром, пе вый вход которого соединен с первым входом блока контроля четности, вто рой вход которого соединен с первым выходом блока управления приемопередачей, второй выход которого соединен с вторым входом сдвиговог регистра, соответствующие выходы которого соединены с соответствующими входами буферного регистра. Недостатком этого устройства является низкая достоверность переда чи данных. Цель изобретения - повышение достоверности Цель достигается тем ЧТО в устро ство для передачи и приема данных, содержащее блок формирования контрольного сигнала четности, который соединен со сдвиговым регистромj первый вход которого соединен с первым входом блока контроля четности второй вход которого соединен с первым выходом блока управления приемопередачей, второй выход которого соединен со вт, рым входом сдвигового регистра, соотвь-тётвующие выходы которого соединены с соответствующим входами буферного регистра, введены блок управления режимами работы, сче чик циклов, дешифратор, блок преобразования код - информация, блок преобразования информация код, три переключателя, блок управления часто той, блок формирования контрольного кода, блок входных переключателей, регистр управления и блок контроля, выход которого соединен с первым вхо дом дешифратора, второй вход которо соединен с первым входом блока управления режимами работы, с первым входом блока управления частотой, с первым входом блока преобразования код - информагдия, с первым входом блока преобразования информация - ко и с первым входом блока контроля, вт рой вход которого соединен с первым входом регистра управления, с первым входом первого переключателя, с первым выходом блока управлеютя режимами работы и с третьим входом дешифратора, четвертый вход которого 4 соединен с вторым входом регистра управления и с вторым выходом блока управления режимами работы, третий выход которого соединен с третьим входом блока контроля и с пятым входом дешифратора, шестой вход которого соединен с вторым входом блока преобразования код - информация, с третьим входом регистра управления и с четвертым выходом блока управления режимами работы, пятый выход которого соединен с четвертым входом регистра управления, пятый вход которого соединен с управляющим входом буферного регистра и с первым выходом дешифратора, второй, третий, четвертый, пятый и шестой выходы, которого подключены к соответствующим входам блока управления приемо-передачей, управляю11№1й вход которого соединен с вторым входом блока преобразования информация - код, с выходом блока управления частотой, с первым входом счетчика цикла, с вторым входом блока управления режимами работы, с четвертым входом блока контроля и с седьмым входом дешифратора, восьмой вход которого соединен с третьим входом блока управления режимами работы, шестой выход которого соеди ( нен с вторым входом первого переключателя, выход которого соединен с четвертым входом блока управления режимами работы« пятый вход которого соединен с выходом второго переключателя и с третьим входом блока преобразования код - информация, четвертый вход которого соединен с седьмым выходом дешифратора, восьмой выход которого соединен с вторым входом блока управления частотой, третий вход которого соединен с вторым входом счетчика цикла и с девятым выходом дешифратора, десятый выход которого соединен с четвертым входом блока управления частотой, пятый вход которого соединен .с первым выходом блока преобразования код - информация, второй выход которого соединен с девятым входом дешифратора и с пятым входом блока контроля, шестой вход, которого соединен с одиннадцатым выходом дешифратора, двенадцатый выход которого соединен с шестым входом блока управления peжимa ш работы, седьмой вход которого соединен с десятым входом дешифратора, тринадцатый выход которого соединен с первым входом второго переключателя, второй вход которого соединен с седьмым выходом блока управления режимами работы, причем первый вход третьего переключателя соединен с пятым входо блока преобразования код - информа ция и с выходом блока преобразования информация - код, третий вход которо го соединен с дополнительным выходом сдвигового регистра, третий вход которого соединен с третьим выходом блока управления приемо-передачей, четвертый выход которого соединен с третьим входом блока контроля четнос ти, выход которого соединен с одиннадцатым входом дешифратора и с седь мым входом блока контроля, восьмой вход которого соединен с первым вход сдвигового регистра и с третьим выходом блока пре15бразования код - информация, шестой вход которого соеди нен с четырнадцатым выходом дешифратора, пятнадцатый выход которого соединен с третьим входом счетчика цикла, выходы которого подключены к соответствующим входам дешифратора, шестнадцатый выход которого соединен с управляющим входом блока формирования контрольного кода, соответствующие входы которого соединены с 00 ответствующими выходами блока входны переключателей, соответствуюц ие вход которого соединены с выходами буферного регистра и с соответствующими входами регистра управления, управляющие выходы которого подключены к управляющим входам блока входных переключателей, соответствующие выходы блока формирования контрольного кода подключены к соответствующим входам регистра сдвига, четвертый вход кото рого соединен с пятым выходом блока управления приемо-передачей, седьмой вход блока преобразования код - информация соединен с выходом третьего переключателя, второй вход которого соединен с семнадцатым выходом дешиф ратора. Каждый переключатель содержит два усилителя, ключевой элемент, элемент И и элемент НЕ, выход которо го соединен с первым входом элемента И, второй вход которого соединен с выходом первого усилителя, вход которого соединен с первым входом ключевого элемента, второй вход кото рого соединен с выходом второго усилителя, а управляющий вход ключевого элемента соединен с входом элемента НЕ, причем вход первого усилителя, вход второго усилителя и вход элемента НЕ, являются входами переключателя, выходом которого - является выход элемента И. Блок управления частотой содержит три элемента НЕ, два элемента И-НЕ, элемент ИЛИ. два элемента 2И-ИЛИ-НЕ, триггер, элемент И и счетчик, выход которого подключен к соответствующим входам первого элемента 2И-НЛИ-НЕ, выход которого соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с входом первого элемента НЕ, выход которого соединен с первым входом счетчика, второй вход которого соединен с выходом второго, элемента НЕ, вход которого соединен с первым входом триггера, второй вход которого соединен с выходом элемента Иу первый вход которого соединен с выходом второго элемента И-НЕ, первый вход которого соединен с выходом первого элемента И-ИЕ и с первым входом элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента И-НЕ, с вьгходом триггера и с первым- входом второго элемента 2И-ИЛИ-НЕ, второй вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с третьим входом второго элемента 2И-ИЛИ-НЕ, -выход элемента ИЛИ подключен к второму входу элемента И, причем вход второго элемента НЕ, вход первого элемента НЕ, третий вход триггераJвход третьего элемента НЕ и четвертый вход второго элемента 2И-ИЛИ-НЕ являются соответственно первым, вторым, третьим, четвертым .и пятым входам- блока управления частотой, выходом которого является выход второго элемента 2И-Ш1И-НЕ. Блок преобразования код - информация содержит два элемента , восемь элементов-НЕ, семь триггеров, пять элементов И, два элемента И-НЕ, шесть элементов ШШ, четьфе элемента ИЛИ-НЕ, счетчик и элемент 4И-ИЛИ-НЕ, выход которого соединен с первым входом счетчика, второй вход которого соединен с первым входом первого элемента И и с выходом первого элемента НЕ, вход которого соединен с первыми входами первого и второго элементов И-НЕ и с выходом первого элемента ИЛИ-НЕ, первый вход которого соединен с выходом второго элемента ШШ-НЕ, с первыми входами трет его и четвертого элементов ИЛИ-НЕ и с входом второго элемента НЕ, выход которого соединен с первым входом первого триггера, второй вход кото рого соединен с первым выходом второ го триггера и с вторым входом третье го элемента ИЛИ-НЕ, третий вход кото рого соединен с выходом первого элемента 2И-ИЛИ, с первым входом третье го триггера и с входом третьего элемента НЕ, выход которого соединен с первым входом четвертого триггера и с вторым входом четвертого элемента ИЛИ-НЕ, третий вход которого соединен с первым входом пятого триггера с первым выходом первого триггера и с первым входом второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с- первым выходом счетчика и с первым входом четвертог элемента И, второй вход которого соединен с вторым выходом счетчика, третий выход которого соединен с первым входом шестого триггера и с первым входом пятого элемента И, вто рой вход которого соединен с вторым выходом первого триггера и с вторым входом пятого триггера, первьй выход которого соединен с четвертым входом четвертого элемента ИЛИ-НЕ, выход которого соединен с вторым входом первого элемента ИЛИ-НЕ, с первым вх дом второго элемента ИЛИ и с вторым входом первого элемента И, третий вход которого соединен с выходом пер вого элемента И-НЕ, с вторым входом второго элемента И-НЕ, с первым и вт рым входами элемента 4И-ИЛИ-НЕ и с входом четвертого элемента НЕ, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом пятого элемента НЕ и с третьим и четвертым входами элемента 4И-ИЛИ-НЕ,, пятый и шестой входы которого соединены с входом пятого элемента НЕ и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выхо дом шестого элемента НЕ, вход которо го соединен с выходом второго.элемента И-НЕ, с седьмым и восьмым вход ми элемента 4И-ИЛИ-НЕ, с вторым входом первого элемента И-НЕ и с четвертым входом первого элемента И выход которого соединен, с первым входом пятого элемента ИЛИ, выход которого соединен с первым входом второго триггера, второй вход которого соединен с выходом четвертого элемента И, с вторым входом второго элемента И и с третьим входом пятого триггера, второй выход которого соединен с первым входом шестого элемента ИЛИ, второй вход которого соединен с первым выходом четвертого триггера второй выход которого соединен с первым входом второго элемента ШШ-НЕ и с первым входом седьмого триггера, второй вход которого соединен с вторым входом второго элемента ИЛИ-НЕ и с первым выходом третьего триггера, второй выход которого соединен с вторым входом четвертого триггера, третий вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с вторым входом третьего триггера и с выходом первого элемента ИЛИ, третий вход которого соединен с вторым входом пятого элемента ИЛИ и с вторым входом шестого триггера, выход которого соединен с вторым входом третьего элемента И, первый вход первого элемента 2И-ИЛИ соединен с выходом седьмого эле.мента НЕ, вход которого соединен с вторым входом первого элемента 2И-ИЛИ, выход седьмого триггера подключен к первому входу второго элемента 2И-ИЛИ, второй вход которого соединен с выходом восьмого элемента НЕ, вход которого соединен с третьим входом второго элемента 2И-ИЛИ, выход пятого элемента И подключен к четвертому входу первого элемента ИЛИ, пятый вход которого соединен с выходом третьего элемента ИЛИ-НЕ, выход четвертого элемента ИГШ соединен с третьим входом второго элемента И-НЕ, выход третьего элемента ИЛИ подключен к третьему входу первого элемента И-НЕ, выход шестого элемента ИЛИ соединен с третьим BXO-I. дом третьего триггера, причем вход пятого элемента НЕ, вход восьмого элемента НЕ, четвертый вход второго элемента 2И-Ш1И, второй вход пятого элемента ИЛИ, третий, второй и четвертый входы первого элемента 2И-ИЛИ являются соответственно первым, вторым, третьим, четвертым, пятым шестым и седьмым входами блока преобразования код - информа1у1я, первым, вторым и третьим выходами которого являются 910 соответственно выход второго элемен-, та ИЛИ-НЕ, выход шестого триггера и выход второго элемента 2И-ИЛИ. Регистр управления содержит блок элементов И, блок элементов ИЛИ, блок элементов НЕ, первый и второй блоки элементов ИЛИ-НЕ, регистр, два элемента НЕ, элемент ИЛИ, элемент ИЛИ-НЕ триггер и элемент И, выход которого соединен с входом регистра, выходы которого coeдинe ы с первыми входами блока элементов И, выходы которого соединены с первыми входами блока эле ментов ИЛИ, выходы которого соединены с первыми входами первого блока элемё тов ИЛИ-НЕ и с входами блока элементов НЕ,выходы которого соединены с первыми входами второго блока элементов ИЛИ- НЕ, вторые входы которого соединены с вторыми входами первого блока элементов ИЛИ-НЕ и с первым входом элемента И, выход первого элемента НЕ соединен с вторыми входами блока элементов И, с первым входом элементов ИЛИ-НЕ, и с первым входом элемента ИЛИ, выход которого соединен с первым входом триггера, выход которого подключен к вторым входам блока элементов ИЛИ, выход второго элемента НЕ соеди11сн с вторым входом элемента ИЛИ-НЕ, выход которого соединен с вторым входом триггера, причем второй вход элемента ИЛИ, вход второго элемента НЕ, первый вход элемента И, вход первого элемента НЕ, второй вход элемента И и соответствующие вхо ды регистра являются соответственно первым, вторым, третьим, четвертым, пятым и соответствующими входами регистра управления, управляющими выходами которого являются выходы первого и второго блоков элементов ИЛИ-НЕ. Блок преобразования информация код содержит элемент И, элемент ИЛИ, элемент И-НЕ, и триггер, первый вход которого соединен с выходом элемента И, первый вход которого соединен с выходом элемента И-НЕ, входы которого соединены с соответствующими входами элемента ИЛИ, выход которого соеди иен с вторым входом элемента И, причем второй вход триггера и входы элемента ИЛИ являются соответственно первым, вторым и третьим входами блок преобразования информация - код, выхо дом которого является выход триггера. Дешифратор содержит элемент ЗИ-ИЛИ два элемента 4И-ИЛИ, два элемента 2И-ИЛИ, девять элементов ИЛИ, двенад04toдать элементов И, элемент 1ШИ-НК, дпа элемента НЕ, четьфе триггера и элемент дешифрации, первый выход которого соединен с первым входом первого триггера, второй вход, которого соединен с первым входом первого элемента И и с первым входом второго триггера, второй вход которого соединен с выходом первого элемента ИЛИ и с первым входом третьего триггера, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с вторым входом третьего триггера, с первым входом первого элемента 4И-ИПИ, с п-ервым входом первого элемента 2И-ИЛИ, с первым входом второго элемента 2И-ИЛИ, с первым входам второго элемента 4И-ИЛИ и с первым входом второго элемента ИЛИ, второй BXOJDI которого соединен с вторым входом первого элемента 4И-ИЛИ, с вторым входом второго элемента 4И-ШШ, с первым вхо дом третьего элемента ИЛИ, с первым входом четвертого элемента И, с первым входом пятого элемента И, с первым входом шестого элемента И, с первым входом седьмого элемента И и с первым входом восьмого элемента И, выход которого соединен с первым входом четвертого элемента i-ШИ, второй вход которого соединен с первым входом первого элемента ИЛИ и с выходом девятого элемента И, первьм вход которого соединен с третьим и с четвертым входами первого элемента 4И-ШШ и с вторым выходом элемента дешифрации, третий выход которого соединен с первым входом элемента ЗИтИЛИ и с вторым и третьим входами второго элемента 2И-ИЛИ, четвертый вход которого соединен с первым входом пятого элемента ИЛИ, с вторым входом седьмого элемента И, с пятым и шестым вxoдa ш первого элемента 4И-Ш1И, с третьим и четвертым входами второго элемента 4И-11ЛИ, с входом первого элемента НЕ и с вторым входом элемента ЗИ-ИЛИ, третий и четвер- ый входы которого соединены с четвертым выходом элемента дешифрации, пятый выход которого соединен с пятым входом второго элемента 4И-ИЛИ, шестой вход которого соединен с выходом первого элемента НЕ, с пятым входом элемента ЗИ-ИЛИ и с седьмым входом первого элемента 4И-ИЛИ, восьмой вход которого соединен с седьмым входом второго элемента 4И-ИЛИ, с выходом 11 второго элемента ИЛИ, с шестым и седьмым входами элемента ЗИ-ИЛИ и с первым входом элемента ИЛИ-НЕ, вто рой вход которого соединен с вторым входом девятого элемента И и с первы входом шестого элемента ИЛИ, второй вход которого соединен с первым входом десятого элемента И и с выходом элемента ЗИ-ИЛИ, восьмой вход которо го соединен с пятым входом второго элемента 2И-ИЛИ,с вторым дходом пятого элемента ИЛИ, с девятым входом первого элемента 4И-ИЛИ, с вось мым входом второго элемента 4И-ИЛИ, с вторым входом третьего элемента ИЛИ, с третьим входом элемента ИЛИНЕ, с вторым входом пятого элемента И-НЕ и с вторым входом первого элемента 2И-ИЛИ, третий и четвертый вхо ды которого соединены с выходом второго элемента И и с первым входом седьмого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента ИЛИ, первый вход которого соединен с выходом седьмого элемента И, шестой выход элемента дешифрации соединен с девятым входом второго элемента 4И-ИЛИ и с десятым входом первого элемента 4И-ИЛИ, одиннадцатый вход которого соединен с седьмым выходом элемента дешифрадии и с десятым и одиннадцатым входами второго элемента 4И-ИЛИ, выход первого элемента 4И-ИЛИ соединен с вторым входом первого элемента ИЛИ, второй вход четвертого элемента И соединен с первым и вторым входами четвертого триггера и с первым входо одиннадцатого элемента И, второй вход которого соединен с первым выходом четвертого триггера, третий вход которого соединен с вторым входом десятого элемента И, третий вход которого соединен с выходом третьего элемента ИДИ, выход первого тригг ра соединен с вторым входом первого элемента И, выход которого соединен с первым входом девятого элемента ИЛ второй вход которого соединен с выходом двенадцатого элемента И, первы вход которого соединен с выходом пятого элемента RFM, выход седьмого элемента ИЛИ соединен с третьим входом девятого элемента ИЛИ, выход элемент ИЛИ-НЕ соединен с третьим входом первого триггера и с входом второго элемента НЕ, выход которого соединен с вторым входом шестого элемента И., выход второго триггера соединен с 0412 вторым входом второго элемента И, причем третийвход седьмого элемента И, первый вход второго элемента И, второй вход второго элемента ИЛИ, вто рой вход третьего элемента И, второй вход пятого элемента ИЛИ, первый вход шестого элемента ИЛИ, третий вход четвертого триггера, вход первого элемента НЕ, второй вход четвертого элемента И, второй вход восьмого элр.мента ИЛИ и второй вход восьмого элемента И являются соответственно первым, вторым, третьим четвертым пятым, шестым, седьмым, восьмым, девятым, десятым и одиннадцатььм входами деиифратора, соответствующими входами которого являются входы элемен-i та деишфрации, а выход четвертого элемента ИЛИ, выход шестого элемента ИЛИ, выход десятого элемента И, выход второго элемента 4И-ИЛИ5 выход восьмого элемента ИЛИ, выход первого элемента 2И-ЕПИ, выход седьмого элемента ИЛИ, выход второго элемента 2.И-ИЛИ, выход элемента ИЛИ-НЕ, выход четвертого элемента И, четвертого триггера, выход второго элемента И, выход первого элемента 4И-ИЛИ, выход шестого элемента И, выход девятого элемента 1-ШИ и выход пятого элемента И являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым,девятым,десятым,одиннадцатым. двенадцать м, тринадцатым, четырнадцатым, пятнадцатым и шестнадцатым выходами дешифратора. Блок формирования контрольного кода содерлсит блок элементов И, блок элементов ИЛИ и .элемент НЕ, выход которого соединен с первыми входами блока элементов И, вход элемента НЕ соединен с первыми входами блока элементов ИЛИ, причем вход элемента НЕ и вторые входы блоков элементов И и элементов ИЛИ являются соответственно управляющим и соответствующими входами блока формирования контрольного кода, вькодами которого являются выходы блоков элементов И и элементов ИЛМ. Блок управления режимами работы содержит два элемента НЕ, двенадцать элементов И, три элемента ИЛИ, двенадцать триггеров и счетчик, выходы которого соединены с входами первого элемента И, выход которого соединен с первым входом первого триггера 13 второй вход которого соединен с первым входом второго триггера и с выходом первого элемента ИЛИ, первый вход которого соединен с первым входом второго элемента ИЛИ, с первыми входами третьего, четвертого, пятого, шестого, седьмого и восьмого триггеров, с первым входом второго элемента И и с первым входом третьего элемента И, второй вход которого через первый элемент НЕ соединен с вторым входом второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, с первым входом девятого триггера и с первым входом десятого триггера, второй вхо которого соединен с вторым входом девятого триггера и с выходом пятого элемента И, первый вход которого соединен с выходом второго элемента НЕ, -вход которого соединен с первым входом шестого элемента И, второй вход которого соединен с вторым входом пятого элемента И и с первым вых дом пятого триггера, второй вход которого соединен с вторым входом шестого триггера, третий вход которого соединен с выходом четвертого тригге ра, второй вход которого соединен с вторым входом третьего триггера, с первым входом одиннадцатого тригг ра и с выходом седьмого элемента И, первый вход которого соединен с пер вым выходом первого триггера и с вто рым входом второго элемента ИЛИ, выход которого соединен с первым входом счетчика, второй вход которого соединен с выходом восьмого элемента И, первый вход которого соединен с первым вьпсодом второго триггера, второй выход которого соединен с первыми входами девятого, десятого и одиннадцатого элементов И, вторые входы девятого и десятого элементов И подключены к выходу двенадцатого элемента И, первый, вход которого соединен с первым выходом седьмого триггера и с вторым входом восьмого триггера, первый выход которого соединен с первым входом четвертого элемента И, второй вход которого сое динен с вторым входом первого элемен та ИЛИ, с вторым входом седьмого триггера и с третьим входом восьмого триггера, второй выход которого сое динен с вторьм входом одиннадцатого элемента И, второй выход первого триггера соединен с вторым и с третьим входами одиннадцатого триггера, выход которого подключен к третьему входу третьего триггера, первый и второй выходы которого подключены соответственно к третьему входу четвертого триггера и к третьему входу пятого триггера, третий вход девятого элемента И соединен с выходом десятого триггера и с третьим входом девятого триггера, четвертый вход которого соединен с выходом шестого элемента И и с третьим входом десятого триггера, четвертый вход которого соединен с выходом девят ;ого триггера и с третьим входом десятого элемента И, выход третьего элемента И соединен с первым входом двенадцатого триггера, второй вход которого соединен с выходом третьего элемента ИЛИ, второй выход седьмого триггера подключен к третьему входу седьмого триггера выход двенадцатого триггера соединен с вторым входом двенадцатого элемента И, причем второй вход седьмого элемента И, второй вход третьего элемента И, вход второго элемента НЕ, второй вход пятого триггера, второй вход первого элемента ИЛИ и первый вход второго элемента ИЛИ являются соответственно первым, вторым, третьим, четвертым, пятым, шестыми седьмым, входами блока управления режимами работы, первым, вторым,третьим, четвертым, пятым, шестым и седьмым выходами которого являются соответственно выход десятого элемента И,выход девятого элемента И, выход одиннадцатого элемента И, первый выход первсгго триггера, выход шестого триггера, второй выход пятого триггера и |второй Быхрд первого триггера. Блок контроля содержит два элемента ИЛИ, два элемента И,Восемь триггеров и два счетчика, выходы которых подключены соответственно к первому и второму входам первого элемента ИЛИ, третий вход которого соединек . с выходом первого триггера, первый вход которого соединен с выходом второго триггера, второй вход которого соединен с выходом восьмого триггера, первый вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с первым выходом четвертого триггера, второй выход которого соединен с перым входом четвертого триггера, второй вход которого соединен с выходом перво го элемента И и с вторым входом третьего триггера, третий вход которого соединен с вторыми входами первого и второго триггеров, с первыми входами пятого, шестого и седьмого триг геров и с первым входом первого счет чика, второй вход которого соединен с вторым входом пятого триггера, выход которого соединен с вторым входом шестого триггера, выход которого соединен с четвертым входом первого элемента ИЛИ, пятый вход которого соединен с выходом седьмого триггера, второй вход которого соеди ней с вькодом восьмого триггера, первый вход которого соединен с первым входом второго элемента И, выход которого подключен к первому входу второго счетчика, второй вход кото-рого соединен с первым входом первог элемента И, второй вход восьмого триггера соединен с третьим входом четвертого триггера, причем второй вход второго элемента И, первый вход восьмого триггера, первый вход первого счетчика, первый вход первог элемента И, второй вход первого счет чика и второй вход второго элемента И являются соответственно первьм, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами блока контроля, выходом которого является выход второго счетчика. На фиг, 1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 - переключател на фиг. 3 - блок управления частотой на фиг. 4 - блок преобразования код информадия; на фиг. 5 - регистр управления; на фиг. 6 - блок преобразо вания информадия - код; на фиг.. 7 дешифратор; на фиг. 8 - блок формирования контрольного кода; на фиг.9 блок управления режимами работы;, на фиг. 10 блок контроляJ на фиг. 11 блок контроля четности; на фиг. 12 блок управления приемо-передачей; на фиг. 13 сдвиговый регистр; на фиг. 14 - блок входных переключате-, лей; на фиг. 15 блок фop fflpoвaния контрольного сигнала четности. Предложенное устройство для передачи и приема данных содерншт сдви говый регистр 1, блок 2 формирования контрольного сигнала четности, буферный регистр 3, блок 4 контроля штности, блок 5 управления приемо04 16передачей, блок 6 управления режимами работы, счётчик 7 циклов, депшфратор 8, блок 9 преобразования код информащ1я, блок 10 преобразования информация - код, переключатели t1 13, блок 14 и управления частотой, блок 15 формирования контрольного кода, блок 16 входных переключателей, регистр 17 управления, блок 18 контроля. Переключатель содержит усилители 19 и 20 гспшчевой элемент 21, элемент И 22;, элемент НЕ 23. Блок управления частотой содержит элементы НЕ 24-26, элементы И-НЕ 27 и 28, элемент ИЛИ 29, элементы 2И-ИПИ-НЕ 30 и 31, триггер 32, элемент И 33, счетчик 34. Блок преобразования код - информация содержит элементы 2И-ИЛИ 35 и 36f элементы НЕ 37-44, триггеры 45-51, элем.енты И 52-56, элементы И-НЕ 57 и 58, элементы ИЛИ 59-64, элем€;нты ИЛИ-НЕ 65-68, счетчик 69, эЛембшт 4И-Ш1И-НЕ 70. Регистр управления содержит блок 71 элементов И, блок 72 элементов ИЛИ, блок 73 элементов НЕ, блоки 74, 75 элементов Ш1И-НЕ, регистр 76, элементы НЕ 77 и 78, элемент ИЛИ 79, элемент ИЛИ-НЕ 80,,триггер 81, элемент И 82. Блок преобразования информация код содержит элемент И 83, элемент ИЛИ 84, элемент И-НЕ 85, триггер 86. Дешифратор содержит элемент ЗИ-Ш1И 87, элементы 4И-ИЛИ 88 и 89, элементы 2И-ИЛИ 90 и 91, элементы ИЛИ 92 - 100, элементы И 10Т-112, элемент ИЛИ-НЕ 113, элементы НЕ 114 и 115, триггеры 116-119, элементы дешифрации 120. Блок формирования контрольного кода содержит блок 121 элементов И, блок 122 элементов ИЛИ,элемент НЕ 123. Блок управления режимами работы содержит элементы НЕ 124 и 125, элементы И 126-137, элементы ИЛИ 138 140, триггеры 141-152, счетчик 153. , Блок контроля содержит элементы ИЛИ 154 и 155, элементы И 156 и 157 триггеры 158-165, счетчики 166и167. Блок контроля четности содержит триггеры 168 и 169, элемент И 170. Блок управления приемо-передачей содержит триггеры 171-173, элементы НЕ 174 и 175, элементы И 176 и 177, элементы ИЛИ 178-180, элемент 2И-ИЛИ 181. Сдвиговый регистр Содержит ре- , гистр 182, элемент ИЛИ 183, элемент 2И-ИЛИ 184, элемент И 185, элемент НЕ 186. Блок входных переключателей содержит переключающие элементы 187 и 188. Блок формирования контрольного сигнала четности содержит триггеры 189 и 190. Устройство работает следующим образом. После включения питания на устройство поступает сигнал начальной установки. По этому сигналу в блоке 6 управления режимами работы (фиг.9 устанавливаются в единичное состояние триггеры 146, 143 и 150, формируя рабочий режим, устанавливают в О триггер 147, формируя признак работы с внутренней синхронизацией, триггер 144, формируя признак работы С полноразрядным словом, и триг гер 151, сбрасывая режим контроля. Также по сигналу начальной установки через элемент ИЛИ 138 устанавливаются в О триггеры 141 и 142, сбрасывая режим загрузки, через эле мент ИЛИ 139 сбрасывается счетчик 153. Если сигнал Признак старшего поступает на устройство уровнем 1 то в момент появления сигнала начальная установка срабатывает элемент И 131, устанавливая в 1 триг гер 152, определяя рабочее состояние устройства. Если сигнал Призна старшего поступает на устройство уровнем О, то при появлении сигна ла Начальная установка триггер 152 по цепочке элемент НЕ 124, элемент 132, элемент ИЛИ 140 устанавливается в О, определяя нерабочее состо .ние устройства. Триггер 142 устанавливаясь в О перебрасывает триггер 145 в 1, а триггер 147, устанавливаясь в О при наличии (1 состояние) признак Прием/передача на входе устройств приемо-передачи информации через элемент И 130, перебрасывает в О триггер 148 и в 1 триггер.149, оп ределяя режим передачи. Если призна приема/передачи поступает уровнем то по цепи элемент НЕ 125, элемент 129, триггеры 148 и 149 устанавливаются соответственно в 1 и в О определяя режим приема. Таким образом, в результате вы- i . полнения начальной установки устройство устанавливается в режим работы с внешней синхронизацией, с полноразрядными словами. При этом в зависимости от уровней сигналов Прием/ передача и Признак старшего устанавливается режим либо приема, либо передачи, либо рабочее, либо нерабочее состояние устройства. Одновременно по сигналу Начальная установка в дешифраторе 8 (фиг.7), на выходе элемента ИЛИ 100 формируется сигнал Сброс в блок 5 управления приемо-передачей, на выходе элемента ИЛИ 99 формируется сигнал Сброс блока 9 преобразования код информация (фиг. 4) и на выходе эле- мента ИЛИ 97 формируется сигнал Сброс счетчика. По сигналу Сброс в блоке 5 управления приемо-передачей (фиг. 12) устанавливается в О триггер 173 и формируются сигналы на выходах элементов ИЛИ 178 и 179, сбрасывающие соответственно триггеры 171 и 172. Уровень 1 с инверсного выхода триггера 172 поступает на блок 4 контроля четности (фиг. 11) разрешая прохождение тактовых импульсов из блока 14 управления частотой через элемент И 170 на входы установки в О триггеров 168 и 169. Сигнал Сброс устанавливает в О триггер 51 в блоке 9 преобразователя код-информация (фиг, 4), а через элементы ИЛИ 62-64, 61 - триггеры 48, 46, 45. Устанавливаясь в О триггеры 46 и 45 по цепочке элемент ИЛИ-НЕ 67, 68 фop шpyют на выходе последнего уровень О, который на элементах И-НЕ 58, 57, 4И-ИЛИ-НЕ 70, блокирует прохождение тактовой частЬты на счетчик 69. В свою очередь уровень 1 с выхода элемента НЕ 42 устанавливает счетчик 69 в О. Уровень 1 с инверсного выхода триггера 48 устанавливает в О триггер 49, с инверсного выхода которого уровень Г устанавливает в О триггер 50. Таким образом, весь блок 9 преобразования код - информация устанавливается в исходное состояние. Сигнал уровнем О с выхода триггера 51 поступает в дешифратор 8 (фиг. 7) и блок 18 контроля (фиг. 19 1C), устанавливая в О триггеры 116 и 158 соответственно. По сигналу Сброс счетчика устанавливается, в О счетчик 7 1диклов, по которому элемент дешифрации 120 (фиг 7) формирует сигнал 1, посту пающий на триггер 119 и устанавлива щий его в О по заднему фронту тактовой частоты. Вследствие того, что на остальных выходах элемента дешифрации 120 присутствуют зфовни О на выходе элемента 4И-ИЛИ 89 вырабат вается сигнал о, поступающий через элемент ИЛИ 95 на триггеры 1I7 и 118, которые по заднему фронту тактовой частоты устанавливаются в О На этом заканчивается этап начальной установки устройства, за ни следует выполнить этап загрузки, на котором устанавливается режим, в котором будет работать устройство,Существует четыре основных режима работы: с внешней синхронизацией с полноразрядными словами; с внешней синхронизацией с укороченными словами; с внутренней синхронизацией с полноразрядными словами; с внутренней синхронизацией с укороченными словами. При работе устройства с внешней синхронизацией ци1спы передачи и при ема информации задаются извне призна ком Прием-передача. При внутренней синхронизации циклы передачи и приема следуют поочередно один за другим. Цикл передачи или приема, с которого начинается работа устройства, устанавливается по сигналу начальной установки и оп ределяется признаком Прием-передаПри работе с полноразрядными сло вами устройство принимает и передает 32 бита информации. В случае если устройство работает с укороченными словами, то оно передает |vi разрядов информации и ,принимает (32-N) разрядов инфор1мации. При этом количество передавае мых разрядов информации и их нахождение в слове задается на этапе загрузки. Загрузочное слово, поступающее на устройство для приема и передачи данных содержит 34 разряда. Первый разряд определяет режим синхронизации работы устройства: 1 - внутренняя синхронизация.,- О - внешняя 10Д20 синхронизация. Второй разряд определяет формат передаваемого слова: О - полноразрядное слово; 1 укороченное слово. Разряды 3-34 В1шючительно определяют передаваемые (1) или принимаемые (О) разряды при работе с укороченными словами. Для включениярежима загрузки необходимо подать сигнал Загрузка.При этом устанавливается в 1 триггер 141 в блоке 6 управления режимами работы (фиг.9), блокируя на элементах И 135 - 137 прохождение признаков Передача, Прием, Контроль. Одновременно в дешифраторе 8 признак рабочего режима на выходе элемента ИЛИ 92 устанавливается в О и на выходе элемента ИЛИ-НЕ 113 формируется (уров нем 1) признак нерабочего состоя ния устройства. По заднему фронту импульса тактовой частоты триггер 119 устанавливается в О, разрешая прохождение тактовой частоты по цепи элемент И 102, элемент ИЛИ 97 на сброс счетчика 7 циклов. Так же признак нерабочего состояния запрещает работу счетчика, в блоке 14 управления частотой устанавливает в О триггер 3-2. Б блоке 6 управления режимами работы сигнал с прямого выхода триггера 141 разрешает прохождение тактовой частоты через элемент И 126 на вход счетчика 153. После прохождения трех импульсов тактовой частоты срабатывает элемент И 127, устанавливая в 1, триггер 142, формирующий признак режима загрузки. Таким образом счетчик 153 осуществляет задержку формирования признака режима загрузки на три периода тактовой частоты по отношению к сигналу Загрузка, поступающему извне, что необходимо для установки счетчика 7 циклов в О, если в момент подачи сигнала Загрузка устройство находилось в рабочем состоянии . По сигналу с блока 6 управления ре.жимами работы в дешифраторе 8 на выходе элемента ИЛИ 93 формируется сигнал, поступающий в блок 5 управления приемо-передачей (фиг. 12) и устанавливающий в 1 триггер 171., Сигнал с выхода триггера 171 разрешает прохождение тактовых импульсов с блока 14 управления частотой через элемент И 176 и далее через элемент 2И-ИЛИ 181 на сдвиговый регистр 1.

Так же по сигналу загрузка в дешифраторе 8 сбрасывается признак нерабочего состояния устройства, разрешая тем самым работу счетчика 7 циклов и триггера 32 в блоке 14 управления частотой, в режиме Загрузка сигнал (уровнем О) с инверсного выхода триггера 142 поступает на магистральный переключатель 13, запрещая прохождение информации из устройства через ключевой элемент 21, и через элемент НЕ 23, разрешая прохождение информации от внешнего устройства через усилитель 19 и элемент И 22.

Кроме того, сигнал Загрузка разрешает прохождение информации, поступающей с магистрального переключателя 13, через элемент .2И-Ш1И 36, блоки 9 преобразования код - информация на сдвиговый регистр 1, раэрешает прохождение информации через элемент И 82 регистра 17 управления (фиг. 5) и формирует на выходе блока 74 элементов ИЛИ-НЕ и блока 75 элементов ИЛИ-НЕ (уровнем О) сигналы управления блоком 76 входных переключателей, запрещая тем самым прохождение информации через переключаюи(ие элементы 187 и 188..

Уровень О с инверсного выхода триггера 142 поступает также на триггер 145, разрешая его установку О. Уровень 1 с прямого выхода триггера 142 поступает на элемент И 128, разрешая прохождение через него тактовой частоты из блока 14 управления частотой, и через элемент И 134 на сброс счетчика 153. По заднему фронту тактовой частоты триггер 145 устанавливается в О. Кроме того, тактовая частота, пройдя через элемент И 128, поступает на выход устройства для синхронизации подачи входной информации. Смена разрядоввходной информации происходит по заднему фронту тактовой частоты. По переднему фронту второго импульса тактовой частоты устанавливается в О триггер 146. По положительному перепаду, возникающему на инверсном выходе триггера 146, осуществляется запись первого разряда информации, поступающей с переключателя 13 .на триггер 147, если устройство работает в режиме с внешней синхронизацией, то триггер 147 устанавливается в О, разрешая работу элементов и И 130 и И 129 и формируя сигнал уровнем О, разрешающий прохождение признака Прием-передача через переключатель 12. Если устройство работает в режиме Передача признак , Прием-передача поступает уровнем 1, устанавливая через элемент И 130 триггер 148 в О, а триггер 149 в Г

определяя режим . Передача. Если признак Прием-передача поступает уровнем О, то по цепи элемент НЕ 125, И 129 триггер

148устанавливается в 1, а триггер 149 в О,определяя режим Прием.

При работе устройства с внутренней синхронизацией триггер 147 устанавливается в 1, запрещая работу элементов И 130 и И 129, и формирует сигнал 1, разрешающий прохождение признака режима работы из устройства через магистральный переключатель 12 на внешние устройства. Вследствие того, что работа элементов И 130 и И 129 запрещена, триггеры 148 и

149начинают работать в режиме коль цевого регистра, переписывая друг 6 друга 1, записанную в один из

них на этапе начальной установки. При этом устройство работает поочередно в режиме приема и передачи. По третьему тактовому импульсу осуществляется запись О в триггер 143 и аналогично описанному запись второго разряда информации в триггер 144. При этом в случае работы с полноразрядными словами в триггер 144 записывается О, формируя уровнем 1 сигнал на регистр 17 управления. Сигнал через элемент НЕ 77 запрещает работу блока 71 элементов И, блоки|руя прохождение через нее информации с регистра 76, и разрешает работу элементов ИЛИ-НЕ 80 и ИЛИ 79, позволяя в зависимости от режима приема или передачи устанавливать триггер 81 в 1 или О.

При работе с укороченным словом триггер 144 устанавливается в 1, формируя сигнал управления уровнем О. По этому сигналу через элементНЕ 77 разрешается работа блока 71 элементов И и через элемент ИЛИ 79 устанавливается в О триггер 81.