(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство для управления оперативной динамической памятью | 1985 |

|

SU1251174A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Устройство для ввода информации | 1988 |

|

SU1580339A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Запоминающее устройство | 1985 |

|

SU1256096A1 |

| Устройство для регенерации информации динамической памяти | 1988 |

|

SU1635213A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения полупроводниковых запоминающих устройств на микросхемах динамической памяти. Устройство управления динамической памятью содержит генератор импульсов регенерации, генератор тактовых импульсов, шесть D-триггеров, семь элементов 2 И-НЕ, элемент 3 И, три инвертора, восьмой, девятый, десятый и одиннадцатый элементы 2 И-НЕ, регистр сдвига, два элемента 2 И, двоичный счетчик, мультиплексор, элемент 3 И-НЕ, дешифратор синхросигнала столбца, элемент 4 И-НЕ, шинный приемопередатчик и четвертый инвертор. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано для построения полупроводниковых запоминающих устройств на микросхемах динамической памяти.

Цель изобретения - повышение надежности и упрощение устройства.

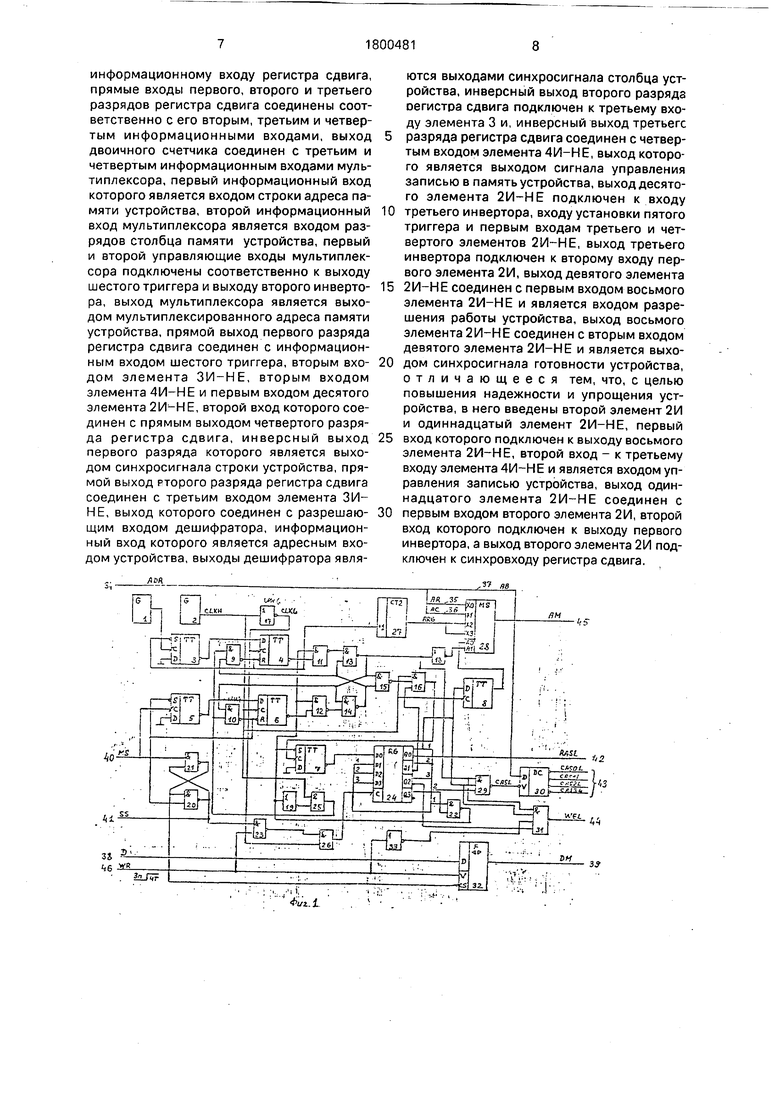

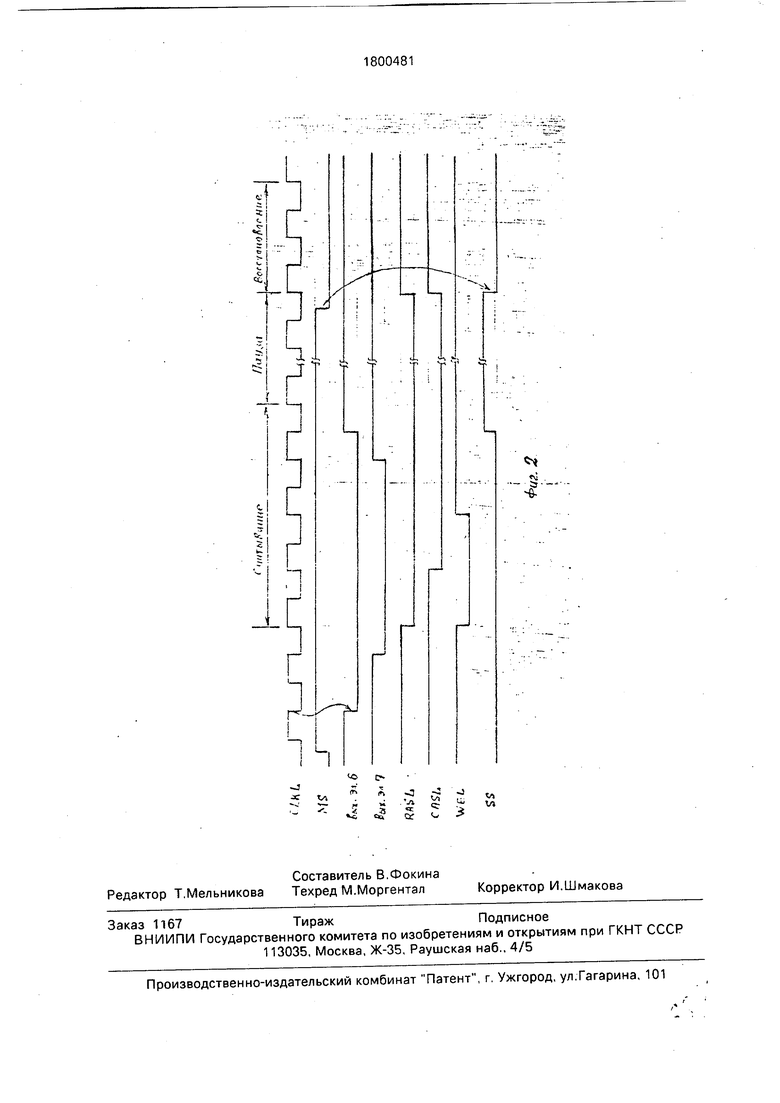

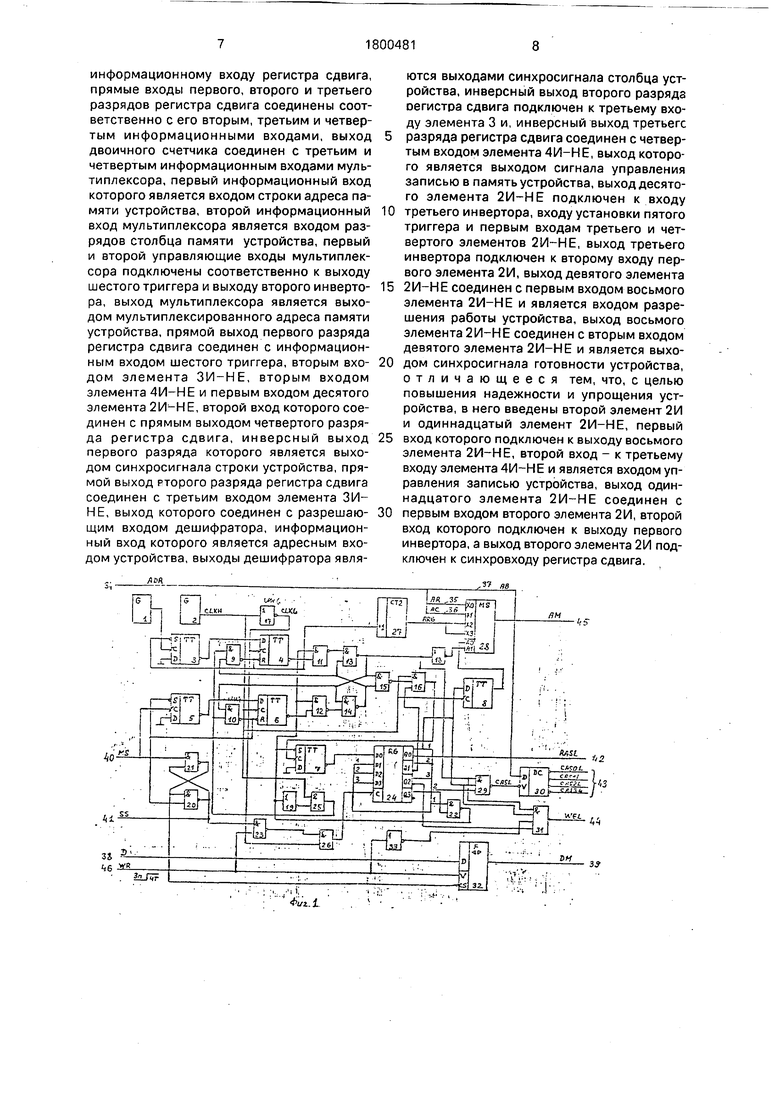

На фиг.1 показана принципиальная электрическая схема предлагаемого устройства; на фиг.2 - временные диаграммы его работы.

Устройство управления динамической памятью содержит (фиг.1) генератор 1 импульсов регенерации, генератор 2 тактовых импульсов, первый 3, второй 4, третий 5, четвертый 6, пятый 7 и шестой 8 D-триггеры, первый 9, второй 10, третий 11, четвертый 12, пятый 13, шестой 14 и седьмой 15 элементы 2VI-HE, элемент ЗИ 16, первый 17, второй 18 и третий 19 инверторы, восьмой 20, девятый 21, десятый 22 и одиннадцатый 23 элементы 2И-НЕ, регистр сдвига 24, первый 25 и второй 26 элементы 2И, двоичный счетчик 27, мультиплексор 28, элемент ЗИНЕ 29, дешифратор синхросигнала столбца 30, элемент 4И-НЕ 31, шинный приемопередатчик 32 и четвертый инвертор 33.

Адрес обращения в память ADR поступает на инверсный вход 34 устройства. При этом разряды ADR разделяются на разряды адреса строки AR 35, разряды адреса столбца АС 36 и разряды выбора банка АВ 37, которые поступают на соответствующие входы мультиплексора 28 и дешифратора 30. Данные D, которыми источник обращения обменивается с памятью, поступают на вход 38 устройства. Соответственно данные DM, которыми память обменивается с источником обращения, поступают на выход 39 устройства.

Сигнал обращения в память MS поступает на вход обращения в память 40 устройства.

00

о о

00

Синхросигнал готовности памяти SS поступает на выход 41 устройства. Кроме того, устройство вырабатывает синхросигнал строки RASL, поступающий на выход 42, синхросигналы столбца CASOL- CAS3L,поступающие на выходы 43, и сигнал управления записью в память WEL, поступающий на выход 44. Мультиплексированный адрес AM подается в память через выход мультиплексированного адреса памяти 45 устройства. Сигнал записи в память WR поступает на вход управления записью 46 устройства.

Предлагаемое устройство управления динамической памятью работает следующим образом.

В любой момент времени устройство может находиться в одном из трех состояний: ожидания, регенерации, памяти и обслуживания обращения в память.

В состоянии ожидания на входы устройства управляющие сигналы не подаются. Триггеры 3, 5, 47 установлены в 1, триггеры 4, 6, 48 сброшены в О. При этом устройство не выдает в память никаких синхросигналов, а приемопередатчик 32 отключен.

Регенерация памяти в устройстве инициируется по положительному фронту сигнала с выхода генератора 1. Этот сигнал сбрасывает триггер 3 в О. Сигнал 1 с инверсного выхода триггера 3 поступает на информационный вход триггера 4. Положительный фронт очередного тактового сигнала CLKL запишет в триггер 4 1. Если в этот момент нет состояния обращения в память, т.е. устройство находится в пассивном состоянии и на выходе элемента 2И-НЕ 12 сигнал 1, то триггер режима, образуемый элементами 2И-НЕ 13 и 14, принимает состояние регенерация и на выходе элемента 13 устанавливается сигнал О. Этот сигнал после инвертирования в инверторе 18 поступает на второй управляющий вход мультиплексора 28 и устанавливает мультиплексор на передачу адреса регенерации с выхода двоичного счетчика 27 на выход 45 мультиплексированного адреса AM. Кроме того, сигнал О с выхода элемента 13 вызывает появление 1 на выходе элемента 2И- НЕ 15. Поэтому положительным фронтом очередного тактового сигнала CLKH с выхода генератора 2 через элемент ЗИ 16 устанавливается в О триггер 7. Положительный фронт очередного синхросигнала CLKL через элемент 2И 26 записывает 1 в первый разряд регистра сдвига 24, а последующие синхросигналы последовательно записывают 1 в старшие разряды регистра. Сигнал с инверсного выхода первого разряда регистра подается на выход 42 как синхросигнал

строки RASL и вместе с адресом AM регенерируемой строки на выходе 41 осуществляет регенерацию строки с номером, содержащимся в счетчике 27, во всех микросхемах памяти. При этом синхросигналы столбца CAS не вырабатываются вследствие запрета сигналом О на первом входе элемента ЗИ-НЕ 29, а приемопередатчик 32 остается отключенным. Через четыре такта сигнала

CLKL сигнал 1 с прямого выхода четвертого разряда регистра 24 вызывает появление сигнала О на выходе элемента 2И-НЕ 22. Этот сигнал О устанавливает триггер 7 в 1 и через инвертор 19 и элемент 2И 25

5 подает сигнал 1 на элементы 2И-НЕ 9 и 10. В результате на выходе элемента 2И-НЕ 9 устанавливается О, а триггер 3 - в 1. Очередной тактовый сигнал CLKL записывает О в первый разряд регистра 24, снимая

0 синхросигнал строки RASL. Вместе с тем обслуживание следующего запроса (обращение в память) возможно лишь после появления сигнала 1 на инверсном выходе второго разряда регистра сдвига 24, посту5 пающего на третий вход элемента ЗИ 16, Этим обеспечивается требуемое время под- заряда ячеек регенерируемых строк микросхем памяти.

Сигнал запроса на обслуживание обра0 щения в память MS поступает на вход 40 устройства и сбрасывает триггер 5 в О. Положительный фронт тактового импульса CLKL записывает 1 в триггер 4. Если в данный момент нет обслуживания регене5 рации, то триггер состояния, образуемый элементами 2И-НЕ 13 и 14, устанавливается в состояние обслуживания обращения в память, и на выходе элемента 14 будет сигнал О, а элемента 13 - 1. Сигнал 1 с

0 выхода элемента 13 поступает через инвертор 18 на второй управляющий вход мульти- плексора 28 и определяет выбор мультиплексором первого и второго информационных входов. При этом в триггере 8

5 записан О.

Поэтому на выход 45 мультиплексированного адреса AM поступает адрес строки AR с первого входа мультиплексора 28. Сигнал О с выхода элемента 2И-НЕ 14 уста0 навливает 1 на выходе элемента 2И-НЕ 15. Поэтому положительный фронт тактового сигнала CLKH запишет 1 в первый разряд регистра 24 и вызовет появление синхросигнала строки RASL. После записи

5 1 в первый разряд регистра 24 очередной синхросигнал CLKH запишет 1 в триггер 8, что вызовет переключение мультиплексора 28 и подачу на выход 45 кода адреса столбца АС со второго входа мультиплексора. После записи 1 во второй разряд регистра 24 на

выходе элемента ЗИ-НЕ 29 появляется сигнал О, который разрешает работу дешифратора 30. На одном из его выходов, соответствующем коду адреса выбора банка АВ 37 на информационном входе дешиф- ратора, появляется синхросигнал столбца CAS09-CAS3L. Одновременно с сигналом RASLna выходе элемента 4И-НЕ 31 появляется сигнал управления записью WEL, если осуществляется операция записи в память и на входе 46установлен сигнал WR, равный 1. Сигнал WEL подается до момента записи 1 в третий разряд регистра сдвига 24, т.е. в течение двух тактов. При записи 1 в четвертый разряд регистра 24 сигнал О с выхода элемента 2И-НЕ 22 устанавливает триггер 7 в 1, а положительный фронт CLKH через элемент 2И 25 сбрасывает триггер 6 в О и устанавливает триггер 5 в 1. Одновременно на выходе триггера, образу- емого элементами 2И-НЕ 20 и 21, устанавливается сигнал 1 готовности памяти SS. Если осуществляется операция чтения данных, то сигнал WR равен 1 и на выходе элемента 2И-НЕ 23 появляется О, который блокирует на первом входе элемента 2И 26 тактовый сигнал CLKL Поэтому сдвиг регистра 24 приостанавливается и возникает пауза (фиг.2), длительность которой зависит от того, как скоро источник запроса принимает считываемую информацию. Во время паузы установлены синхросигналы RAS и CAS, а данные через приемопередатчик 32 передаются с выхода 39 на вход 46. После приема данных источник запроса устанавливает MS в О, сбрасывая триггер на 2И-НЕ 20 и 21. Сигнал SS переходит в О, отключая приемопередатчик 32, а сигнал 1 с выхода элемента 2И-НЕ 23 разрешает прохождение импульсов CLKL через элемент 26. Поэ- тому очередной импульс CLKL запишет О в первый разряд регистра 24, сбрасывая синхросигналы RAS и CAS. Далее, аналогично операции регенерации, формируется задержка для подзаряда ячеек строки, к которой было обращение, после чего устройство переходит в состояние ожидания и готово к приему запросов на очередное обращение в память или регенерацию. При выполнении операции записи сигнал имеет значение О и на выходе элемента 2И-НЕ 23 всегда 1. Поэтому пауза отсутствует.

Таким образом, в предлагаемом техническом решении за счет введения паузы и сохранения синхросигналов строки и столб- ца считываемые данные удерживаются на выходе микросхем динамической памяти до тех пор, пока источник запроса обращения в память не сообщит об окончании приема информации. Это позволяет исключить использование регистра для считываемой информации, а следовательно, уменьшить объем аппаратуры и повысить надежность устройства.

Устройство может быть выполнено на микросхемах ТТЛ-серий К555, К 155 и др. В памяти, управляемой предлагаемым устройством, могут быть использованы микросхемы К565РУ5, М565РУ7 и др.

Формула изобретения Устройство для управления динамической памятью, содержащее генератор импульсов регенерации, генератор тактовых импульсов, с первого по шестой триггеры, с первого по десятый элементы 2И-НЕ, элемент ЗИ, регистр сдвига, первый элемент 2И, двоичный счетчик, мультиплексор, элемент ЗИ-НЕ, дешифратор, три инвертора, элемент 4И-НЕ, причем выход генератора импульсов регенерации подключен к синх- ровходу первого триггера, выход генератора текстовых импульсов подключен к входу первого инвертора, синхровходам четвертого и шестого триггеров, первому входу элемента ЗИ и первому входу первого элемента 2И, выход первого инвертора подключен к синхровходу второго триггера, информационный вход которого соединен .с выходом первого триггера, вход установки которого соединен с выходом первого элемента 2И- НЕ, с входом сброса второго триггера и подключен к счетному входу двоичного счетчика, выход второго триггера соединен с первым входом третьего элемента 2И-НЕ, выход которого соединен с первым входом пятого элемента 2И-НЕ, выход которого соединен с входом второго инвертора, первыми входами второго, шестого и седьмого элементов 2И-НЕ и элемента ЗИ-НЕ, синх- ровход третьего триггера соединен с первым входом девятого элемента 2И-НЕ и является входом обращения устройства, вход установки третьего триггера соединен с выходом второго элемента 2И-НЕ, входом сброса четвертого триггера и вторым входом восьмого элемента 2И-НЕ, выход третьего триггера соединен с информационным входом четвертого триггера, выход которого подключен к второму входу четвертого элемента 2И-НЕ, выход которого подключен к второму входу шестого элемента 2И-НЕ, выход которого подключен к вторым входам первого, пятого и седьмого элементов 2И- НЕ, второй вход второго и первый вход первого элементов 2И-НЕ объединены и подключены к выходу первого элемента 2И, выход седьмого элемента 2И-НЕ соединен с вторым входом элемента ЗИ, выход которого соединен с синхровходом пятого триггера, выход которого подключен к первому

информационному входу регистра сдвига, прямые входы первого, второго и третьего разрядов регистра сдвига соединены соответственно с его вторым, третьим и четвертым информационными входами, выход двоичного счетчика соединен с третьим и четвертым информационным входами мультиплексора, первый информационный вход которого является входом строки адреса памяти устройства, второй информационный вход мультиплексора является входом разрядов столбца памяти устройства, первый и второй управляющие входы мультиплексора подключены соответственно к выходу шестого триггера и выходу второго инверто- ра, выход мультиплексора является выходом мультиплексированного адреса памяти устройства, прямой выход первого разряда регистра сдвига соединен с информационным входом шестого триггера, вторым вхо- дом элемента ЗИ-НЕ, вторым входом элемента 4И-НЕ и первым входом десятого элемента , второй вход которого соединен с прямым выходом четвертого разряда регистра сдвига, инверсный выход первого разряда которого является выходом синхросигнала строки устройства, прямой выход второго разряда регистра сдвига соединен с третьим входом элемента ЗИНЕ, выход которого соединен с разрешаю- щим входом дешифратора, информационный вход которого является адресным входом устройства, выходы дешифратора являются выходами синхросигнала столбца устройства, инверсный выход второго разряда оегистра сдвига подключен к третьему входу элемента 3 и, инверсный выход третьего разряда регистра сдвига соединен с четвертым входом элемента 4И-НЕ, выход которого является выходом сигнала управления записью в память устройства, выход десятого элемента 2И-НЕ подключен к входу третьего инвертора, входу установки пятого триггера и первым входам третьего и четвертого элементов 2И-НЕ, выход третьего инвертора подключен к второму входу первого элемента 2И, выход девятого элемента 2И-НЕ соединен с первым входом восьмого элемента 2И-НЕ и является входом разрешения работы устройства, выход восьмого элемента 2 И-НЕ соединен с вторым входом девятого элемента 2И-НЕ и является выходом синхросигнала готовности устройства, отличающееся тем, что, с целью повышения надежности и упрощения устройства, в него введены второй элемент 2И и одиннадцатый элемент 2И-НЕ, первый вход которого подключен к выходу восьмого элемента 2И-НЕ, второй вход - к третьему входу элемента 4И-НЕ и является входом управления записью устройства, выход одиннадцатого элемента 2И-НЕ соединен с первым входом второго элемента 2И, второй вход которого подключен к выходу первого инвертора, а выход второго элемента 2И подключен к синхровходу регистра сдвига.

| Микропроцессорные средства и системы | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Фальцовая черепица | 0 |

|

SU75A1 |

| Микропроцессорные средства и системы | |||

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1993-03-07—Публикация

1990-12-14—Подача