1

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах,содержаадих несколько активных источников информации, подключенных к устройству общего пользования, например общей памяти.

Известно устройство приоритетного подключения процессоров к общей магистрали содержащее блок формирования разрешений и блок маскирования, элементы И-НЕ и лок управления l3

Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство, содержащее два регистра, счетчик, дешифратор, элемент И, триггер,каналы, а в каждом канале - элементы ИЛИ, ИЛИ-НЕ, 2И-ИЛИ.

Недостатком таких устройств является низкое быстродействие.

Цель -изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в многоканальное приоритетное устройство, содержащее входной и выходной регистры, счетчик, дешифратор, элемент задержки, триггер, элемент И, элемент ИЛИ-НЕ, три канала, каждый из которых содержит элемент ИЛИ, элемент ИЛИ-НЕ и элемент 2И-ИЛИ,причем выходы элементов ИЛИ и ИЛИ-НЕ каждого канала соединены соответственно с первыми входами элемента 2И-ИЛИ своего канала, выходы элементов 2И-ИЛИ каналов соединены с соответствующими информационными входами счетчика, тактовый вход счетчика че10рез элемент задержки соединен с первым тактовым входом устройства и тактовьпл входом входного регистра, выход триггера соединен с первым управляющим входом счетчика, группа

15 выходов счетчика соединена с группой информационных выходов дешифратора, управляющий вход дешифратора соединен с выходом элемента И, нулевой вход триггера и первый вход эле20мента И соединены со вторым тактовым входом устройства, тактовый вход триггера и второй вход элемента И соединены с выходом элемента ИЛИ-НЕ, единичный вход триггера сое25динен со входом логической единицы устройства, группа выходов дешифратора соединена с группой управляющих входов выходного регистра, с первого по четвертый и с пятого по

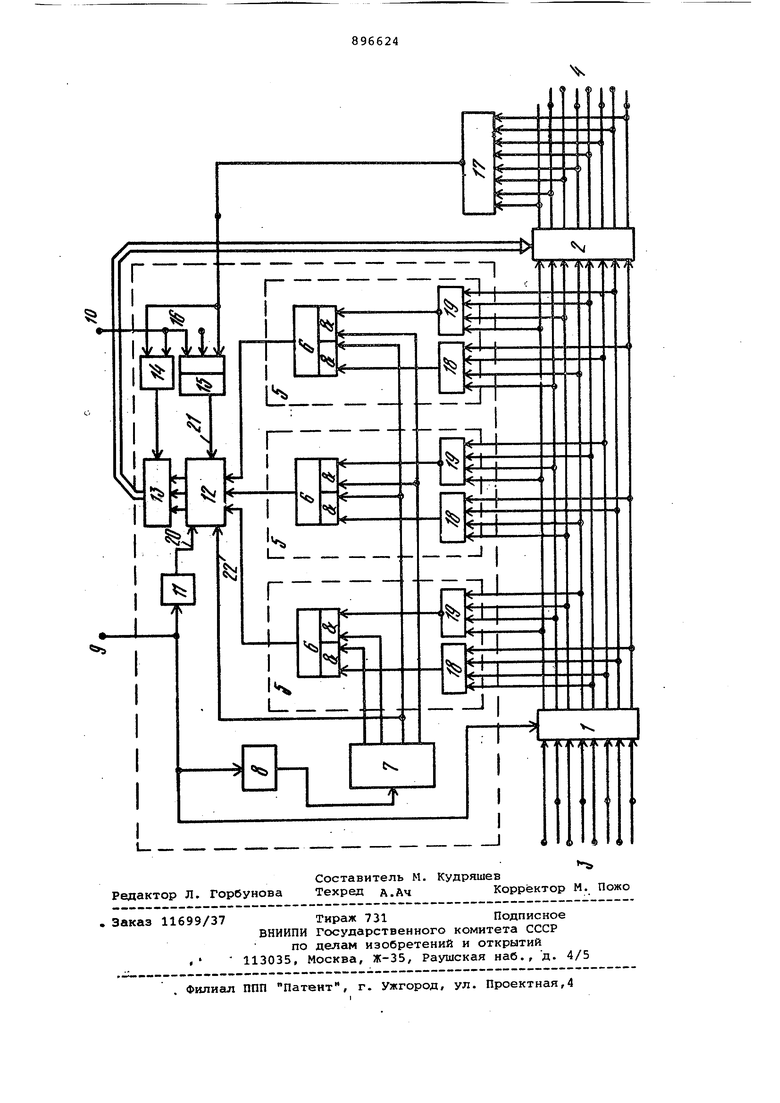

30 восьмой разрядные выходы группы выходов входного регистра соединены соответственно с группами входов элементов ИЛИ и ИЛИ-НЕ первого канала, первый,. второй, пятый, шестой и третий, четвертый, седьмой, восьмой разрядные выходы группы разрядных выходов входного регистра соединены соответственно с группами входов элементов ИЛИ и ИЛИ-НЕ второго канала, группа информационных вхо-. дов входного регистра является группей входов устройства, первый,третий, пятый, седьмой и второй, четвер тый, шестой, восьмой разрядные выход группы выходов входного регистра сое динены с группами входов соответственно элементов ИЛИ и ИЛИ-НЕ третьег канала, группа разрядных выходов выходного регистра соединена с группой входов элемента ИЛИ-НЕ и группой выходов устройства, группа выходов входного регистра соединена с группой информационных входов выходного регистра, введены делитель частоты и распределитель импульсов. Вход делителя частоты соединен с первым тактов 1м входом устройства, выход - со входом распределителя импульсов.Первый и второй выходы распределителя соединены со вторыми входами элемента 2И-ИЛИ первого канала, третий и четвертый выходы - со вторыми входами элементов 2И-ИЛИ второго и трет его каналов, третий выход - со вторы управляющим входом счетчика. На чертеже представлена структур ная схема устройства. Устройство содержит входной регистр 1, выходной регистр 2, группу входов 3 устройства, группу выходов 4 устройства, каналы 5, элементы 2И-ИЛИ 6 каналов, распределитель 7 импульсов, делитель 8 частоты, тактовые входы 9 и 10 устройства, элемент 11 задержки, счетчик 12, дешиф ратор 13, элемент И 14, триггер 15, вход 16 логической единицы устройст ва, элемент ИЛИ-НЕ 17, элементы ИЛИ 18 каналов, элементы ИЛИ-НЕ 19 кана лов, тактовый вход 20 счетчика, управляющие входы 21 и 22 счетчика. Устройство работает следующим образом. По синхросигналу, поступающему на вход 9, информация с группы входов 3 принимается в регистр 1. Триггер 15 сбрасывается по сигналу логической единицы на входе 16 и тактовому импульсу к входу 10. Изменение состояния счетчика 12 ..происходит под действием сигнала на входе 20, Если к моменту прихода это го сигнала на входе 21 присутствует единица, то в счетчик заносится новая информация, если на входе 21 нуль, то содержимое счетчика 12 увеличивается или .уменьшается на едини,цу в зависимости от сигнала на входе 22. При наличии нуля на этом входе единица прибавляется к содержимому счетчика, при наличии единицы на входе 22 единица вычитается. Дешифратор 13 при наличии нуля на выходе .элемента 14 закрыт, на всех его выходах - нули. При появлении единицы на выходе элемента 14 на одном из выходов дешифратора появляется единица, позиция которой определяется входным кодом. Распределитель 7 импульсов предназначен для периодической смены режимов работы устройства, характеризующихся определенным соотношением приоритетов входных сигналов. Элемент 11 предназначен для управления работой счетчика 12, элемент 2И-ИЛИ 6 - для передачи информации на информационные входы счетчика. Делитель 8 частоты предназна- чен для управления работой распределителя 7. Через каналы 5, в состав которых входят элементы 2И-ИЛИ 6, элементы ИЛИ 18, элементы ИЛИ-НЕ 19, осуществляется передача содержимого регистра 1 в счетчик 12. При работе системы, включающей данное многоканальное приоритетное устройство, активный блок, например процессор, инициирующий обмен с устройством общего пользования, при отсутствии относящегося с нему сигнала разрешения на одном из выходов 4, формирует сигнал запроса, который поступает на соответствующий вход 3. Получив сигнал разрешения, активный.блок, не снимая сигнала запроса, производит обмен с устройством общего пользования и по окончании обмена снимает запрос. В ответ на снятие запроса снимается сигнал разрешения, после чего производятся анализ накопившихся запросов, выбор одного из них (в зависимости от приоритета запросов и от состояния выходов распределителя 7), вьщача решения на один из выходов 4 и подключение очерёдного активного блока к устройству общего пользования. Окончание предыдущего обмена активного устройства с устройством общего пользования завершается снятием запроса с одного из входов 3. По сигналу со входа 9 один из триггеров регистра 1, хранящий соответствующий запрос, переходит в нулевое состояние, остальные триггеры регистра 1 фиксируют накопившиеся запросы. Сброс триггера регистра 1 вызывает сброс соответствующего триггера регистра 2, т.е. снятие сигнала разрешения для соответствующего активного устройства. При этом на выходе элемента 17 формируется единица. Этот сигнал переводит триггер 15 в единичное состояние. К этому моменту сигнал 9, пройдя через элемент 11 задержки, поступает на вход 20 счетчика 12, разредиая прием ин формации с информационных входов счетчика 12. После этого на вход триггера 15 со входа 10 поступает сигнал, который сбрасывает триггер 15 в нулевое состояние через элемент 14 открывает дешифратор 13. Сигнал с одного из выходов дешифратора поступает на соответствующий управляемый вход регистра 2, (Если на каком-либо информационном входе регистра 2 присутствует сигнал запроса, то соответствующий триггер регистра 2 устанавливается в состояние единица, и на одном из выходов 4 формируется сигнал раз решения. После этого дешифратор 13 закрывается, так как на выходе элемента 17 будет нуль. Таким образом, быстродействие пр лагаемого устройства повышено. Формула изобретения Многоканальное приоритетное устройство, содержащее входной и выход ной регистры, счетчик, дешифратор, элемент задержки, триггер, элемент элемент ИЛИ-НЕ, три канала, каждый из которых содержит элемент ЙЛй, элемент ИЛИ-НЕ и элемент 2И-ИЛИ,при чем выходы элементов ИЛИ и ИЛИ-НЕ каждого канала соединены соответственно с первыми входами элемента 2И-ИЛИ своего канала, выходы элемен тов 2И-ИЛИ каналов соединены с соот ветствующими информационными входам счетчика, тактовый вход счетчика че рез элемент задержки соединен с пер вым тактовым входом устройства и тактовыг входом входного регистра,в ход триггера соединен с первым управляющим входом счетчика, группа выходов счетчика соединена с грУпйО информационных выходов дешифратора/ управляющий вход дешифратора соедин с выходом элемента И, нулевой вход триггера и первый вход элемента И соединены со вторым тактовым входом устройства, тактовый вход триггера второй вход элемента И соединены с. выходом элемента ИЛИ-НЕ, единичный вход триггера соединен со входом логической единицы устройства, группа выходов дешифратора соединена с группой управляющих входов выходного регистра , с первого по четвертый и с пятого по восьмой разрядные выходы группы выходов входного регистра соединены соответственно с группами входов элементо5з ИЛИ и ИЛИ-НЕ первого канала, первый, второй, пятый, шестой и третий, четвертый, седьмой, восьмой разрядные выходы группы раэрядннх выходов входного регистра соединены соответственно с группами входов элементов ИЛИ и ИЛИ-НЕ второго канала, группа информационных входов входного регистра является группой входов устройства, первый,третий, пятый, седьмой и второй, четвертый, шестой, восьмой разрядные выходы группы выходов входного регистра соединены с группами входов соответственно элементов ИЛИ и ИЛИ-НЕ третьего канала, группа разрядных выходов выходного регистра соединена с группой входов элемента ИЛИ-НЕ и группой выходов устройства, группа выходов входного регистра соединена с группой информационных входов выходного регистра, о т л i ч а ющ е е с я тем, что, с целью повышения быстродействия, устройство содержит делитель частоты и раЬпределитель импульсов, причем вход делителя частоты соединен с первым тактовым входом устройства, выход со входом распределителя импульсов, первый и второй выходы распределителя соединены со вторыми входами элемента 2И-ИЛИ первого канала,третий и четвертый выходы - со вторыми :входами элементов 2И-ИЛИ второго и третьего каналов, третий выход со вторым управляющим входом счетчика. Источники информации, привитые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке № 2700938/19-24, КЛ. G 06 F 9/46, 1978. 2.Авторское свидетельство по заявке 2764576/18-24, КЛ. G 06 F 9/46, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Многоканальное устройство для прерывания программ | 1983 |

|

SU1124301A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для приоритетного обслуживания запросов | 1981 |

|

SU955069A1 |

| Устройство для возведения в квадрат | 1983 |

|

SU1160404A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

Авторы

Даты

1982-01-07—Публикация

1980-03-13—Подача