пятого, шестого, седьмого и десятого элементов И и к третьму входу первого элемента И первого коммутатора, четвертьй информационный вход устройства подключен к третьим входам третьего, пятого, седьмого и десятого элементов И, к вторым входам восьмого и девятого элементов II и к четвертому входу первого элемента И первого коммутатора, выход третьего элемента НЕ устройства подключен к четвертому входу третьего элемента И и.к третьим входам второго и девятого элементов И первого коммутатора, выход четвертого элемента НЕ подключен к четвертому входу второго элемента Инк третьему вход шестого элемента И первого коммутатора, выход элемента ИЛИ-НЕ устройства подключен к четвертым входам шестого, девятого и десятого элементов И первого коммутатора, выход третьего элемента И устройства подключен к пятым входам первого и второго элементов И первого коммутатора выход второго элемента И устройства подключен к четвертым входам четвертого, пятого и седьмого элементов И и к третьему входу восьмого элемента И первого коммутатора, выход первого элемента И устройства подключен к пятому входу третьего элемента И первого коммутатора, пятый, шестой, седьмой, восьмой, девятый и десятый входы элемента ИЛИ первого коммутатора подключены к выходам пятого, шестого, седьмого, восьмого, девятого и десятого элементов И данного коммутатора соответственно, первый информацио1гный вход устройства подключен к первым, входам . первого, второго, третьего, четвертого и пятого элементов И второго коммутатора, второй информационный вход устройства подключен к второму входу четвертого и к первому входу шестого элементов И второго коммутатора, выход первого элемента НЕ устройства подключел к второму входу шестого и к первому входу седьмого элементов И второго коммутатора, выход второго элемента НЕ устройства подключен к первым входам восьмого и девятого и к вторым входам первого и третьего элементов И второго коммутатора, третий информационный вход устройства подключен к первому входу десятого элемента И, к вторым входам второго

00618

и восьмого элементов Ник третьему входу четвертого элемента И второго коммутатора, четвертый-информационный вход устройства подключен к третьему входу шестого и к четвертому входу четвертого элемента И второго коммутатора, выход третьего элейента НЕ устройства подключен к второму входу седьмого элемента И второго коммутатора, выход четвертого элемента НЕ устройства подключен к вторым входам пятого, девятого и десятого элементов И и к третьему входу третьего элемента И второго коммутатора, выход элемента ИЛИ-НЕ устройства подключен к Третьим входам пятого и седьмого элементов И sTopoio коммутатора, выход третьего элемента И устройства подключен к пятому входу четвертого элемента И второго коммутатора, выход второго элемента И устройства подключен к четвертым входам третьего и шестого элементов И второго коммутатора, выход первого элемента И устройства подключен к третьим входам первого, второго, восьмого, девятого и десятого элементов И второго коммутатора, выходы пятого, шестого, седьмого,, восьмого, девятого и десятого элементов И которого подключены к пятому, шестому, седьмому, восьмому, девятому и десятому входам элемента ИЛИ второго коммутатора соответственно, первый информационный вход устройства подключен к первым входам первого, второго, третьего, четвертого, пятого, шестй го и седьмого элементов И третьего коммутатора, второй информационный вход устройства подключён к вторым входам третьего и шестого элементов И и к первым входам восьмого, девятого., десятого, одиннадцатого и двенадцатого элементов И третьего коммутатора, выход первого элемента НЕ устройства подключен к второму входу восьмого элемента И и к первым входам тринадцатого, четьфнадцатого, пятнадцатого и шестнадцатого элементов И третьего коммутатора, выход второго элемента НЕ устройства подключён к второму входу седьмого элемента И третьего коммутатора, третий инфор-. мационный вход устройства подключен к третьему входу шестого элемента И, к вторым входам пятого, четырнадцатого и шестнадцатого элементов И третьего коммутатора, четвертый информационный вход устройства подключен к вторым входам первого, второго, четвертого и двенадцатого длементов И, к третьим входам седьмого, четырнадцатого и шестнадцатого элементов И, к .-четвертому входу шестого элемента И и к первому входу семнадцатого элемента И третьего коммутатора, выход третьего элемента НЕ устройства подключен к вторым входам второго, девятого, тринадцатого, шестнадцатого и семнадцатого элементов И, к третьему Входу первого элемента И и к четвертому входу седьмого элемента И третьего коммутатора, выход четвертого элемента НЕ подключен к вторым входам десятого и одиннадцатого элементов И и к третьему входу пятнадцатого элемента И третьего коммутатора, выход элемента ИЛИ-НЕ устройству подключен к пятым входам шестого и седьмого элементов И третьего коммутатора, выход третьего элемента И устройства подключен к третьим входам третьего, четвертого, пятого и двенадцатого элементов И и к четвертому входу шестнадцатого элемента И третьего коммутатора, выход второго элемента И устройства подключен к третьим входам одиннадцатого и семнадцатого элементов И и к четвертым входам второго, четырнадцатого и пятнадцатого элементов И третьего коммутатора, выход первого, элемента И устройства подключен к третьим входам восьмого, девятого, десятого и трунадцатого элементов И и к четвертому входу первого элемента И третьего коммутатора, выходы элемента И которого подключены к входам элементов ИЛИ данного коммутатора соответственно, выход которого является выходом третьего коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональное устройство | 1985 |

|

SU1291963A1 |

| Многофункциональный логический модуль | 1981 |

|

SU1032449A1 |

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1835542A1 |

| Многофункциональный модуль | 1984 |

|

SU1236459A1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2757817C1 |

| Многофункциональный модуль | 1983 |

|

SU1117629A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| Устройство для LU-разложения матриц | 1988 |

|

SU1548795A1 |

| Многофункциональный логическийМОдуль | 1977 |

|

SU798802A1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

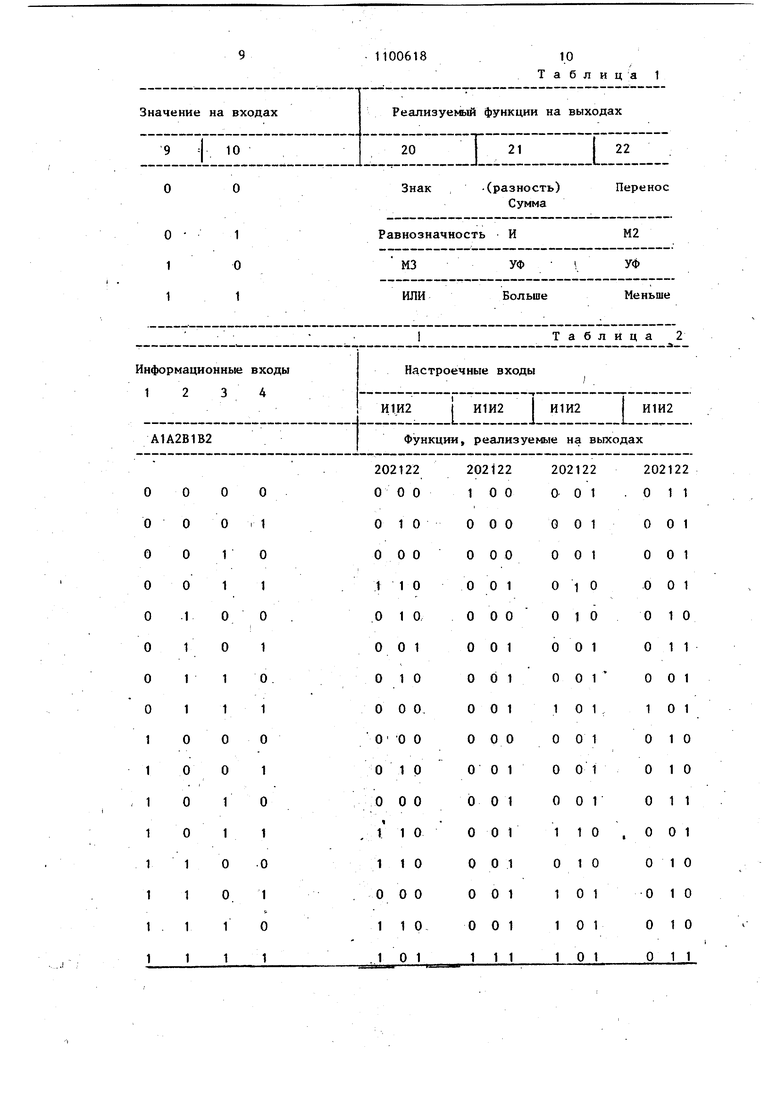

МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО, содержащее элементы И, НЕ и два коммутатора, каждый из которых содержит четыре элемента И и один элемент РШИ, первый и второй информационные входы устройства подключены к входам первого и второго элементов НЕ устройства соответственно, при этом входы элемента ИЛИ первого коммутатора подключены к входам элементов И данного коммутатора, первый и второй входы первого элемента И которого подключены к первому и второму информационным входам уст-. ройства соответственно, выходы первого и второго элементов НЕ устройства подключены к первому и второму входс1м -второго .элемента И первого коммутатора соответственно, выход элемента ИЛИ которого является выходом первого коммутатора, при этом входы элемента ИЛИ второго коммутатора подключены к выходам элементов И данного коммутатора соответственно, выход элемента ИЛИ которого является выходом второго коммутатора, отличающееся тем, что, с целью расширения области применения за счет возможности реали- . зацяи дополнительных логических-функций от четырех входных переменных и операции сравнения, устройство дополнительно содержит элементы И, НЕ, ИЛИ-НЕ и третий коммутатор, причем Первый коммутатор содержит дополнительно шесть элементов И, второй коммутатор содержит дополнительно шесть элементов И, третий коммутатор содержит семнадцать элементов И и один элемент ИЛИ, третий и чеТвертьй инфор мационные входы устройства подключены к входам третьего и четвертого эле ментов НЕ. устройства соответственно, первый настроечный вход устройства i подключен .к первым входам элемента ИЛИ-НЕ, первого и второго элеменКЛ тов И и к входу пятого элемента НЕ, С второй настроечный вход устройства подключен к вторым входам элемен.та ИЖ-НЕ и первого элемента И, к первому входу третьего элемента И и к входу шестого элемента НЕ, выходкоторого подключен к второму входу о BToporj элемента И, выход пятого эле мента НЕ подключен к второму входу третьего элемента И, выходы первого, второго и третьего коммутаторов под00 ключены соответственно к выходам устройства, первый информационней вход устройства подключен к первым вхЬдам третьего, четвертого, пятого и шестого элементов И первого коммутатора, второй информационный вход устройства -подключен к второму входу третьего элемента И, к первому входу седьмого элемента И, к первым входам восьмого, девятого и десятого элементов И первого коммутатора, третий информационный вход устройства подключен к вторым входам четвертого.

Изобретение относится к области вычислительной техники и микроэлектроники.

Известен управляемый арифметический модуль, который реализует широкий круг арифметических операций, сдвиги, функции записи О и 1 l) .

Недостатком известного модуля являются сложность и неоднородность конструкции, низкое быстродействие и ограниченные функциональные возможности, так как модуль не позволяет реализовать операции сравнения входных и универсальных функции.

Наиболее близким к предлагаемому по технической сущноЬти является устройство для логической обработки и вычитанля чисел, содержащее в каждом разряде коммутаторы, элементы И, ИЛИ, НЕ, и НЕРАВНОЗНАЧНаСТЬ, причем,информационные входы устройства подключены к управляю1цим входам коммутаторов, информационные входы которых подключены к управляющим входам устройства соответственно, выход первого коммутатора подключен к входу элемента НЕРАБНОЗНАЧНОСТЬ и через элемент НЕ к входу элемента И, выход которого и выход второго коммутатора подключен к входам элемента ИЛИ,, вход переноса из предыдущего устройства подключен к входам разряда элементов НЕРАВНОЗНАЧНОСТЬ и И, выходы элементов НЕРАВНОЗНАЧНОСТЬ и ИЛИ являются выходами переноса и суммы данного разряда соответственноС2.

Однако такое устройство не позволяет одновременно с арифметико-логической обработкой чисел выполнять операции сравнения, не реализует универсальную логическую функцию от четырех входных переменных, имеет большое число внешних выводов, что в целом ограничивает область его применения.

Целью изобретения является расширение области применения устройства за счет возможности реализации дополнительных логических функций от четырех входных переменных и операции сравнения.

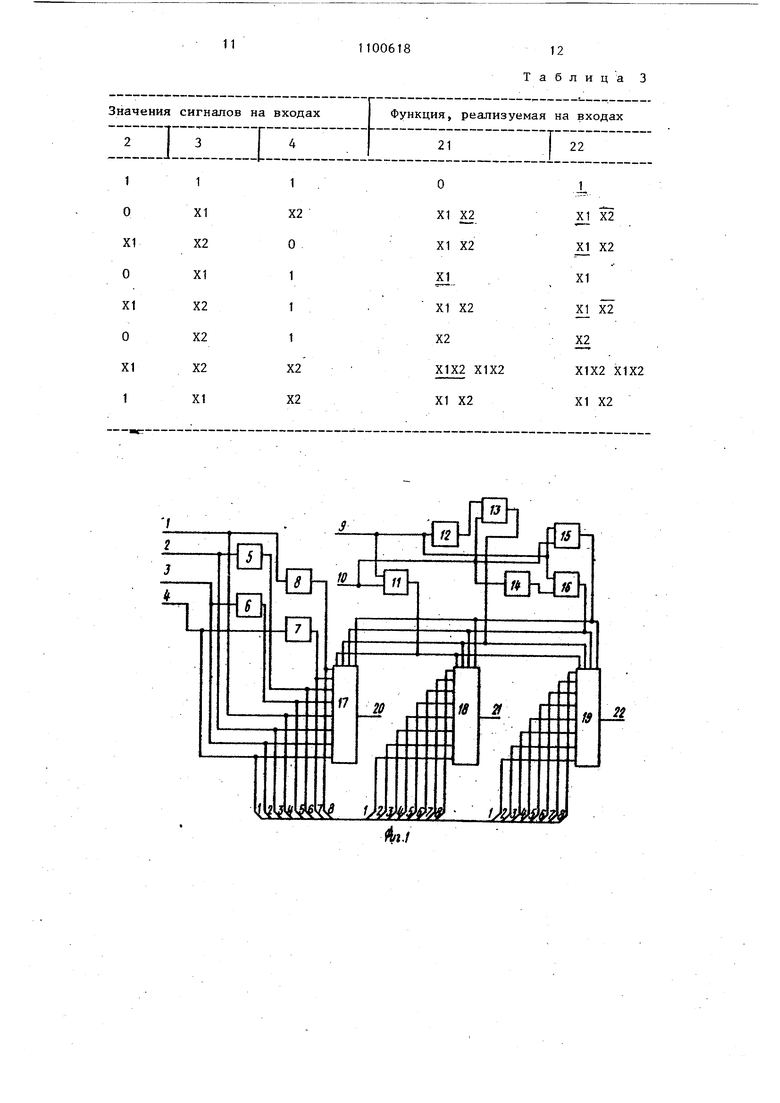

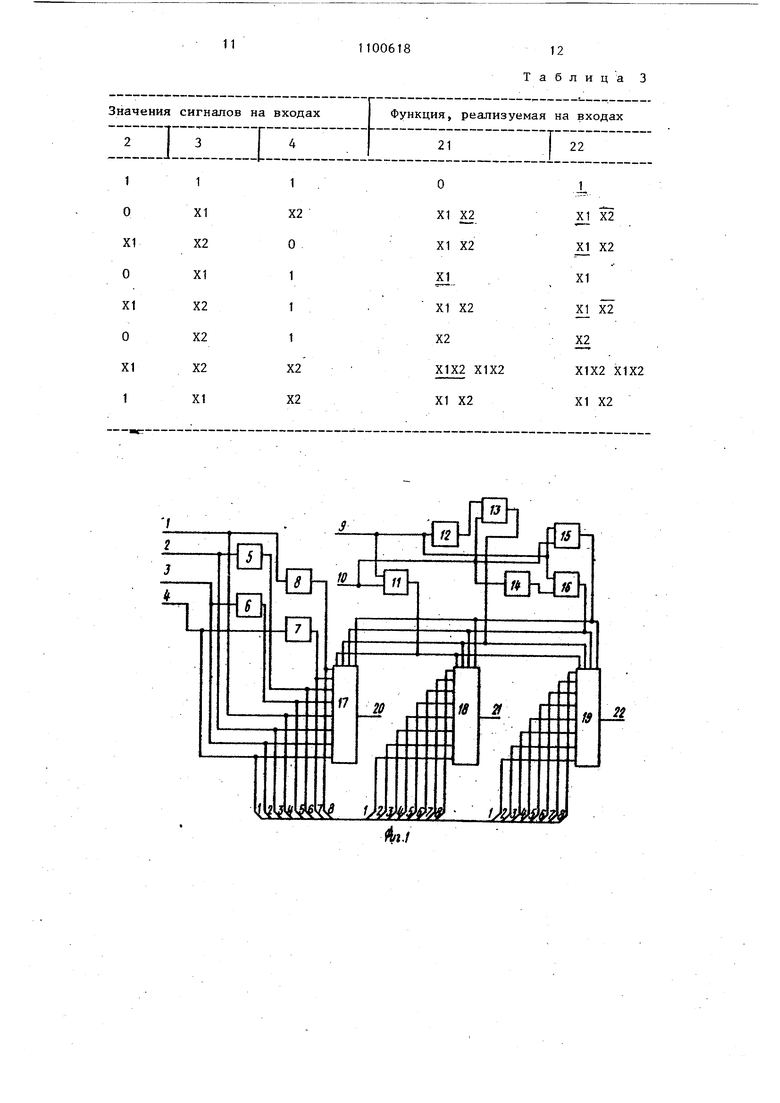

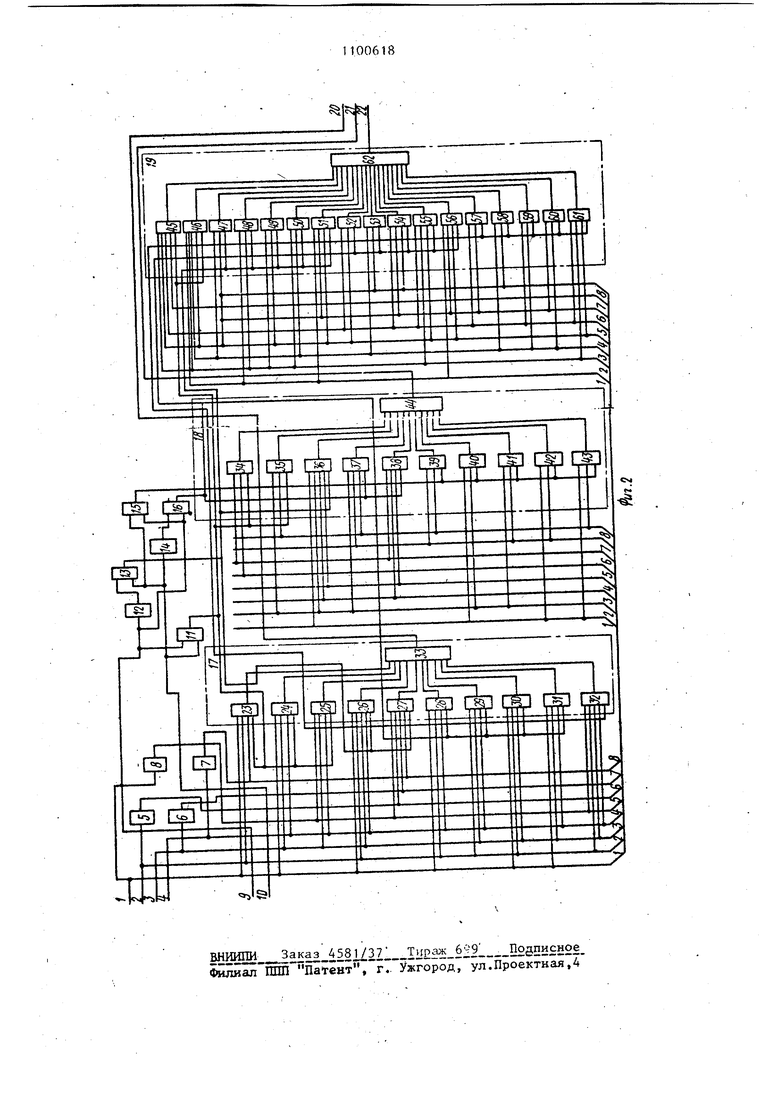

Поставленная цель достигается тем, что многофункциональное устройство, содержащее элементы И, НЕ, и два коммутатора, каждый из которы содержит четыре элемента И и один 3 элемент ИЛИ, первый и второй информ ционные входы устройства подключены к входам первого и второго элементов НЕ устройства соответственно, при этом входы элемента ИЛИ первого коммутатора подключены к входам элементов И данного коммутатора, пе вый и второй входы перв« го элемента И которого подключены к первому и второму информационным входам уст ройства соответственно, выходы первого и второго элементов НЕ устройс ва подключены к первому и второму входам второго элемента И первого коммутатора соответственно, выход элемента ИЛИ которого является выхо дом первого коммутатора, при этом входы элемента ИЛИ второго коммутат ра подключены к выходам элементов И данного коммутатора соответственно, выход элемента ИЛИ которого являетс выходом второго коммутатора, дополн тельно содержит элементы И, НЕ, ИЖ НЕ и третий коммутатор, причем первый коммутатор содержит дополнитель но шесть элементов И, второй коммутатор содержит дополнительно шесть элег-тентов И, третий коммутатор содержит семнадцать элементов И и оди элемент ИЛИ третий и четвертый информационные входы устройства подключены к входам третьего и четвертого элементов НЕ устройства соотве ственно, первый настроечный вход ус ройства подключен к первым входам элемента ИЛИ-НЕ, первого и второго элементов И и к входу пятого элемен та НЕ, второй настроечный вход устройства подключен к вторым входам элемента ИЛИ-НЕ и первого элемента И, к первому входу третьего элемента Инк входу шестого элемента НЕ, выход которого подключен к второму входу второго элемента И, выход пятого элемента НЕ подключен к второму входу третьего элемента И выходы первого, второго и третьего коммутаторов подключены соответственно к выходам устройства, первый информационный вход устройства подключен к первым входам третьего, че вертого, пятого и шестого элементов И первого коммутатора, второй информационный вход устройства подключен к второму входу третьего эле мента И, к первому входу седьмогр элемента И, к первым входам восьмог девятого и десятого элементов И пер 184 Boro коммутатора, третий информационный вход устройства подключен к вторым входам четвертого,ПЯТОГО, шестого, седьмого и десятого элементон И и к третьему входу первого элемента И первого коммутатора, четвертый информационный вход устройства подключен к третьим входам третьего, пятого, седьмого и десятого элементов И, к вторым входам восьмого и девятого элементов Ник четвертому входу первого элемента И первого коммутатора, выход третьего элемента НЕ устройства подключен к четвертому входу третьего элемента И и к третьим входам второго и девятого элементов И первого коммутатора, выход четвертого элемента НЕ подключен к четвертому входу второго элемента И и к третьему входу шестого элемента И первого коммутатора, выход элемента ИЛИ-НЕ устройства подключен к четвертым входам шестого, девятого и десятого элементов И первого коммутатора, выход третьего элемента И устройства подключен к пятым входам первого и второго элементов И первого коммутатора, выход второго элемента И устройства подключен к четвертым входам четвертого, пятого и седьмого элементов И и к третьему входу восьмого элемента И первого коммутатора, выход первого элемента И устройства подключен к пятому входу третьего элемента И первого коммутатора, пятый, шестой, седьмой, восьмой, девятый и десятьй входы элемента ИЛИ первого коммутатора подключены к выходам пятого, шестого, седьмого, восьмого, девятого и десятого элементов И данного коммутатора соответственно, первый информационный вход устройства подключен к первым входам первого, второго, третьего, четвертого и пятого элементов И второго коммутатора, второй информационный вход устройства подключен к второму входу четвертого и к первому входу шестого элементон И второго коммутатора, выход первого элемента НЕ устройства подключен к второму входу шестого и к первому входу седьмого элементов И второго коммутатора, выход второго элемента НЕ устройства подключен к первым входам восьмого и девятого и к вторым входам первого и третьего элементов И второго коммутатора, третий информационный вход устройства подключен к первому входу десятого элемента И, к вторым входам второго и восьмого элементов И и к третьему входу четвертого элемента И второго коммутатора, четвертый информационный вход устройства подключен к третьему входу шестого и к четвертому входу четвертого элемента И второго коммутатора, выход третьего элемента НЕ устройства подключен к второму входу седьмого элемента И второго коммутатора, выход четвертого элемента НЕ устройства подключен к вторым входам пятого, девятого и десятого элементов Инк третьему входу третьего элемента И второго коммутатора, выход элемента Ш1И-НЕ устройст ва подключен к третьим входам пятого и седьмого элементов И второго коммутатора, выход третьего элемента И устройства подключен к пятому входу четвертого элемента И второго коммутатора, выход второго элемента И устройства подключен к четвертым входам третьего и шестого элемен тов И второго коммутатора, выход пер вого элемента И устройства подключен к третьим входам первого, второго, восьмого, девятого и десятого элементов И второго коммутатора, выходы пятого, шестого, седьмого, восьмого девятого и десятого элементов И которого подключены к пятому, шестому седьмому, восьмому, девятому и десятому входам элемента ИЛИ второго ком мутатора соответственно, первый информационный вход устройства подключен к перв1 1м входам первого, второго третьего,.четвертого, пятого, шестого и седьмого элементов И третьего коммутатора, второй информационный вход устройства подключ л к вторым входам третьего и шестого элементов Ник первым входам восьмого, девятого, десятого, одиннадцатого и двенадцатого элементов И третьего коммутатора, выход первого элемента НЕ устройства подключен к второму входу восьмого элемента Инк первым входам тринадцатого, четырнадцатого пятнадцатого и шестнадцатого элемен тов И третьего коммутатора, выход второго элемента НЕ устройства подключен к второму входу седьмого эле мента И третьего коммутатора, трети информационный вход устройства подключен к третьему входу шестого эле мента И, к вторым входам пятого, четырнадцатого и шестнадцатого элементов И третьего коммутатора, четвертый информационный вход устройства подключен к вторым входам первого, второго; четвертого и двенадцатого элементов И, к третьим входам седьмого, четырнадцатого и шестнадцатого элементов И, к четвертому входу шестого элемента И и к первому входу семнадцатого элемента И третьего коммутатора, выход третьего элемента НЕ устройства -подключен к вторым входам второго, девятого, тринадцатого, шестнадцатого и семнадцатого элементов И, к третьему входу первого элемента И и к четвертому входу седьмого элемента И третьего коммутатора, выход четвертого элемента НЕ подключен к вторым входам десятого и одиннадцатого элементов И и к третьему входу пятнадцатого элемента И третьего коммутатора, выход элемента ИЛИ-НЕ устройства подключен к пятым входам шестого и седьмого элементов И третьего коммутатора, выход третьего элемента И устройства подключен к третьим входам третьего, четвертого, пятого и двенадцатого элементов И и к четвертому входу шестнадцатого элемента И третьего коммутатора, выход второго элемента И устройства подключен к третьим входам одиннадцатого и семнадцатого элементов Инк четвертым входам второго, четырнадцатого и пятнадцатого элементов И третьего коммутатора, выход первого элемента И устройства подключен к третьим входам восьмого, девятого, десятого и тринадцатого элементов Ник четвертому входу первого элемента И третьего коммутатора, выходы элементов И которого подключены к входам элементов ИЛИ данного коммутатора соответственно, выход которого является выходом третьего коммутатора. На фиг. 1 представлена структурнофункциональная схема многофункциональ кого устройства,на фиг. 2- функциональная схема многофункционального устроит;, ства. Многофункциональное устройство (фиг. 1) содержит информационные входы 1-4, элементы НЕ 5-8, входы 9-10, элемент ИЛИ-НЕ 11, элемент НЕ 12, элемент И 13, элемент НЕ 14, элементы И 15 и 16, коммутаторы 17-19, выходы устройства 20-22. 7 Функциональная схема многофункцио нального устройства (фиг. 2) содержи также элементы И 23-32,элемент или 33 элементыИ 34-43, элемент ИЛИ 44, элементы И 45-61, элемент ИЛИ 62. Входы 1-4 непосредственно и через элементы НЕ 8, 5,6, 7 подключены к коммутаторам 17,18 и 19. Настроечный вход 9 подключен к элементам НЕ 12, И 15, И 16 и ИЛИ-НЕ 11. Настроечный вход 10 подключен к элементам.ИЛИНЕ 11, И 13, И 15, НЕ 14. Выходы эле ментов НЕ 12 и 14 подключены соответ ственно к входам элементов И 13 и 16 ВЫХОДЫ.которых совместно с выходами элементов ИЛИ-НЕ 11 и И 15 подключены к каждому из коммутаторов 17, 18 и 19. Выходы коммутаторов подключены к выходам устройства. Функциональные связи схем коммутаторов с входами устройства и с дру гими элементами представлены на фиг. Устройство выполняет функции, определенные в табл. 1. Все функции, указанные в табл. 1, реализуются для четырех переменных, подаваемых на информационные входы 1-4. Логически функционирование устрой ства определяется табл. 2. При реализации универсальной функ ции устройство работает следующим образом. Как следует из табл. 1, для настройки устройства на эту функцию на настроечные входы 9, 10 необходимо подать соответственно сигналы И О. В этом случае при подаче на входы 1-4 информационных переменных А1, А2, В1, В2 с выхода 20 снимается функция МЗ, с выхода 21 - универсальная функция, а с выхода 22 - ее инверсная. Рассмотрим выход 21 для данного набора настроечных сигналов F(A1,A2,B1,B2)A1A2B1B2 Y А1А2В1В2 Y А1А2В1В2 Y Y, А1А2В1В2 618 А2В1В2 Y А1В1В2 R(A2,B1,B2), где R - функция равнозначности. В этом устройство на выходах 21 и 22 реализует набор логических функций, заданный табл. 3. Аналогично устройство реализует функцию срвненИя пар чисел и и определяет факт равенства и неравенства. В случае а,а2 в,Во (управляющие сигналы на входах 9 и 10 равны 1) с выходов 21 и22 снимаются константы 1.Если , то с выхода 21 снимается константа 1, ас выхода 22 константа О. В противном случае с выхо да 21 снимается константа О, а с выхода 22 константа 1. Аналогичным образом можно пояснить функционирование устройства при реализации остальных функцийуОпределенных . табл. 1 и 2. Таким образом, данное многофункциональное устройство обладает дополнительными функциональными возможностями по сравнению с устройством-прототипом (реализует такие функции, как суммы, равнозначности, модулей два и три. И, ИЛИ, сравнения и универсальные функци. Несмотря на широкий класс реализуемых функций устройство обладает достаточной простотой и может быть реализовано на базе одного кристалла в риде одной интегральной микросхемы. Устройство обладает высоким быстродействием, так как имеет всего четыре уровня. Данное устройство целесообразно реализовать на основе интегральной технологии и использовать б качестве дополнительного в существующих сериях интегральных микросхем, что позволит расширить область применения существующих микросхем, а в ряде случаев сократить сложность устройств , реализуемых на микросхемах, а также повысить быстродействие устройств и снизить их стоимость.

Таблица 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Управляемый арифметический модуль | 1978 |

|

SU802961A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для логической обработки и вычитания двоичных чисел | 1979 |

|

SU855655A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-30—Публикация

1982-12-29—Подача