Изобретение относится к вычислительной технике и шгкроэлектронике.

Целью изобретения является расширение функциональных возможностей устройства за счет реализации функции умножения и памяти и обеспечения возможности его использования в качестве ячейки однородных наращиваемых структур.

На чертеже приведена функциональная схема многофункционального устройства.

Устройство содержит информационные входы 1-4, настроечные входы 5 и 6, выходы 7-10, элементы НЕ 11, 12, и 12,, 13,-13, элементы И 14, -14 , 15, -15 , элементы ИЛИ 16, и 16

ментами И 17,-17

первый коммутатор с элеи элементом ИЛИ

17, , второй коммутатор с элементами И 18,-18, и элементом ИЛИ 18, , третий коммутатор с элементами И

19,-19,

и элементом ИЛИ 19 ,

вертый коммутатор, с элементами И 20., -20,., и элементом ИЛИ 20,s .

В статике сигналы на входах устройства отсутствуют.

В динамике устройство функционирует следующим образом.

На информационные входы 1,2 и 3,4 подаются пары разрядов двух двоичных чисел А и В. Одновременно на управляющие входы 5 и 6 подаются константы О и 1, определяющие вид реализуемой устройством функщга.

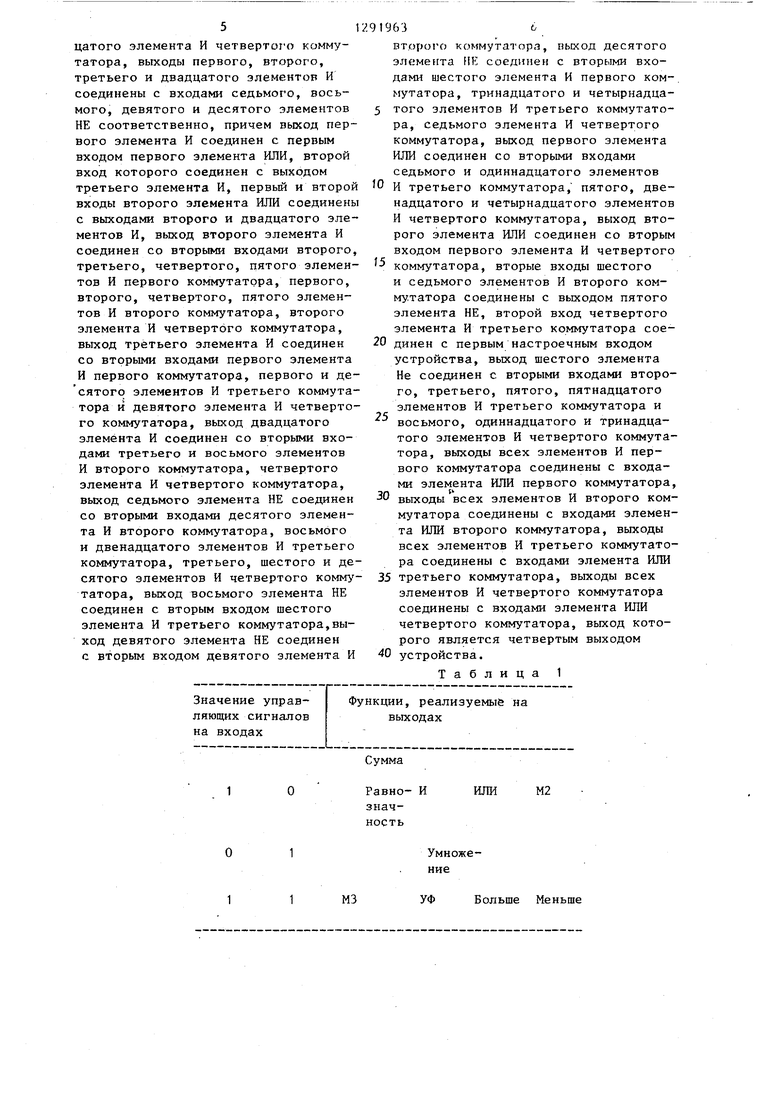

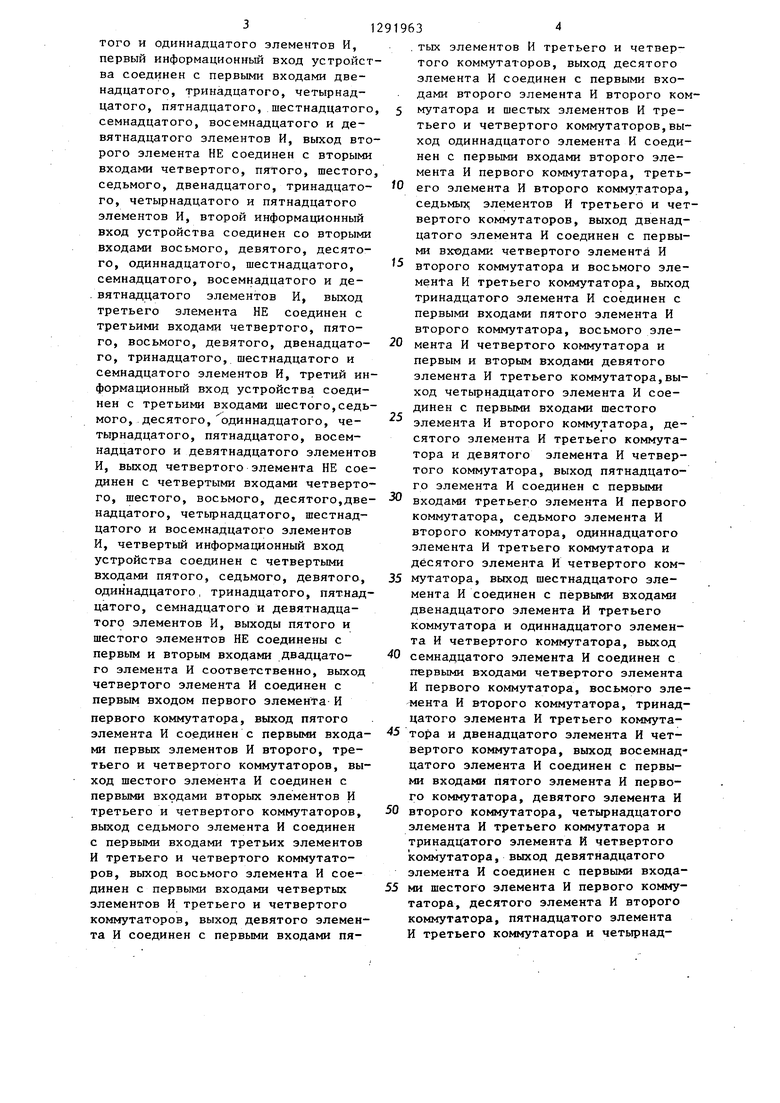

Все функции, реализуемые устройством, приведены в табл. 1.

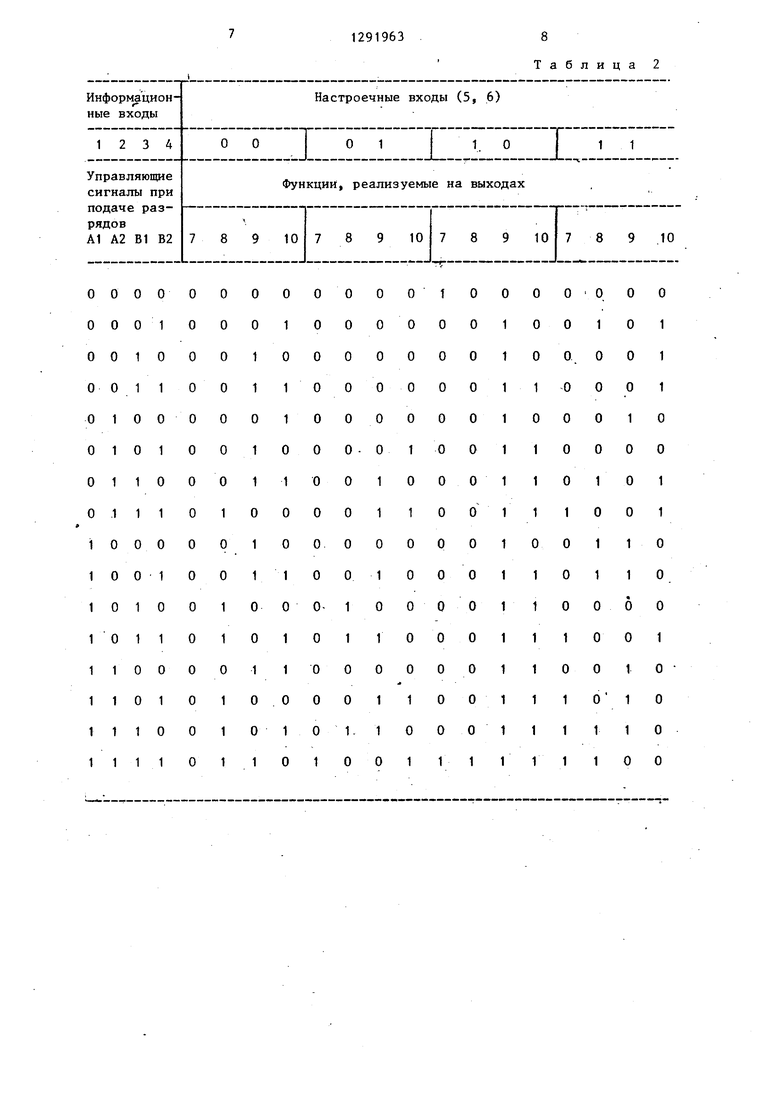

Логически функционирование устройства определяется табл. 2.

Как следует из приведенных таблиц при подаче на входы 5 и 6 устройства констант 1,1, с выхода 7 снимается функция МЗ, с выхода 8 - универсальная функция, с вькода 9 - А1А2 В1В2, с выхода 10 - А1А2 В1В2.

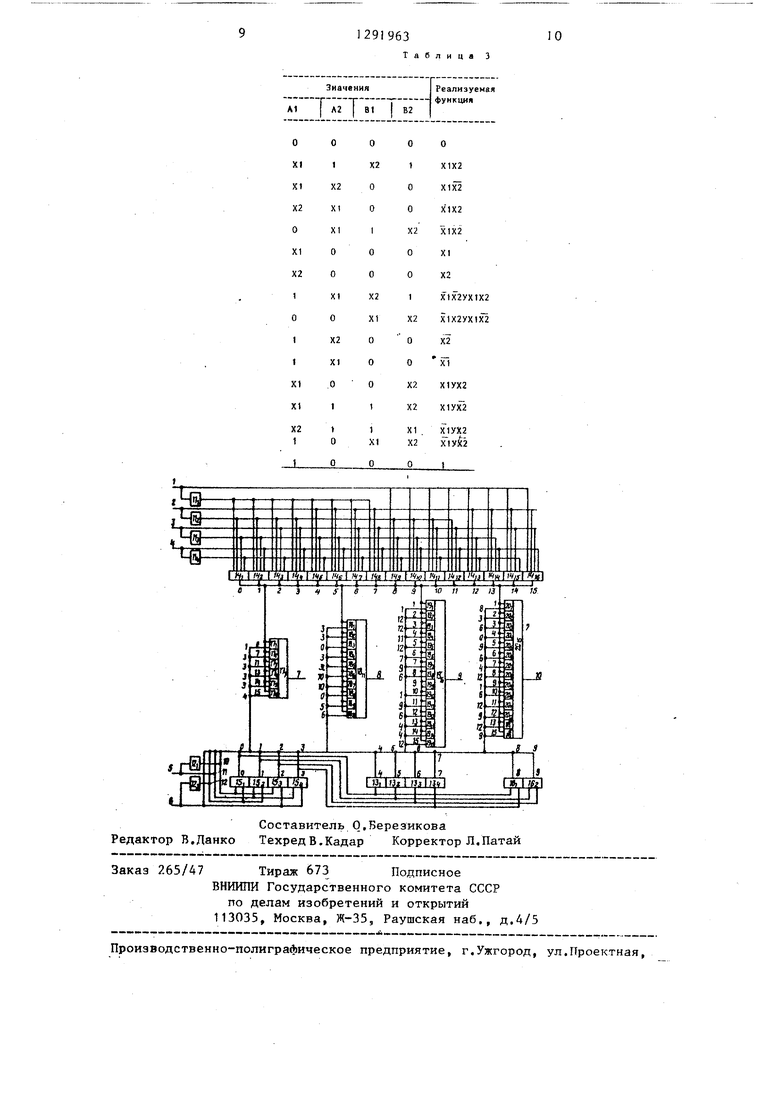

Универсальная функция (УФ) в соответствии с табл. 2 логически описывается выражением вида УФ А1А2В1В2 У А 1А2 1В2 У А1А2вТв 2У У A1A2BJB2 У А1А2В1В2 У А1А2В1В2 А1А2В1 У А1А2В1 У А2В1В2 У А2В1В2 Данная функция обеспечивает реализацию всех логических функций двух переменных (табл. 3).

I..

Кроме того, используя логические

свойства УФ при , , , , последняя обеспечивает реализацию функции памяти Х1Х2УХ1Р XI +

+ Р + Х2. .

Аналогичным образом устройство функционирует при реализации остальных функций, указанных в табл. 1.

Таким образом, предложенное многофункциональное устройство обладает дополнительными функциональными возможностями - реализует функции умножения и памяти. Кроме того, устройство имеет число выходов, разное числу входов - 4,. что обеспечивает его использование в качестве ячейки однородных структур.

Несмотря на широкий класс реализуемых функций устройство обладает достаточной простотой и может быть реализовано на базе одного кристалла в виде одной интегральной микросхемы. Устройство имеет высокое быстродействие, так как имеет всего 4 уровня логических элементов.

Формула изобретения

Многофункциональное устройство, содержащее элементы И, элементы НЕ, три коммутатора, содержащих элементы

И и ИЛИ-, причем первый, второй, третий и четвертый информационные входы устройства соединены с первым, вторым, третьим и четвертым элементами НЕ соответственно, первый и второй

настроечные входы устройства соединены с пятым и шестым элементами НЕ соответственно, выход пятого элемента НЕ соединен с первым входом первого элемента И, второй вход котороГО соединен с вторым настроечным входом устройства и первым входом второго элемента И, второй вход которого соединен с первым настроечньш входом устройства и первым входом

третьего элемента И,второй вход которого соединен с выходом шестого элемента НЕ, выходы первого, второго и третьего коммутаторов являются первым, вторым и третьим выходами устройства соответственно, отличающееся тем, что, с целью расширения функциональных возможностей за счет реализации функций умножения и памяти, устройство содержит первый

И второй элементы ИЛИ, четвертый коммутатор, причем выход первого элемента НЕ соединен с первыми входами четвертого, пятого, шестого, седьмого, восьмого, девятого десятого и одиннадцатого элементов И, первый информационный вход устройства соединен с первыми входами двенадцатого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого семнадцатого, восемнадцатого и девятнадцатого элементов И, выход второго элемента НЕ соединен с вторыми входами четвертого, пятого, шестого седьмого, двенадцатого, тринадцатого, четырнадцатого и пятнадцатого элементов И, второй информационный вход устройства соединен со вторыми входами восьмого, девятого, десятого, одиннадцатого, шестнадцатого, семнадцатого, восемнадцатого и де- . вятнадцатого элементов И, выход третьего элемента НЕ соединен с третьими входами четвертого, пятого, восьмого, девятого, двенадцатого, тринадцатого, шестнадцатого и семнадцатого элементов И, третий информационный вход устройства соединен с третьими входами шестого,седьмого, десятого, одиннадцатого, четырнадцатого, пятнадцатого, восемнадцатого и девятнадцатого элементо И, выход четвертого элемента НЕ соединен с четвертыми входами четвертого, шестого, восьмого, десятого,двенадцатого, четырнадцатого, шестнадцатого и восемнадцатого элементов И, четвертый информационный вход устройства соединен с четвертыми входами пятого, седьмого, девятого, одиннадцатого, тринадцатого, пятнадцатого, семнадцатого и девятнадцатого элементов И, выходы пятого и шестого элементов НЕ соединены с первым и вторым входами двадцатого элемента И соответственно, выход четвертого элемента И соединен с первым входом первого элемента- И первого коммутатора, выход пятого элемента И соединен с первыми входами первых элементов И второго, третьего и четвертого коммутаторов, выход шестого элемента И соединен с первыми входами вторых элементов И третьего и четвертого коммутаторов, выход седьмого элемента И соединен с первыми входами третьих элементов И третьего и четвертого коммутаторов, выход восьмого элемента И соединен с первыми входами четвертых элементов И третьего и четвертого коммутаторов, выход девятого элемента И соединен с первыми входами пя5

. тых элементов И третьего и четвертого коммутаторов, выход десятого элемента И соединен с первыми входами второго элемента И второго ком- 5 мутатора и шестых элементов И третьего и четвертого коммутаторов,выход одиннадцатого элемента И соединен с первыми входами второго элемента И первого коммутатора, треть- 0 его элемента И второго коммутатора, седьмых элементов И третьего и четвертого коммутаторов, выход двенадцатого элемента И соединен с первыми входами четвертого элемента И 5 второго коммутатора и восьмого элемента И третьего коммутатора, выход тринадцатого элемента И соединен с первыми входами пятого элемента И второго коммутатора, восьмого эле- 0 мента И четвертого коммутатора и первым и вторым входами девятого элемента И третьего коммутатора,выход четырнадцатого элемента И соединен с первыми входами шестого элемента И второго коммутатора, десятого элемента И третьего коммутатора и девятого элемента И четвертого коммутатора, выход пятнадцатого элемента И соединен с первыми входами третьего элемента И первого коммутатора, седьмого элемента И второго коммутатора, одиннадцатого элемента И третьего коммутатора и десятого элемента И четвертого ком- 5 мутатора, выход шестнадцатого элемента И соединен с первыми входами двенадцатого элемента И третьего коммутатора и одиннадцатого элемента И четвертого коммутатора, выход 0 семнадцатого элемента И соединен с первыми входами четвертого элемента И первого коммутатора, восьмого элемента И второго коммутатора, тринадцатого элемента И третьего коммута- 5 тора и двенадцатого элемента И четвертого коммутатора, выход восемнадцатого элемента И соединен с первыми входами пятого элемента И первого коммутатора, девятого элемента И 0 второго коммутатора, четырнадцатого элемента И третьего коммутатора и тринадцатого элемента И четвертого коммутатора, выход девятнадцатого элемента И соединен с первыми входа- 5 ми шестого элемента И первого коммутатора, десятого элемента И второго коммутатора, пятнадцатого элемента И третьего коммутатора и четырнадцатого элемента И четвертого коммутатора, выходы первого, второго, третьего и двадцатого элементов И соединены с входами седьмого, восьмого, девятого и десятого элементов НЕ соответственно, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый и второй входы второго элемента ИЛИ соединены с выходами второго и двадцатого элементов И, выход второго элемента И соединен со вторыми входами второго, третьего, четвертого, пятого элементов И первого коммутатора, первого, второго, четвертого, пятого элементов И второго коммутатора, второго элемента И четвертого коммутатора, выход третьего элемента И соединен со вторыми входами первого элемента И первого коммутатора, первого и де- сятого элементов И третьего коммутатора и девятого элемента И четвертого коммутатора, выход двадцатого элемента И соединен со вторыми входами третьего и восьмого элементов И второго коммутатора, четвертого элемента И четвертого коммутатора, выход седьмого элемента НЕ соединен со вторыми входами десятого элемента И второго коммутатора, восьмого и двенадцатого элементов И третьего коммутатора, третьего, шестого и десятого элементов И четвертого коммутатора, выход восьмого элемента НЕ соединен с вторым входом шестого элемента И третьего коммутатора,выход девятого элемента НЕ соединен с вторым входом девятого элемента И

Функции, реализуемые на выходах

МЗ

BT.opoi o кo fмyтaтopa, нькод десятого элемента tIE соединен с вторыми входами шестого элемента И первого ком-, мутатора, тринадцатого и четырнадца- того элементов И третьего коммутатора, седьмого элемента И четвертого коммутатора, выход первого элемента ИЛИ соединен со вторыми входами седьмого и одиннадцатого элементов PJ третьего коммутатора, пятого, двенадцатого и четырнадцатого элементов И четвертого коммутатора, выход второго элемента ИЛИ соединен со вторым входом первого элемента И четвертого коммутатора, вторые входы шестого и седьмого элементов И второго коммутатора соединены с выходом пятого элемента НЕ, второй вход четвертого элемента И третьего коммутатора сое- динен с первым настроечным входом устройства, выход шестого элемента Не соединен с вторыми входами второго, третьего, пятого, пятнадцатого элементов И третьего коммутатора и восьмого, одиннадцатого и тринадцатого элементов И четвертого коммутатора, выходы всех элементов И первого коммутатора соединены с входами элемента ИЛИ первого коммутатора, выходы всех элементов И второго коммутатора соединены с входами элемента ИЛИ второго коммутатора, выходы всех элементов И третьего коммутатора соединены с входами элемента ИЛИ третьего коммутатора, выходы всех элементов И четвертого коммутатора соединены с входами элемента ИЛИ четвертого коммутатора, выход которого является четвертым выходом устройства.

Таблица 1

И

ИЛИ

М2

Умножение

УФ

Больше Меньше

00000 О О О 00 о

001 о о 010 о о 01 1 100 101 110

о о о о о о

о о

о 1 1 о 1 1

000000

000000

10 о 00 10000

о

о о о о

о о 0-01 о о

1 о

1 1 о 1

о 00

0111

о

1

0000

000о о

001о о 010 о 1

000

1 о о

1 1 о 1

о о

000-1 о о

011 100 101 110

111

о о о

о 1

о о

о 1

о 1

1

о

0000

00 о о

о 1

1 о 1

о

о о

1100 1.1 о 00 001 11

Таблица 2

t о о о о о о о

00101

о

о о

00001

1000 1

00010

0000

о 00

1 о 0

о о

о о о о

о 1

о о

о

о о

о о

о

о о

о

0

о

о о

100 о 00 1 11

о о

о 1 1

1

о о о

о о

Тавлнца 3

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2006 |

|

RU2336562C2 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| Устройство резервирования при отказе выключателей линий схемы шестиугольника | 2020 |

|

RU2733861C1 |

| Ассоциативный запоминающий элемент | 1982 |

|

SU1057988A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| Многофункциональный модуль | 1983 |

|

SU1117629A1 |

| Многофункциональный логическийМОдуль | 1977 |

|

SU798802A1 |

Изобретение относится к области вычислительной техники и микроэлектроники и предназначено для реализации арифметических и логических операций. Позволяет осуществлять сравнение двух двухразрядных чисел. Цель изобретения состоит в расширении функциональных возможностей и областей практического применения за счет обеспечения использования устройства в качестве ячейки однородных наращиваемых структур. Устройство содерзкит элементы НЕ, И, ИЛИ и четыре коммутатора, реализованные на основе элементов И, ИЛИ и имеет четыре входные шины, четьфе выходные шины и два входа настройки. Сигналы настройки обеспечивают настройку устройства на реализацию любой функции из заданного множества. 1 ил. 3 табл.с

| Устройство для логической обработки и вычитания двоичных чисел | 1979 |

|

SU855655A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многофункциональное устройство | 1982 |

|

SU1100618A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-10-10—Подача