(54) УСТРОЙСТВО для ЛОГИЧЕСКОЙ ОБРАБОТКИ И ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ Изобретение огносится к вычислительной технике и может использоваться при конструировании устройств обработки цифровой информации. Известно устройство для вычитания двоичных чисел, содержащее два сумматора, элемент задержки, ключ элементы И, ИЛИ, информационные входы, вход заема, выход результата и выход 3 аема 11. Недостатком данного устройства является то, что оно выполняет толь ко одну арифметическую операцию вычитание. Реализация только одной Операции ограничивает область применения устройства. Наиболее близким к предлагаемому является устройство, содержащее два коммутатора, выходы которых являются выходами устройства, управляющие входы коммутаторов попарно объе динены и подключены ко входам усгройства, информационные входы коммутаторов являются входами устройст ва. устройство при подаче на его управляющие входы двоичных сигналов А и В, а. на его информационные входы сигналов О и 1, образующих соответствующие коды настройки, pe лизует любые логические операции переменных А и в f 2 . Недостатком данного устройства является то, что оно не регшизует а1 ифметических операций, например операции вычитания А-В или В-А, что ограничиваетобласть применения устройства. Цель изобретения - расширение области применения устройства путем реализации в нем операций вычитания кодов двоичных чисел. Поставленная цель достигается тем, что в устройство для логической обработк.и и вычитания двоичных чисел, содержгидее два коммутатора, управляющие входы которых попарно объединены и подключены к информационным входам устройства, а информационные входы являются управляющими входами устройства, в устройство введены элементы НБ, ИЛИ, И и ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом результата устройства, вый вход элемента ИСКЛЮЧАКХЦЕЕ Й.11И подключен к выходу первого коммутатора и входу элемента НЕ, а второй вход - ко входу заема устройства и-к первому входу элемента И, второй вход которого подключен к выходу

ломснта НЕ, а выход элемента И соеинен с одним из входов элемента ЛИ, другой вход которого подключен к выходу второго коммутатора, а выход яв яется выходом заема устройстэа.

Устройство, кроме операций логиеской обработки двоичных переменных еализует и арифметические операции х вычитания.

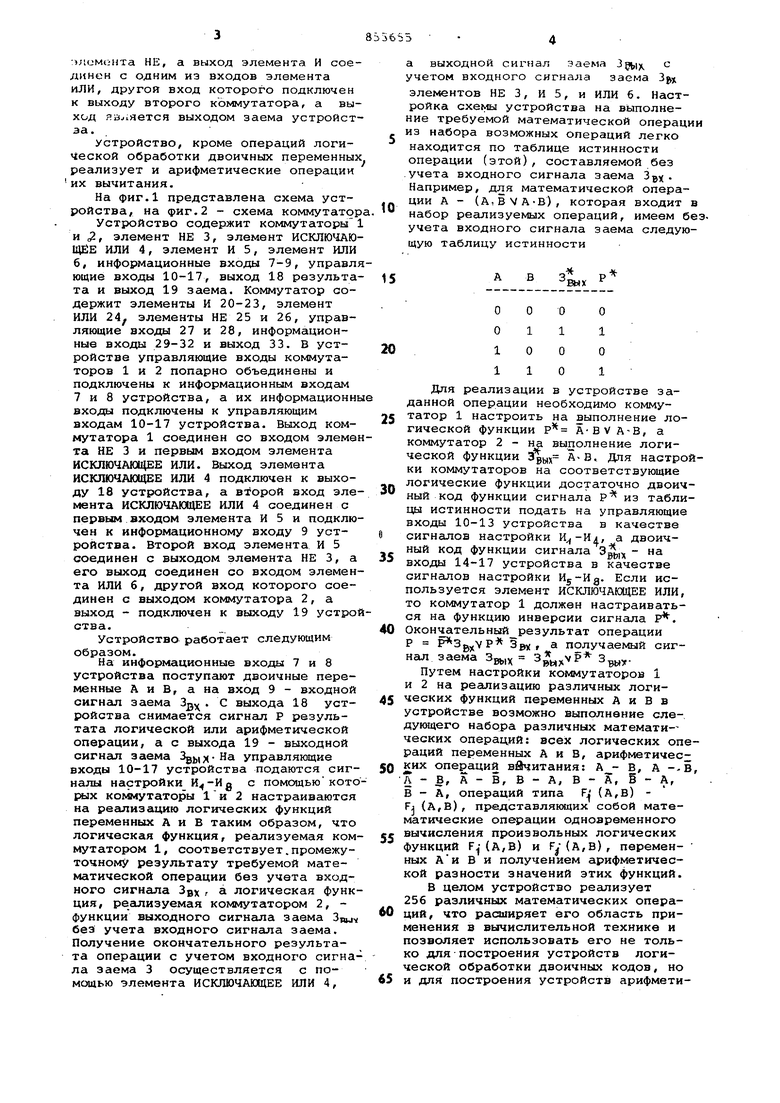

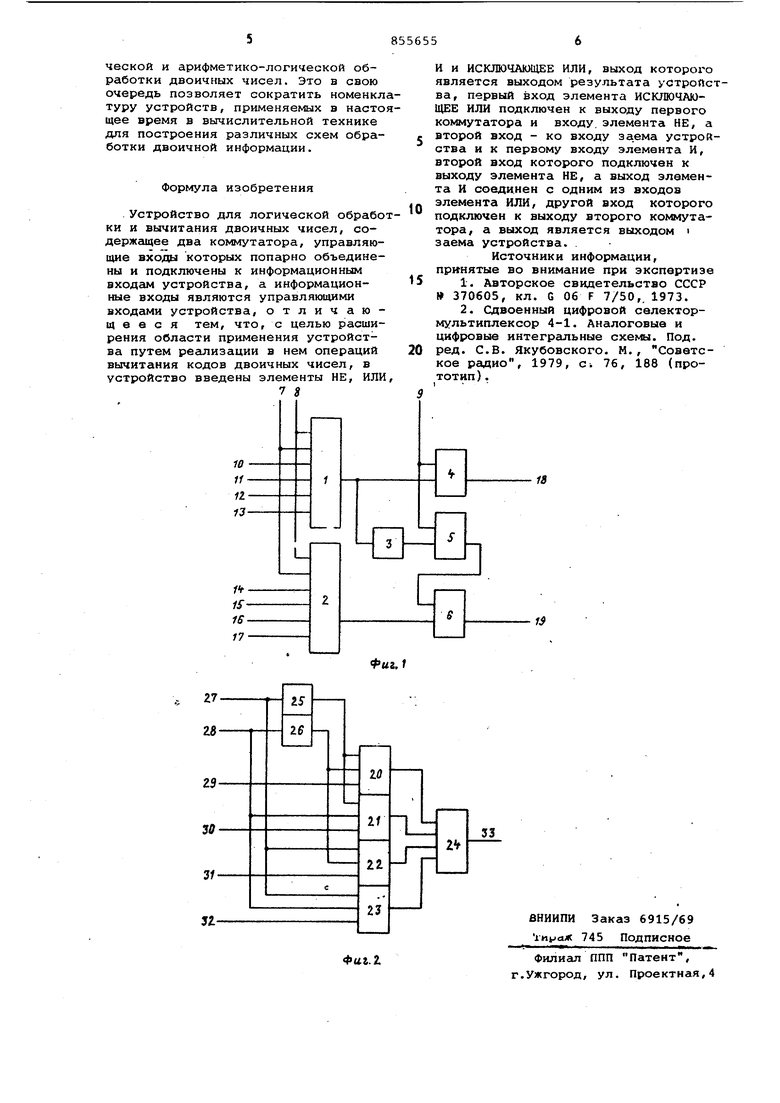

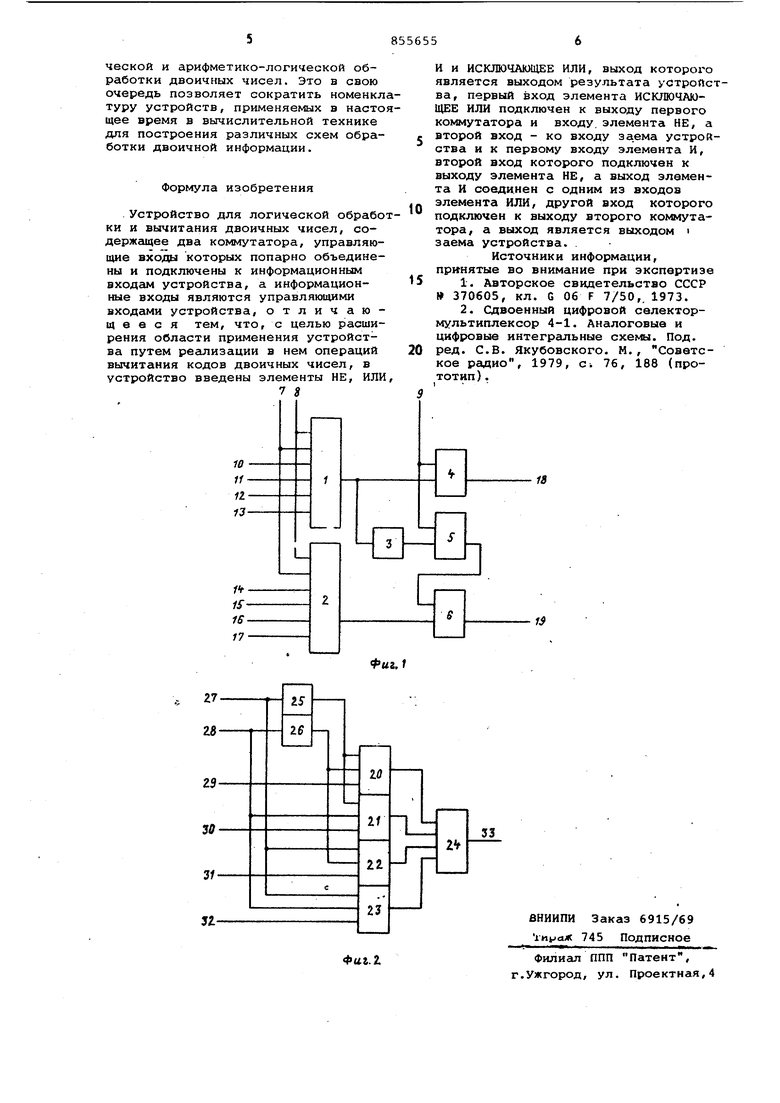

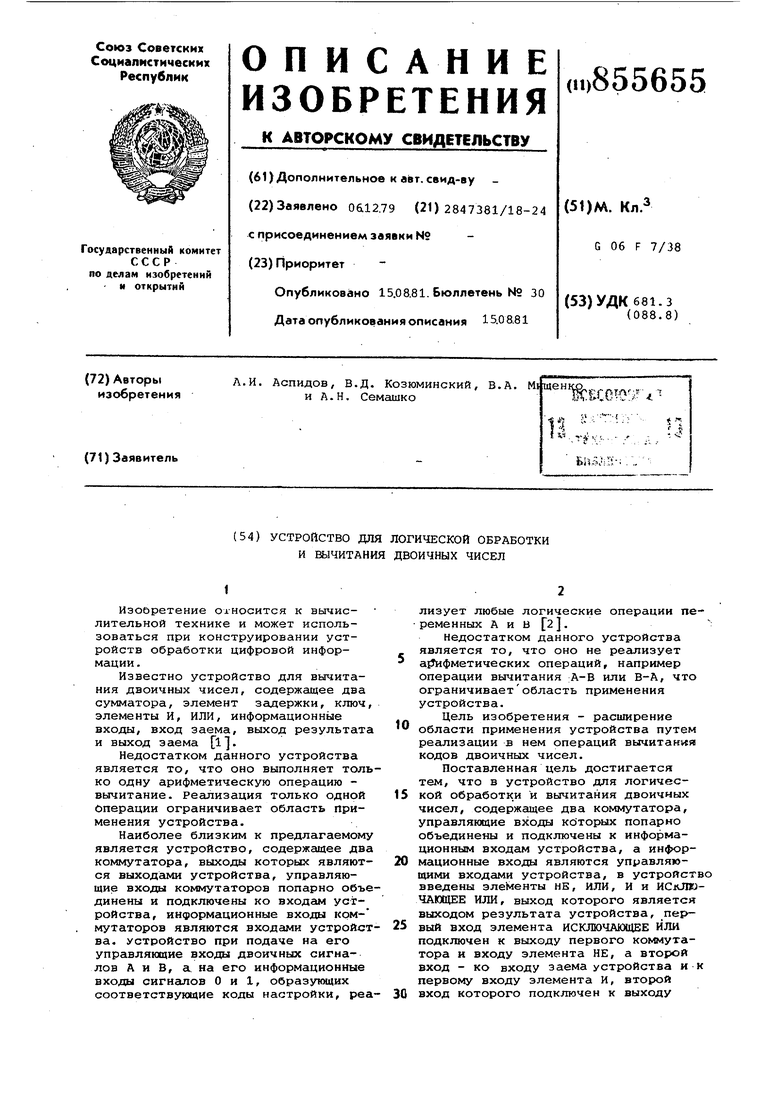

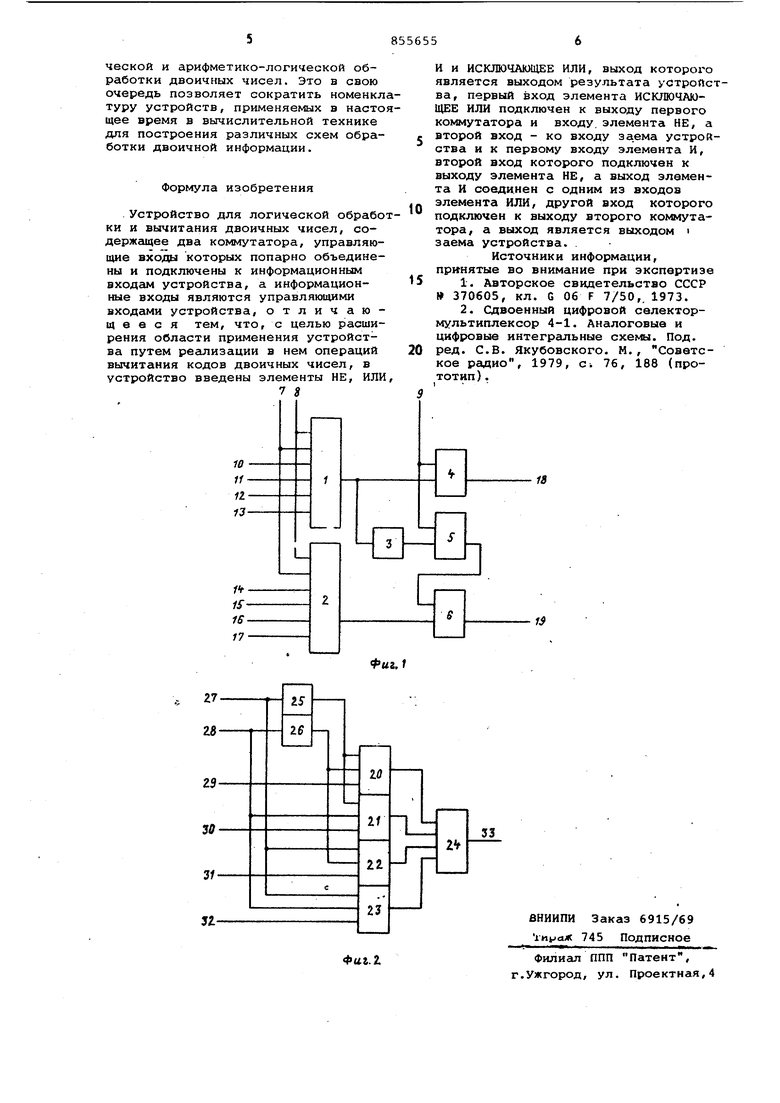

На фиг.1 представлена схема устойства, на фиг.2 - схема коммутатора.

Устройство содержит коммутаторы 1 и , элемент НЕ 3, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элемент И 5, элемент ИЛИ 6, информационные входы 7-9, управляющие входы 10-17, выход 18 результата и выход 19 заема. Коммутатор содержит элементы И 20-23, элемент ИЛИ 24, элементы НЕ 25 и 26, управляющие входы 27 и 28, информационные входы 29-32 и выход 33. В устройстве управляющие входы коммутаторов 1 и 2 попарно объединены и подключены к информационным входам 7 и 8 устройства, а их информационные входы подключены к управляющим входам 10-17 устройства. Выход коммутатора 1 соединен со входом элемента НЕ 3 и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 подключен к выходу 18 устройства, а вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 соединен с первым входом элемента И 5 и подключен к информационному входу 9 устройства. Второй вход элемента И 5 соединен с выходом элемента НЕ 3, а его выход соединен со входом элемента ИЛИ 6, другой вход которого соединен с выходом коммутатора 2, а выход - подключен к выходу 19 устройства.

Устройство работает следующим

образом.

На информационные входы 7 и 8

устройства поступгиот двоичные переменные А и В, а на вход 9 - входной сигнгш заема 3. С выхода 18 устройства снимается сигнал Р результата логической или арифметической операции, а с выхода 19 - выходной сигнал эаема 3g,,x-Ha управляющие входы 10-17 устройства подаются сигналы настройки с помощьюкоторых коммутаторы 1 и 2 настраиваются на реализгщию логических функций переменных А и В таким образом, что логическая функция, регшизуемая коммутатором 1, соответствует.промежуточному результату требуемой математической операции без учета входного сигнала Звх а логическая функция, реализуемая коммутатором 2, функции выходного сигнала заема 3nj без учета входного сигнала заема. Получение окончательного результата операции с учетом входного сигнала заема 3 осуществляется с помодью элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4,

а выходной сигнал эаема Jptix учетом входного сигнала заема

элементов НЕ 3, и 5, и ИЛИ 6. Настройка схемы устройства на выполнение требуемой математической операции из набора возможных операций легко находится по таблице истинности операции (этой), составляемой без .учета входного сигнала заема . Например, для математической операции А - (A,BVAB), которая входит в набор реализуемых операций, имеем безучета входного сигнала заема следующую таблицу истинности

Для реализации в устройстве заданной операции необходимо коммутатор 1 настроить на выполнение логической функции Р А-ВУА В, а коммутатор 2 - на выполнение логической функции 3gbix А-В. Для настроки коммутаторов на соответствующие логические функции достаточно двоичный код функции сигнала из таблицы истинности подать на управляющие входы 10-13 устройства в качестве сигналов настройки , а двоичный код функции сигнала 3,, - на входы 14-17 устройства в качестве сигналов настройки И5-Ид. Если используется элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, то коммутатор 1 должен настраиваться на функцию инверсии сигнала Р. Окончательный результат операции Р Зру , а получаемый сигнал заема Звых 3,.

Путем настройки коммутаторов 1 и 2 на реализацию различных логических функций переменных А и В в устройстве возможно выполнение следующего набора различных математических операций: всех логических операций переменных А и В, арифметичес1 их операций вйчитания: А - В, А --В Л - В, А - В, В - А, В - А, В - А, В - А, операций типа (А,В) FJ (А,в), представляющих собой математические операции одновременного вычисления произвольных логических функций (А/в) и (A,B), переменных Аи В и получением арифметической разности значений этих функций.

В целом устройство реализует 256 различных математических операций, что расширяет его область применения в вычислительной технике и позволяет использовать его не только для построения устройств логической обработки двоичных кодов, но и для построения устройств арифметической и арифметико-логической обработки двоичных чисел. Это в свою очередь позволяет сократить номенкл туру устройств, применяемых в насто щее время в вычислительной технике для построения различных схем обработки двоичной информации. Формула изобретения Устройство для логической обрабо ки и вычитания двоичных чисел, содержащее два коммутатора, управляющие входы которых попарно объединены и подключены к информационным входам устройства, а информационные входы являются управляющими входами устройства, отличающееся тем, что, с целью расширения области применения устройства путем регшизации в нем операций вычитания кодов двоичных чисел, а устройство введены элементы НЕ, ИЛИ и и ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом результата устройства, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к выходу первого коммутатора и входу, элемента НЕ, а второй вход - ко входу за.ема устройства и к первому входу элемента И, второй вход которого подключен к выходу элемента НЕ, а выход элемен та И соединен с одним из входов элемента ИЛИ, другой вход которого подключен к выходу второго коммутатора, а выход является выходом заема устройства. . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 370605, кл. G Об F 7/50,. 1973. 2.Сдвоенный цифровой селектормультиплексор 4-1. Аналоговые и цифровые интегральные схемы. Под. ред. С.В. Якубовского. М., Советское радио, 1979, с. 76, 188 (прототип }.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для арифметической илОгичЕСКОй ОбРАбОТКи дВОичНыХчиСЕл | 1979 |

|

SU842795A1 |

| Устройство для арифметической и логической обработки двоичных и двоично-десятичных @ -разрядных чисел | 1980 |

|

SU962922A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Логическое запоминающее устройство | 1982 |

|

SU1024988A1 |

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Накапливающий сумматор | 1979 |

|

SU920708A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для сортировки чисел | 1979 |

|

SU881735A1 |

Авторы

Даты

1981-08-15—Публикация

1979-12-06—Подача