(54) УПРАВЛЯЕМЫЙ АРИФ1МЕТИЧЕСКИЙ .МОДУЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1978 |

|

SU840881A1 |

| Управляемый арифметический модуль | 1979 |

|

SU855654A1 |

| Арифметическое устройство | 1989 |

|

SU1635172A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для арифметической и логической обработки двоичных и двоично-десятичных @ -разрядных чисел | 1980 |

|

SU962922A1 |

| Управляемый арифметический модуль | 1988 |

|

SU1585792A2 |

| Арифметическо-логическое устройство | 1979 |

|

SU822180A1 |

| Управляемый арифметический модуль | 1980 |

|

SU903865A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1405049A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

1

Изобретение относится к вычислительной технике и может использоваться при построении различных узлов и устройств ЭВМ.

Известен управляемый арифметический модуль, содержащий триггер, элементы И,ИЛИ и НЕ, управляющие и информационные входы и выходы, и предназначенный для арифметической и логической обработки двоичных чисел, и хранения и сдвигов 1

Однако функциональная ограниченность и сложность этого устройства не позволяют реализовать в нем выполнение операций над обратными кодами операндов.

Наиболее близким техническим решением к изобрета.шю является управляемый арифметический модуль,. содержащий элементы И, ИЛИ,триггер, причем перЬые входы первого и второго элементов И соединены между собой и являются входом переноса модуля, первый вход третьего элемента И соединен с вторым входом второго элемента И, а второй вход третьего элемента И является входом управления сложением модуля, выходы первого и второго элементов И соединены с входами элемента ИЛИ, выход которого

является выходом переноса модуля 2. Модуль содержит кроме того элементы НЕ.

Целью изобретения является расширение функциональных возможностей за счет выполнения сложения чисел в обратном коде.

Достигается это тем, что в модуль введены два коммутатора и два элемен0та равнозначность, причем управляющие входы первого коммутатора, первые входы первого и второго элементов равнозначность, информационные входы второго коммутатора являются управ5ляющими входами модуля, информационные входы первого коммутатора являются информационными входами модуля, вторые входы первого и второго элементов равнозначность соединенных

0 соответственно с выходом первого коммутатора и с выходом триггера, выход которого является выходом модуля, выходы первого и второго элементов равнозначность соединены с первым и

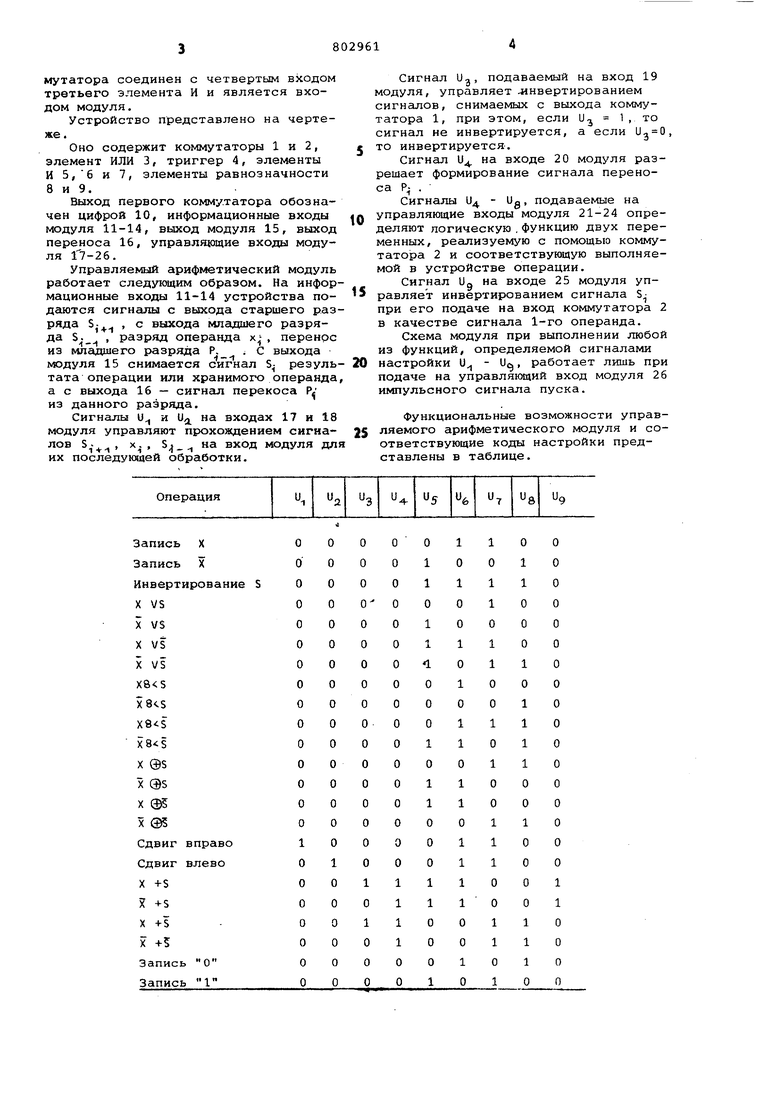

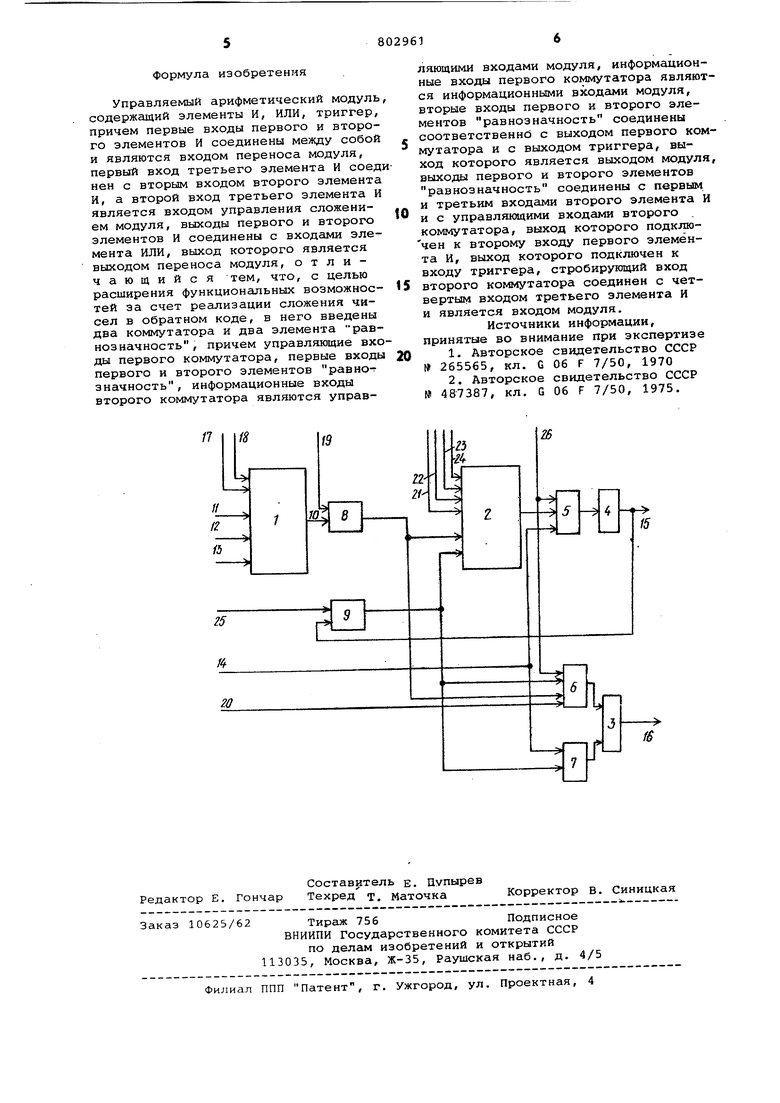

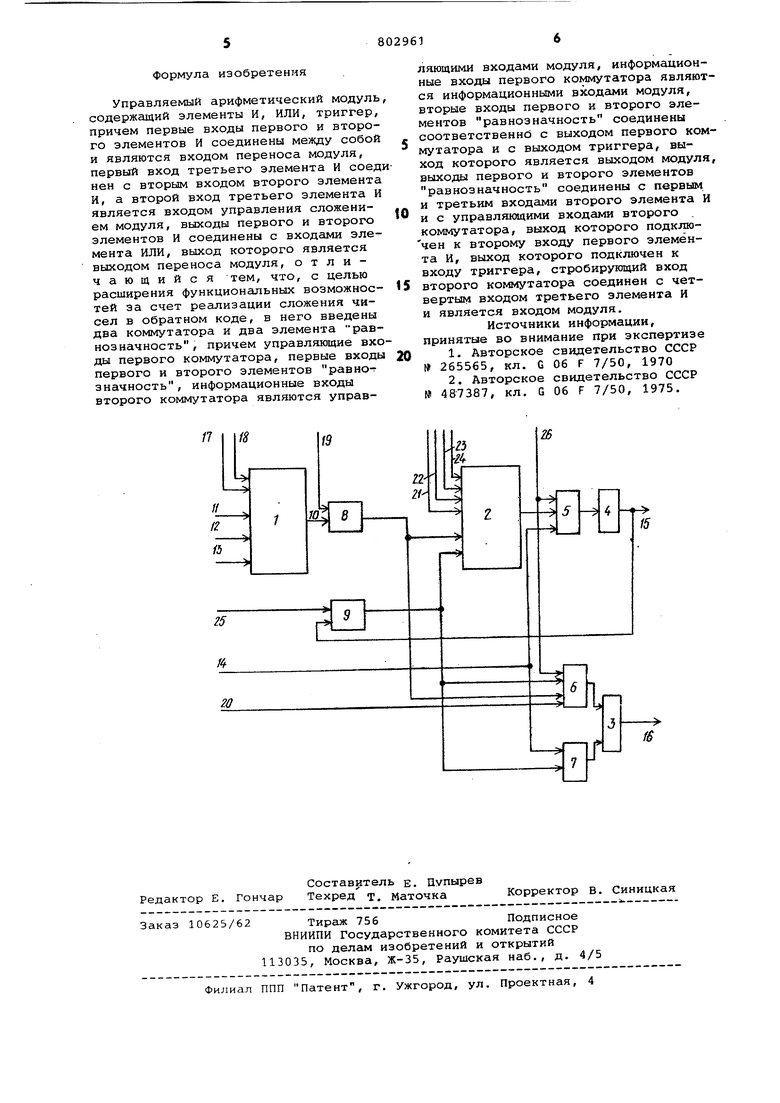

5 третьим входами второго элемента И и с управляющими входами второго коммутатора, выход которого подключен к второму входу первого элемента И, а его выход подк.)1ючег к ихолу трш0гера, стробирующи вход BTOIXH-O коммутатора соединен с четвертьвд входом третьего элемента И и является входом модуля. Устройство представлено на чертеже. Оно содержит коммутаторы 1 и 2, элемент ИЛИ 3, триггер 4, элементы И 5,6 и 7, элементы равнозначности 8 и 9. Выход первого коммутатора обозначен цифрой 10, информационные входы модуля 11-14, выход модуля 15, выход переноса 16, управляющие входы модуля Г7-26. Управляемый арифметический модуль работает следующим образом. На инфор мационные входы 11-14 устройства подаются сигналы с выхода старшего раз ряда S- , с выхода младшего разряда S. , разряд операнда х , перенос из младшего разряда Р, .С выхода модуля 15 снимается сигнал 5 резуль тата операции или хранимого операнда а с выхода 16 - сигнал перекоса Р из данного разряда. Сигналы и и U/j на входах 17 и 18 модуля управляют прохождением сигналов 5., х. , S на вход модуля дл их последующей обработки. Сигнал и, подаваемый на вход 19 модуля, управляет инвертированием сигналов, снимаемых с ВЕлхода коммутатора 1, при этом, если U,j 1 , то сигнал не инвертируется, а если 0, то инвертируется. Сигнал Уд. на входе 20 модуля разрешает формирование сигнала переноса Р . Сигналы Уд. Ug, подаваемые на управляющие входы модуля 21-24 определяют логическую .функцию двух переменных, реализуемую с помощью коммутатора 2 и соответствующую выполняемой в устройстве операции. Сигнал Ug на входе 25 модуля управляет инвертированием сигнала S при его подаче на вход коммутатора 2 в качестве сигнала 1-го операнда. Схема модуля при выполнении любой из функций, определяемой сигналами настройки и - Ug, работает лишь при подаче на управляющий вход модуля 26 импульсного сигнала пуска. Функциональные возможности управляемого арифметического модуля и соответствующие коды настройки представлены в таблице. Формула изобретения Управляемый арифметический модуль содержащий элементы И, ИЛИ, триггер, причем первые входы первого и второго элементов И соединены между собой и являются входом переноса модуля, первый вход третьего элемента И соед нен с вторым входом второго элемента И, а второй вход третьего элемента И является входом управления сложением модуля, выходы первого и второго элементов И соединены с входами элемента ИЛИ, выход которого является выходом переноса модуля, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации сложения чисел в обратном коде, в него введены два коммутатора и два элемента равнозначность, причем управляющие вхо ды первого коммутатора, первые входы первого и второго элементов равно-т значность, информационные входы второго коммутатора являются управляющими входами модуля, информационные входы первого коммутатора являются информационными входами модуля, вторые входы первого и второго элементов равнозначность соединены соответственно с выходом первого коммутатора и с выходом триггера, выход которого является выходом модуля, выходы первого и второго элементов равнозначность соединены с первым и третьим входами второго элемента И и с управляющими входами второго коммутатора, выход которого подключен к второму входу первого элемента И, выход которого подключен к входу триггера, стробирующий вход второго коммутатора соединен с четвертым входом третьего элемента И и является входом модуля. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 265565, кл. G 06 F 7/50, 1970 2.Авторское свидетельство СССР 487387, кл. G 06 F 7/50, 1975.

Авторы

Даты

1981-02-07—Публикация

1978-11-10—Подача