Изобретение относится к вычислительной технике и может быть использовано для организации регенерации информации в динамических запоминающих устройствах.

Известно устройство для регенерации инфордмации, содержаш,ее триггеры режима и регенерации, коммутатор адресов, счетчик адресов регенерации, генератор импульсов регенерации 1.

Устройство позволяет периодически производить регенерацию во всех ячейках динамической памяти, однако характеризуется невысоким быстродействием, обусловленным необходимостью регенерации информации даже в тех модулях памяти, которые не используются в работе.

Наиболее близким по технической сущности и схемно.му рещению к предлагаемому является устройство для регенерации инфор.мации, содержащее ком.мутатор, триггеры режимов и регенерации, счетчик адресов регенерации, генератор импульсов и позволяющее производить регенерацию информации с различной периодичностью во всех ячейках динамической памяти 2.

Недостатком устройства является невысокое быстродействие, обусловленное необходи.мостью регенерации информации даже в тех модулях памяти, которые не используются.

Иель изобретения - повышение быстродействия за счет уменьщения вре.мени на регенерацию в загю.минающем устройстве с зоной свободной памяти.

Иоставленная цель достигается тем, что динамическое запоминающее устройство с зонами свободной памяти, содержащее первый ко.ммутатор, выходы которого являются адресными выходами устройства, триггер режимов, первый выход которого соединен с управляющим входом первого коммутатора, а второй выход является управляюи1им выходом устройства, первый вход триггера режимов соединен с выходом триггера регенерации, а второй вход является первы.м управляющим входом устройства, первый вход триггера регенерации является вторы.м управляющим входом устройства, счетчик адресов регенерации, вход которого соединен с вторы.м входо.м триггера регенерации, входы первой группы первого коммутатора являются адресны.ми входами устройства, генератор импульсов, выход которого соединен с вторым входо.м триггера регенерации, еодержит преобразователь кода и второй ком.мутатор, входы которого являются дополните.льными управляющими входами устройства, а выходы соединены с входами первой группы преобразователя кода и управляющими входами генератора импу.льсов, выходы счетчика адресов соединены с входами второй группы преобразователя кода, информационные выходы которого соединены с входами второй группы первого ко.ммутатора, а управляющий

ВЫХОД соединен с установочным входом счетчика адресов.

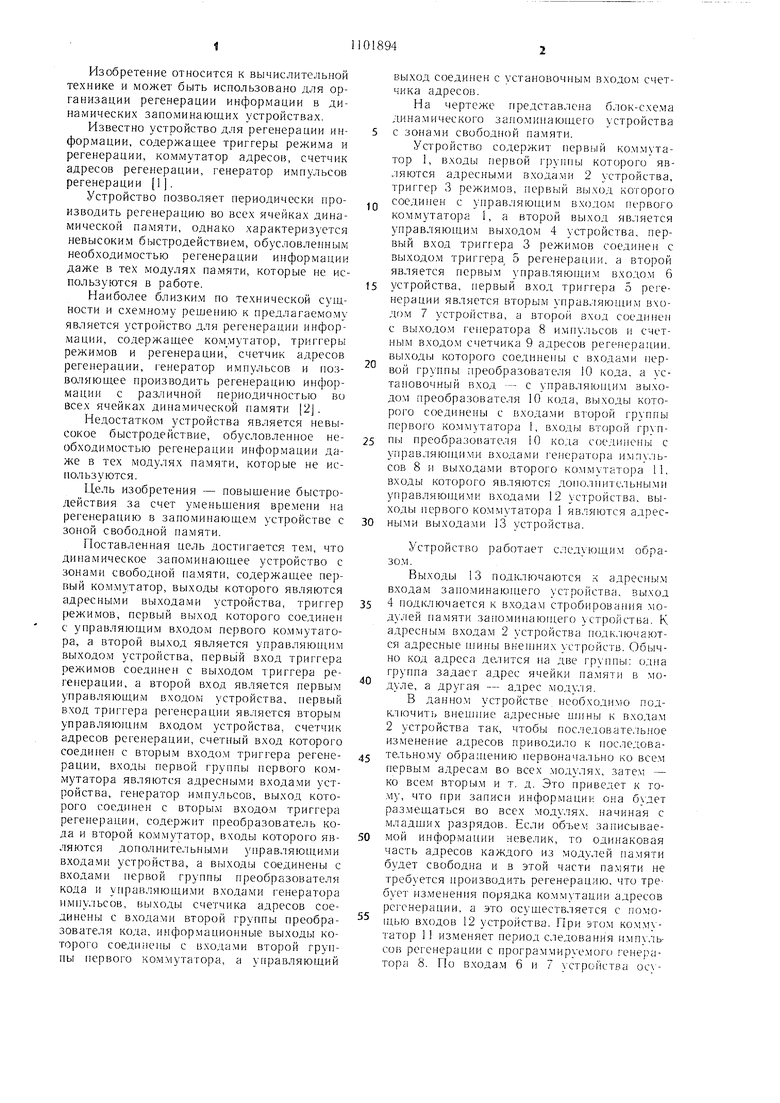

На чертеже представ;1ена блок-схе.ма динамического зано.минающего устройства с зонами свободной памяти.

Устройство содержит перв1,1Й ко.ммутатор 1, входы первой rpyinibi которого являются адресны.ми входами 2 устройства, триггер 3 режимов, первый выход которого соединен с управляющим входом первого коммутатора 1, а второй выход яв:1яется управляюп1им выходом 4 устройства, первый вход триггера 3 режимов соединен с выходо.м триггера 5 регенерации, а второй является первым управляющим входо.м 6 устройства, иервый вход триггера 5 регенерации является вторым праБляющим входом 7 устройства, а второй вход соединен с выходо.м генератора 8 импульсов и счетным входом счетчика 9 адресов peгeflepaции. выходы которого соединены с входа.ми первой группы преобразователя 10 кода, а установочный вход - с управляющим выходом преобразователя 10 кода, выходы которого соединены с входами второй группы первого ко.ммутатора 1, входы второй гр ппы преобразовате,1я 10 кода соедипещз с управ;1яюпдими входами генератора HNirnvibсов 8 и выходами второго ко.ммутатора 11, входы которого являются дополнительны.ми управляющи.ми входами 12 устройства, выходы первого коммутатора 1 являются адресными выхода.ми 13 устройства.

Устройство работает следующим образом.

Выходы 13 подключаются к адресны.м входам запо.минающего устройства, выход 4 подключается к входа.м стробирования модулей памяти запоминающего устройства. К адресны.м входа.м 2 устройства 11одк,1юча.ются адресные гнины устройств. Обычно код адреса делится на две группы: o.:uia группа задает адрес ячейки па.мяти в модуле, а другая - адрес .

В данно.м устройстве необходимо подключить внешние адресные тины к входа.м 2 устройства так, чтобы последовате,лы1ое изменерще адресов приводило к последовательному обращению первонача,пьно ко все.м первы.м адреса.м во всех .модулях, зате.м - ко всем вторы.м и т. д. Это приведет к тому, что при записи информации она будет раз.мещаться во всех .модулях, начиная с младщих разрядов. Если объе.м записываемой инфор.мапии невелик, то одинаковая часть адресов каждого из модулей памяти будет свободна и в этой части па.мяти не требуетея нроизвод.чть регенерацию, что требует изменения порядка коммутации адресов регенерации, а это осуществляется с помоп ью входов 12 устройства. При этом ко.м.татор 11 изменяет период следования имп льсов регенерации с программир е.мого генератора 8. Но входа.м 6 и 7 ттройства ос ществлястся ооргииение к устройству и сорос регенерации.

Счетчик 9 в режиме регенерации обеспечивает последовате;1ьный перебор адресов. подлежа цих регенерации, начиная с младших. При достижении адреса, устанавл 1вае.мого с помощью ко.м.мутатора II, преобразователь 10 вырабатывает на управляющем выходе сигнал сброса счетчика 9 в исходное состояние. Это означает, что регенерация будет произведена только в части .младци х разрядов всех модулей памяти, т. е. в тех адресах, где была записана информация. В режиме обраи1ения коммутатор 1 перек.1ючается на коммутацию адресных сигналов с входа 2 устройства.

Технико-экономическое преимущество предлагаемого стройства заключается в уменьшении времени, отводимого для регенерации инфор.мации, поскольку регенерация ячеек на.мяти, в которых информация не была записана, не производится. Это повьинает быстродействие устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Устройство для вывода графической информации | 1984 |

|

SU1169010A1 |

| Устройство для ввода информации | 1986 |

|

SU1381522A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1984 |

|

SU1234871A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1065884A1 |

| Устройство для ввода информации | 1987 |

|

SU1529208A1 |

| Устройство для отображения информации | 1986 |

|

SU1388941A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ЗОНАМИ СВОБОДНОЙ ПАМЯТИ, содержащее первый коммутатор, выходы которого являются адресными выходами устройства, триггер режимов, первый выход которого соединен с управляющим входом первого коммутатора, а второйВЫХОД является управляющим выходом устройства, первый вход триггера режимов соединен с выходом триггера регенерации, а второй вход является первым управляющим входом устройства, первый вход триггера регенерации является вторым управляющим входом устройства, счетчик адресов регенерации, счетный вход которого соединен со вторым входом триггера регенерации, входы первой группы первого коммутатора являются адресными входами устройства, генератор импульсов, выход которого соединен с вторым входом триггера регенерации, отличающееся тем, что, с целью повыщения быстродействия, оно содержит преобразователь кода и второй коммутатор, входы которого являются дополнительными управляющими входами устройства, а выходы соединены с входами первой группы преобразователя кода и управляющими входами генератора импульсов, ходы счетчика адресов соединены с входасл ми второй группы преобразователя кода, информационные выходы которого соединены с входами второй группы первого коммутатора, а управляющий выход соединен с установочным входом счетчика адресов. 7J 00 со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающие устройства | |||

| Под ред | |||

| Л | |||

| П | |||

| Крайзмера | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3796998, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1984-07-07—Публикация

1982-12-09—Подача