Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на

микросхемах динагиической памяти.

Цель изобретения - повышение быстродействия устройства.

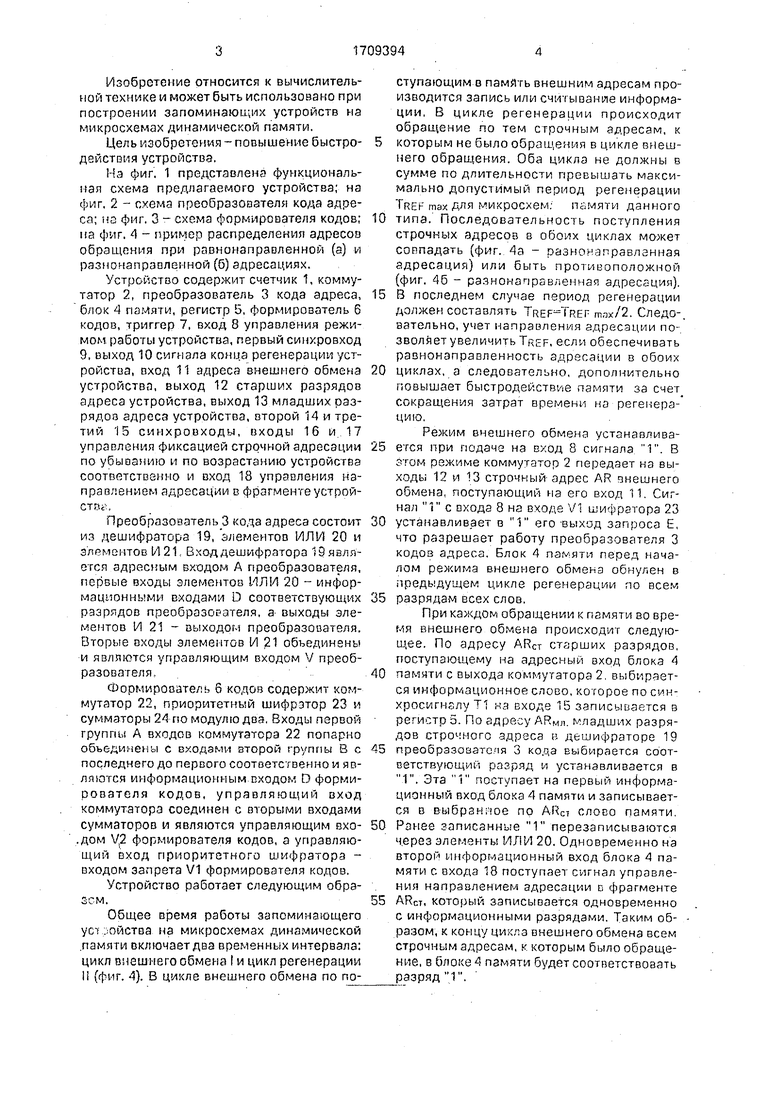

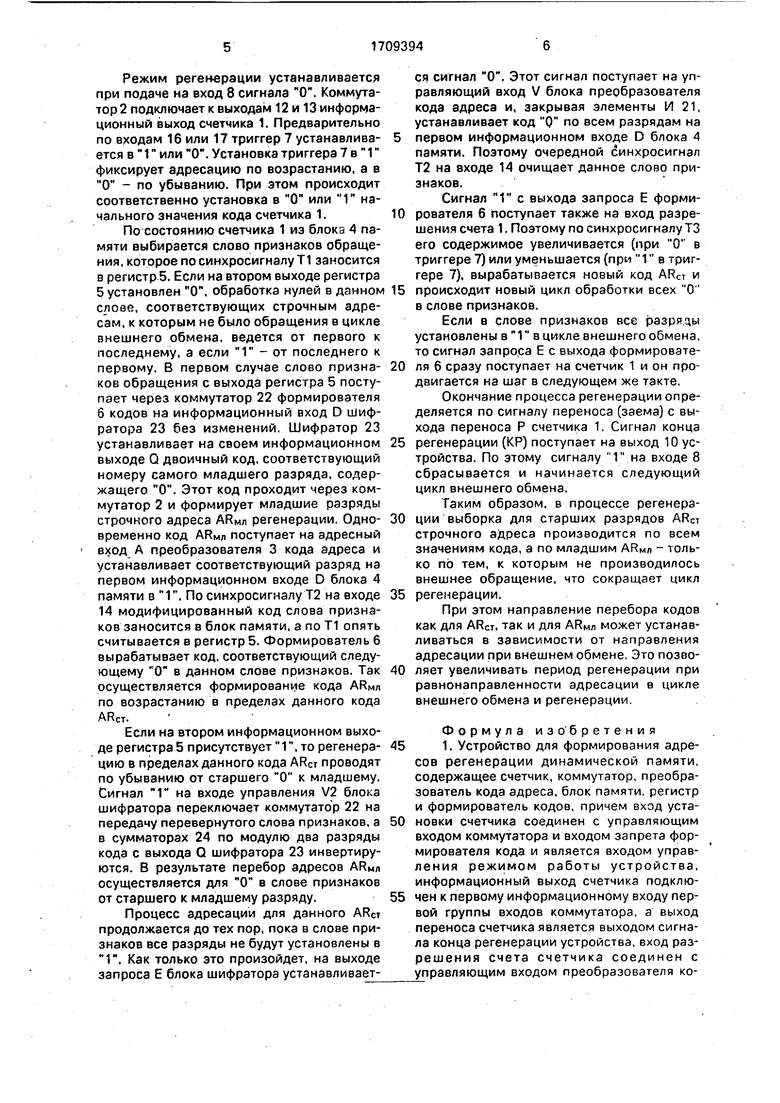

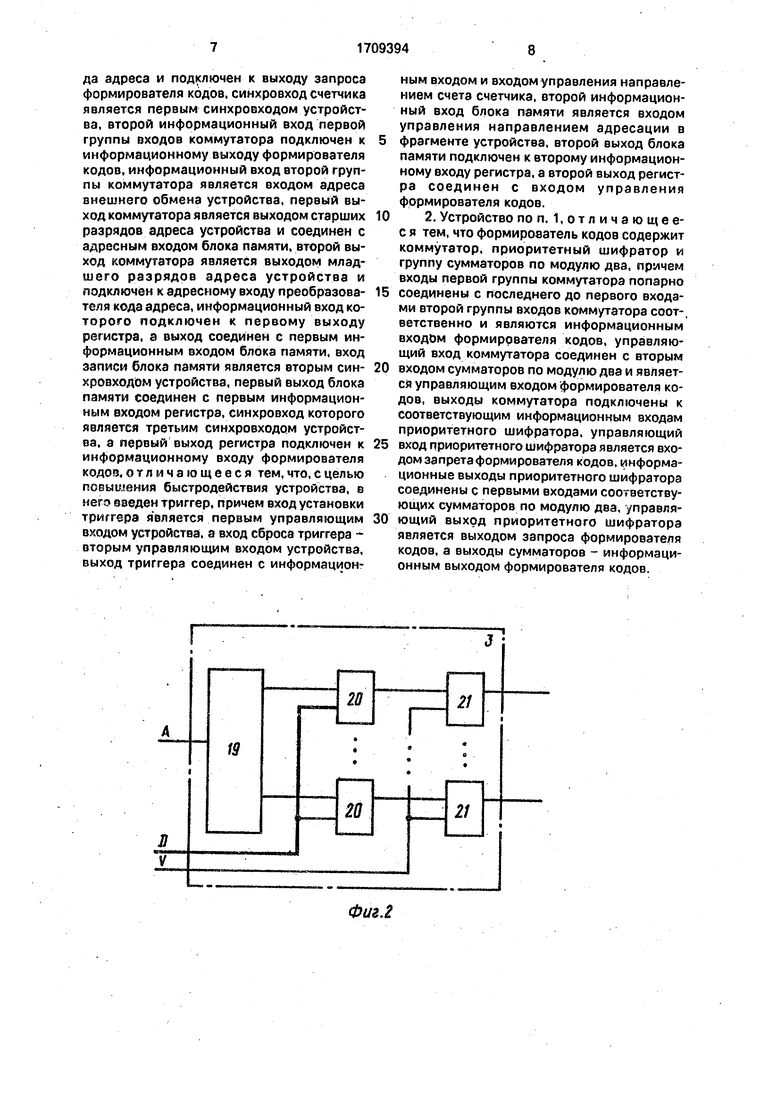

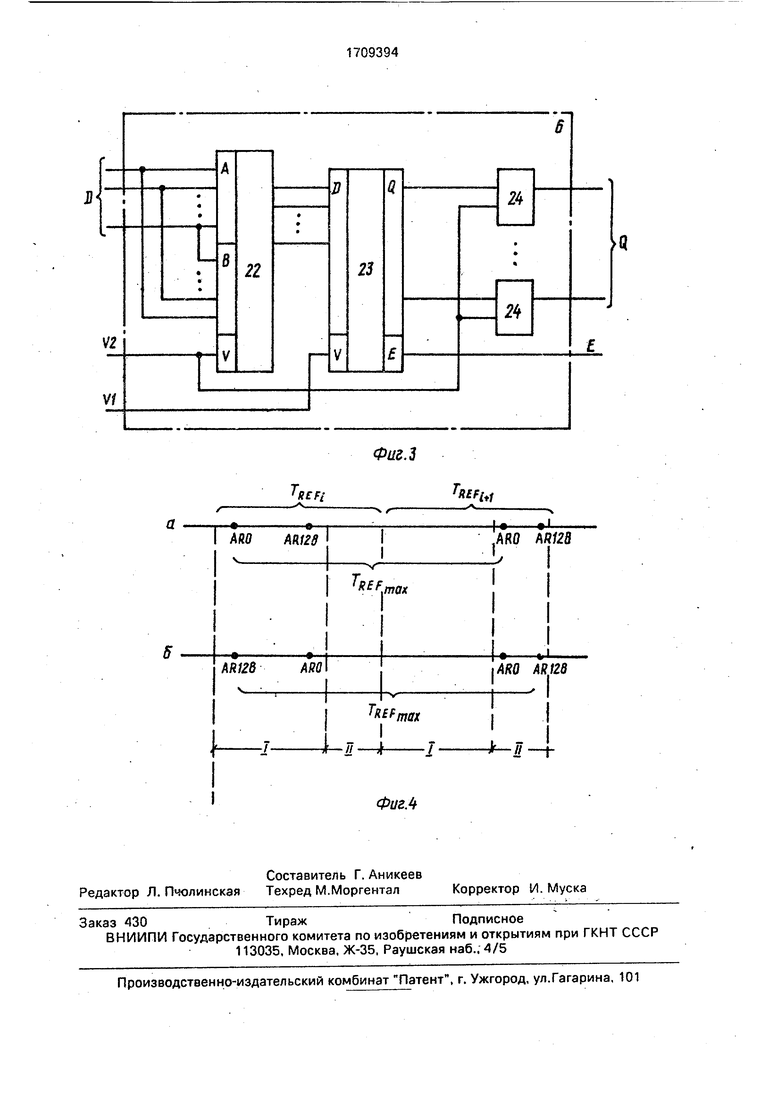

Нэ фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - схема преобразователя кода адреса; из фиг. 3 - схема формирователя кодов; на фмг. 4 - пример распределения адресоа обращения при равнонаправленно.й (а) и разнонаправленной (б) адресациях.

Устройство содержит счетчик 1, коммутатор 2, преобразователь 3 кода адреса, блок 4 памяти, регистр 5, формирователь б кодов, триггер 7, вход 8 управления режимом работы устройства, первый синхровход 9, выход 10 сигнала конца регенерации устройства, вход 11 адреса внешнего обмена устройства, выход 12 старших разрядов адреса устройства, выход 13 младших разрядов адреса устройства, второй 14 и третий 15 синхровходы, входы 16 и 17 управления фиксацией строчной адресации по убыванию и по возрастанию устройства соответственно и вход 18 управления направлением адресации в фрагменте устройстве

Преобразователь 3 ко. адреса состоит из дешифратора 19, элементов ИЛИ 20 и элементов И 21, Вход дешифратора 19 является адресным входом А преобразователя, первые входы элементов ИЛИ 20 - информационными входами О соответствующих разрядов преобразователя, а выходы элементов И 21 - выходом преобразователя. РЗторые входы элементов И 21 объединены и являются управляющим входом V преобразователя.

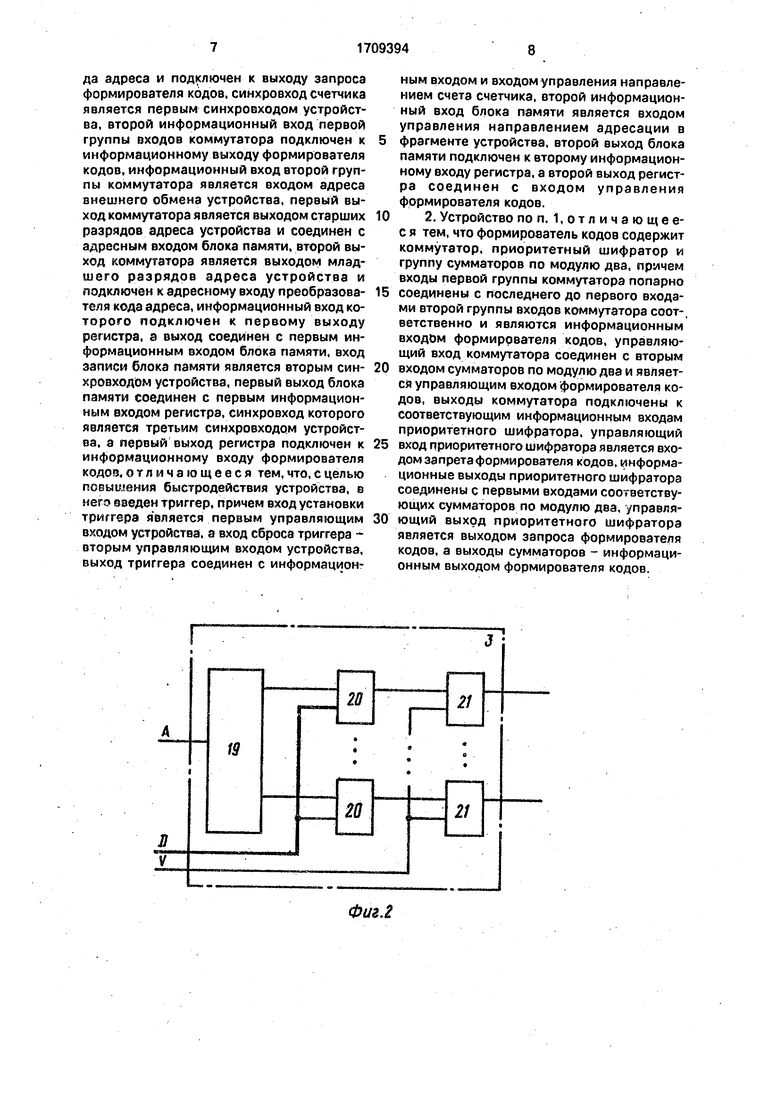

Формирователь 6 кодов содержит коммутатор 22, приоритетный шифратор 23 и сумматоры 24 по модулю два. Входы первой группы А входов коммутатора 22 попарно объединены с входами второй группы В с последнего до первого соотоетственно и являются информационным входом D формирователя кодов, управляющий вход коммутатора соединен с вторыми входами сумматоров и являются управляющим вхо.дом у2 формирователя кодов, а управляющий вход приоритетного шифратора входом запрета V1 формирователя кодов.

Устройство работает следующим образом.

Общее работы запоминающего yof .гюйства на микросхемах динамической .памяти включает два временных интервала: цикл внешнего обмена I и цикл регенерации I (фиг. 4). В цикле внешнего обмена по поступающим в память внешним адресам производится запись или считывание информации, В цикл-е регенерации происходит обращение по тем строчным адресам, к

которым не было обраш,ения в цикле внешнего обращения. Оба цикла не должны в сумме по длительности превышать максимально допустимый период регенерации TREF max для микросхем; памяти данного

0 типа. Последовательность поступления строчных адресов в обоих циклах может совпадать (фиг., 4а - разнонаправланная адресация) или быть противоположной (фиг. 46 - разнонагфавленная адресация).

5 В последнем случае период регенерации должен составлять 7рЕР Тр.ЕР т.-)х/2. Следе-, аательно, учет направления адресации позволяет увеличить TREF, если обеспечивать равнонаправленность адресации в обоих

0 циклах, а следовательно, дополнительно повышает быстродействие памяти за счет сокращения затрат времени на регенерацию.

Режим внешнего обмена устанавливается при подаче на вход 8 сигнала. 1. В этом режиме коммутатор 2 передает на выходы 12 и 13 строчныйадрес AR внешнего обмена, поступающий на его вход 11, Сигнал 1 с входа 8 на входе V1 шифратора 23

0 устанавливает в 1 его выход запроса Е, что разрешает работу преобразователя 3 кодов адреса. Блок 4 памяти перед началом режима внешнего обмена обнулен в предыдущем цикле регенерации по всем

5 разрядам всех слов.

При каждом обращении к памяти во время внешнего обмена происходит следующее. По адресу ARcr старших разрядов, поступающему на адресный вход блока 4

0 памяти с выхода коммутатора 2, выбирается информационное слово, которое по синхросигналу Т1 ка входе 15 записывается в регистр 5. По адресу АВмл. младших разрядов строчного адреса в дешифраторе 19

5 преобрэзоаате.пя 3 кода выбирается соответствуЮЩий разряд и устанавливается в 1. Эта 1 поступает на первый информационный вход блока 4 памяти и записывается в в-ыбранйое по ARci слово памяти,

0 Ранее записанные 1 перезаписываются через элементы ИЛИ 20. Одновременно на второй информационный вход блока 4 памяти с входа 18 поступает сигнал управления направлением адресации с фрагменте

5 ARcT, который зaпиcыDaetcя одновременно с информационными разрядами. Таким образом, к концу цикла внешнего обмена всем строчным адресам, к которым было обращение, в блоке 4 памяти будет соответствовать разряд 1.

Режим регенерации устанавливается при подаче на вход 8 сигнала О. Коммутатор 2 подключает к выходам 12 и 13 информационный выход счетчика 1. Предварительно по входам 16 или 17 триггер 7 устанавливается в Г или О. Установка триггера 7 в Г фиксирует адресацию по возрастанию, а в О - по убыванию. При этом происходит соответственно установка в О или 1 начального значения кода счетчика 1.

По состоянию счетчика 1 из блока 4 памяти выбирается слово признаков обращения, которое по синхросигналу Т1 заносится в регистрб. Если на втором выходе регистра

5установлен О, обработка нулей в данном слоае, соответствующих строчным адресам, к которым не было обращения в цикле внешнего обмена, ведется от первого к последнему, а если 1 - от последнего к первому. В первом случае слово признаков обращения с выхода регистра 5 поступает через коммутатор 22 формирователя

6кодов на информационный вход D шифратора 23 без изменений. Шифратор 23 устанавливает на своем информационном выходе Q двоичный код, соответствующий номеру самого младшего разряда, содержащего О. Этот код проходит через коммутатор 2 и формирует младшие разряды строчного адреса АРмл регенерации. Одновременно код АРмл поступает на адресный вход А преобразователя 3 кода адреса и устанавливает соответствующий разряд на первом информационном входе D блока 4 памяти в 1. По синхросигналу Т2 на входе 14 модифицированный код слова признаков заносится в блок памяти, а по Т1 опять считывается в регистр 5. Формирователь б вырабатывает код, соответствующий следующему О в данном слове признаков. Так осуществляется формирование кода АЯмл

по возрастанию в пределах данного кода ARcT.

Если на втором информационном выходе регистра 5 присутствует 1, то регенерацию в пределах данного кода АНст проводят по убыванию от старшего О к младшему. Сигнал 1 на входе управления V2 блока шифратора переключает коммутатор 22 на передачу перевернутого слова признаков, а в сумматорах 24 по модулю два разряды кода с выхода Q шифратора 23 инвертируются. В результате перебор адресов ARMn осуществляется для О в слове признаков от старшего к младшему разряду.

Процесс адресации для данного АРст продолжается до тех пор, пока в слове признаков все разряды не будут установлены в 1. Как только зто произойдет, на выходе запроса Е блока шифратора устанавливается сигнал О. Этот сигнал поступает на управляющий вход V блока преобразователя кода адреса и, закрывая элементы И 21, устанавливает код О по всем разрядам на первом информационном входе D блока 4 памяти. Поэтому очередной Синхросигнал Т2 на входе 14 очищает данное слово признаков.

Сигнал 1 с выхода запроса Е формирователя б поступает также на вход разрешения счета 1. Поэтому по синхросигналу ТЗ его содержимое увеличивается (при О в триггере 7) или уменьшается (при 1 в триггере 7), вырабатывается новый код АРст и происходит новый цикл обработки всех О в слове признаков.

Если в слове признаков все разряды установлены в 1 в цикле внешнего обмена, то сигнал запроса Е с выхода формирователя б сразу поступает на счетчик 1 и он продвигается на шаг в следующем же такте.

Окончание процесса регенерации определяется по сигналу переноса (заема) с выхода переноса Р счетчика 1. Сигнал конца регенерации (КР) поступает на выход 10 устройства. По этому сигналу 1 на входе 8 сбрасывается и начинается следующий цикл внешнего обмена.

Таким образом, в процессе регенерации выборка для старших разрядов АРст строчного адреса производится по всем значениям кода, а по младшим АЯмл - только по тем, к которым не производилось внешнее обращение, что сокращает цикл регенерации.

При этом направление перебора кодов как для АРст, так и для АРмл может устанавливаться в зависимости от направления адресации при внешнем обмене. Это позволяет увеличивать период регенерации при равнонаправленности адресации в цикле внешнего обмена и регенерации.

Формула изобретения 1. Устройство для формирования адресов регенерации динамической памяти, содержащее счетчик, коммутатор, преобразователь кода адреса, блок памяти, регистр и формирователь кодов, причем вход установки счетчика соединен с управляющим входом коммутатора и входом запрета формирователя кода и является входом управления режимом работы устройства, информационный выход счетчика подключен к первому информационному входу первой группы входов коммутатора, а выход переноса счетчика является выходом сигнала конца регенерации устройства, вход разрешения счета счетчика соединен с управляющим входом преобразователя кода адреса и подключен к выходу запроса формирователя кодов, синхровход счетчика является первым синхровходом устройства, второй информационный вход первой группы входов коммутатора подключен к информационному выходу формирователя кодов, информационный вход второй группы коммутатора является входом адреса внешнего обмена устройства, первый выход коммутатора является выходом старших разрядов адреса устройства и соединен с адресным входом блока памяти, второй выход коммутатора является выходом младшего разрядов адреса устройства и подключен к адресному входу преобразователя кода адреса, информационный вход которого подключен к первому выходу регистра, а выход соединен с первым информационным входом блока памяти, вход записи блока памяти является вторым синхровходом устройства, первый выход блока памяти соединен с первым информационным входом регистра, синхровход которого является третьим синхровходом устройства, а первый выход регистра подключен к информационному входу формирователя кодоэ, отличающееся тем, что, с целью повышения быстродействия устройства, в него введен триггер, причем вход установки триггера является первым управляющим входом устройства, а вход сброса триггера вторым управляющим входом устройства, выход триггера соединен с информационным входом и входом управления направлением счета счетчика, второй информационный вход блока памяти является входом управления направлением адресации в фрагменте устройства, второй выход блока памяти подключен к второму информационному входу регистра, а второй выход регистра соединен с входом управления формирователя кодов.

2. Устройство по п. 1,отличающеес я тем, что формирователь кодов содержит коммутатор, приоритетный шифратор и группу сумматоров по модулю два, причем входы первой группы коммутатора попарно соединены с последнего до первого входами второй группы входов коммутатора соот-. ветственно и являются информационным входом формирователя кодов, управляющий вход коммутатора соединен с вторым входом сумматоров по модулю два и является управляющим входом формирователя кодов, выходы коммутатора подключены к соответствующим информационным входам приоритетного шифратора, управляющий вход приоритетного шифратора является входом запрета формирователя кодов, информационные выходы приоритетного шифратора соединены с первыми входами соответствующих сумматоров по модулю два, управляющий выход приоритетного шифратора является выходом запроса формирователя кодов, а выходы сумматоров - информационным выходом формирователя кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1762320A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1388945A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1251183A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для отображения информации на экране телевизионного индикатора | 1989 |

|

SU1647628A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении запоминающих устройств на микросхемах динамической. памяти. Целью изобретения является повы-ЮУБ.П803Р1D9ТЗ ршение быстродействия устройства. Устройство содержит счетчик 1, коммутатор 2, преобразователь 3 кода адреса, блок памяти 4, регистр 5, формирователь кодов 6, триггер 7, вход 8 управления режимом работы, первый синхровход 9, выход 10 сигнала конца регенерации, вход 11 адреса внешнего обмена, выход 12 старших разрядов адреса, выход 13 младших разрядов адреса, второй 14 и третий 15 синхровходы, входы 16, 17 управления фиксацией строчной адресации по убыванию и возрастанию, вход 18 управления направлением адресации в фрагменте. Быстродействие устройства повышается за счет исключения во время регенерации формирования строчных адресов, к которым было обращение в режиме внешнего обмена, а также за счет учета направления адресации при внешнем обмене и регенерации. 1 з.п. ф-лы, 4 ил.11ARARCT_ J2АКмлJ38D5MКРЮ^Оюсо юfb.

0яг.5

| Устройство для управления регенерацией информации в динамической памяти | 1987 |

|

SU1471224A1 |

Авторы

Даты

1992-01-30—Публикация

1989-12-05—Подача