Изобретение относится к вычислительвой технике и может быть использовано при гтостроении запоминающих устройств (ЗУ) на динамических микросхемах памяти. Известно запоминающее устройство с самоконтролем, в котором диагностика и локализация неисправных блоков выполняются программными средствами 1. Недостатком данного устройства является то, что оно не обеспечивает глубины диагностирования с точностью до любого функционального узла. Наиболее близким к предлагаемому является запоминающее устройство с самоконтролем, содержащее накопители, умощнители, приемники информации, первый и второй передатчики информации, регистры информации, адреса и ощибок, первые элементы сложения по модулю два, счетчики цикла и адресов регенерации, селектор адреса, генератор импульсов, первый триггер и блок управления, первый вход которого подключен к первому выходу счетчика циклов регенерации, второй вход - к первому выходу генератора импульсов, третий вход - к первому управляющему входу устройства, а первые выходы - к первым входам умощнителей, вторые входы которых подключены к выходам селектора адреса, первые входы которого подключены к выходам счетчика адресов регенерации, а вторые входы - к.выходам регистра адреса, входы которого подключены к адресным входам устройства, информационные шины которого подключены к выходам первого и второго передатчиков информации и входам приемника информации, выходы которого подключены к информационным входам соответствующих накопителей, адресные и управляющие входы которых подключены к выходам соответствующих умощнителей и входам соответствующих первых элементов сложения по модулю два, а выходы - к соответствующим входам регистра информации, выходы которого подключены к входам первого передатчика информации, а входы второго передатчика информации - к выходам регистра ощибок, первые входы которого подключены к выходам соответствующих первых элементов сложения по модулю два 2. Недостатком известного устройства является то, что оно не обеспечивает глубину диагностирования, необходимую для локализации неисправности таких функциональных блоков, как счетчик циклов регенерации, счетчик адресов регенерации и блок управления, что затрудняет поиск места Неисправностей, увеличивает время восстановления и, таким образом, снижает Надежность устройства. Цель изобретения - повышение надежности устройства путем увеличения глубины диагностирования. Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопители, усилители, выходной регистр, блоки ввода информации, блоки вывода информации, регистр адреса, регистр ощибок, группу сумматоров по модулю два, первый генератор импульсов счетчик циклов регенерации, счетчик адресов регенерации, первый селектор, первый триггер и блок управления, первый вход которого подключен к одному из выходов счетчика циклов регенерации, второй вход - к первому выходу первого генератора импульсов, а одни из выходов - к первым входам усилителей, вторые входы которых соединены с выходами первого селектора, одни из входов которого подключены к выходам счетчика адресов регенерации, а другие входы - к выходам регистра адреса причем выходы блоков ввода информации соединены с информационными входа.ми на выходы усилителей подключены копителей к входам сумматоров по модулю два групги:) и адресным и управляющим входа.м накопителей, выходы которых соединены с входами выходного регистра, выходы которого подключены к входам первого блока вывода информации, выходы сум.маторов по модулю два группы соединены с первыми .информационными входами регистра ошибок, зы ходы которого подключены к входам второго блока вывода информации, третий вход блока управления -является входом обращения устройства, введены второй генератор импульсов, блок сравнения, сумматор г;о модулю два, второй и третий се/;;.кторы, счетчик ошибок, второй триггер, элемент задержки и элемент ИЛИ, причем второй выход первого генератора импульсов по; ключен к первому входу второго селектора, выход которого соединен со счетным входом счетчика циклов регенерации, один из выходов которого подключен к перво.му входу третьего селектора, а другие выходы соединены с одними из входов блока сравнения, выход и другие входы которого подключены соответственно к второму информационному входу регистра ошибок к к выходам счетчика адресов регенерации, установочный вход которого соединен с установочным входом счетчика циклов регенерации и выходом второго генератора импульсов, а счетный вход - с выходом третьего селектора, вторые входы второго и третьего селекторов подключенык третьему входу блока управления, одни из выходов которого соединены с в.ходами сумматора по модули два, выход которого подключен к информационному входу второго триггера, вход синхронизации и инверсный выход которого соединены соответственно с первым выходом первого Ieнератора импульсов и с входе:,, элемента задержки, выход которого подключен к vcтановочному входу второго триггера, нрямой выход которого соединен со счетным входом счетчика ошибок, устаковочный вход и выходы которого подключены соответственно к другому выходу блока управления и к входам элемента ИЛИ, выход которого соединен с информационным входом первого триггера, выход которого подключен к третьему информационному входу регистра ошибок, установочные входы первого триггера и регистра ошибок, третьи входы второго и третьего селекторов и вход второго генератора импульсов объединены и являются управляющим входом устройства.

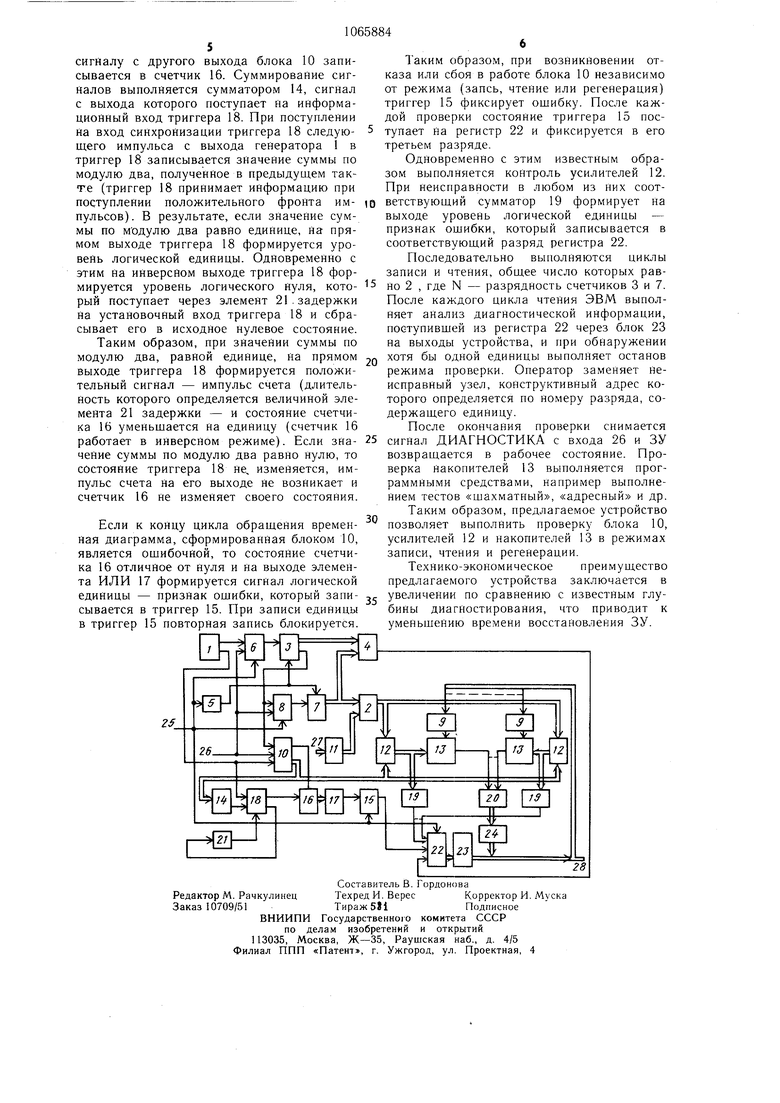

На чертеже показана структурная схема предлагаемого устройства.

Устройство содержит первый генератор импульсов, первый селектор 2, счетчик 3 циклов регенерации, блок 4 сравнения, второй генератор 5 импульсов, второй селектор 6, счетчик 7 адресов регенерации, третий селектор 8, блоки 9 ввода информации, блок 10 управления, регистр ; адреса, усилите;1и 12, накопители 13, сум.матор 14 по модулю два, первый триггер 15, счетчик 16 ошибок, элемент ИЛИ 17, второй Т1:иггер 18, группу сумматоров 19 по модулю два, выходной регистр 20, элемент 21 задержки, регистр 22 ошибок, а также первый 23 и второй 24 блоки вы1К)да информации.

На чертеже обозначены управляющий вход 25, вход 26 обращения, а также адресные 27 и информационные 28 входы устройства.

Иредлагаемое устройство работает следующим образом.

В режимах записи или чтения устройство работает обычным образом. При обращении на вход 26 поступает сигнал «Обращение для возбуждения работы блока 10, а на вход 27 - код адреса адресуемой ячейки, который фиксируется в регистре 11.

Код адреса с выхода регистра 11 поступает через селектор 2 на вторые входы усилите«1ей 12, которые посылают его на адресные входы соответствующих накопителей 13. Записываемая информация поступает на ЭВМ по входам 28 на входы блоков 9, которые передают ее на информационные входы соответствующих накопителей 13. При этом блоки 23 и 24 переводятся в состояние, не искажаюпхее значение сигналов на входах 28. Далее блок 10 формирует сигналы временной диаграммы записи, которые поступают через первые входы усилителей 12 на управляющие входы соответствующих накопителей 13.

В режиме чтения блок 23 остается в прежнем состоянии, а информация, считанная из накопителей 13, поступает на регистр 20 и передается блоком 24 на выходы устройства и далее в ЭВМ. Сигналы, необходимые

для выполнения цикла чтения, формируются блоком 10 и передаются в пакопители 3 аналогично сигна,пам временной диаграммы режима записи.

5 Устройство периодически выполняет циклы регенерации хранимой информации. Регенерация выполняется каждый раз при формировании счетчиком 3 на один из его выходов сигнала начала регенерации. Счет- чик 3 работает от импульсов, поступающих на его счетный вход с выхода генератора 1 через селектор 6. Код адреса регенерируемой ячейки формируется счетчиком 7 и поступает через селектор 2 па входы усилителей 12 и далее на адресные входы соответст5 вующих накопителей 13. Состояние счетчика 7 увеличивается каждый раз на единицу при поступлении на его счетный вход сигнала начала регене|,ацпи с вы.хода селектора 2.

Формирование управляющих сигналов

для любого режима работы на выходе блока 10 выполняется под действием импульсов, поступающих на его вход с выхода генератора 1.

В режиме проверки (самоконтроля) на

5 вход 25 поступает на ЭВМ (не показана) сигнал «Диагностика, который переводит блоки ЗУ в исходное состояние, а именно снимает блокировку с установочных входов триггера 15 и регистра 22, находящихся в нулевом состоянии, разрешает прохожде0 ние сигналов с входа 26 на выходы селекторов 6 и 8, а также поступает па вход генератора 5, который формирует импульс сброса, поступающий на установочные входы счетчиков 3 и 7 и устанавливающий их в нулевое состояние.

5 Далее ЭВМ организует обычные циклы обращения к устройству.

Ири этом сигнал «Обра1пение входа 26 через се,текторы 6 и 8 посгхпает па счетные входы С етчиков 3 и 7 я увеличи0 вает их состояние на единицу. Сигналы с выходов счетчиков 3 и 7 поступают соответственно на входы блока 4, который выполняет сравнение состояниг.й счетчиков 3 и 7 и в случае несовпадения формирует из выходе сигнал логической единицы ---

5 нак ошибки, который поступает па вход регистра 22 и записывается в него. При совпадении в данный разряд регис1ра 22 записывается ноль - признак отсутствия о:пибок.

Одновременно с этим выполняется проверка работоспособности блока 10 и усилителей 12. Учитывая, что управляющие сигналы на одних выходов блока 10 могут изменяться только при поступленпи импульсов с выхода генератора 1, проверка бло5 ка 10 выполняется подсчетом числа тактов генератора 1, в которых сумма но модулю два всех сигналов на одних из выходов блока 10 равна единице. Данное число по

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для управления памятью | 1980 |

|

SU962963A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059630A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для контроля матриц памяти на цилиндрических магнитных пленках с неразрушающим считыванием информации | 1986 |

|

SU1387045A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накопители, усилители, выходной регистр, блоки ввода информации, блоки вывода информации, регистр адреса, регистр ошибок, группу сумматоров по модулю два, первый генератор импульсов, счетчик циклов регенерации, счетчик адресов регенерации, первый селектор, первый триггер и блок управления, первый вход которого подключен к одному из выходов счетчика циклов регенерации, второй вход - к первому выходу первого генератора импульсов, а одни из выходов - к первым входам усилителей, вторые входы которых соединены с выходами первого селектора, одни из входов которого подключены к выхрдам счетчика адресов регенерации, а другие входы - к выходам регистра адреса, причем выходы блоков ввода информации соединены с информационными входами Накопителей, выходы усилителей подключены к входам сумматоров по модулю два группы и адресным и управляющим входам накопителей, выходы которых соединены с входами выходного регистра, выходы которого подключены к входам первого блока вывода информации, выходы сумматоров по модулю два группы соединены с первыми информационными входами регистра ощибок, выходы которого подключены к входам второго блока вывода информации, третий вход блока управления является входом обращения устройства, отличающееся тем, что, с целью повышения его надежности путем увеличения глубины диагностирования, в него введены второй генератор импульсов, блок сравнения, сумматор по модулю два, второй и третий селекторы, счетчик ошибок, второй триггер, элемент задержки и элемент ИЛИ, причем второй выход первого генератора импульсов подключен к первому входу второго селектора, выход которого соединен со счетным входом счетчика циклов регенерации. Один из выходов которого подключен к первому входу третьего селектора, а другие выходы соединены с одними из входов блока сравнения, выход и другие входы которого подключены соответственно к второму информационному входу регистра ошибок и к выходам счетчика адресов регенерации, установочный вход которого соединен с ус тановочным входом счетчика циклов регенерации и выходом второго генератора им(Л пульсов, а счетный вход - с выходом третьего селектора, вторые входы второго и третьего селекторов подключены к третьему входу блока управления, одни из выходов которого соединены с входами сумматора по модулю два, выход которого подключен к информационному входу второго триггера, вход синхронизации и инверсный выход которого соединены соответственно с первым выходом первого генератора имOi пульсов и с входом элемента задержки, выел ход которого подключен к установочному входу второго триггера, прямой выход ко00 00 4 торого соединен со счетным входом счетчика ошибок, установочный вход и выходы которого подключены соответственно к другому выходу блока управления и к входам элемента ИЛИ, выход которого соединен с информационным входом первого триггера, выход которого подключен к третьему информационному входу регистра ошибок, установочные входы первого триггера и регистра ошибок, третьи входы второго и третьего селекторов и вход второго генератора импульсов объединены и являются управляющим входом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения угла в системах числового программного управления | 1987 |

|

SU1495749A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3944800, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1984-01-07—Публикация

1982-08-24—Подача