(Л

со

00

ел ГС N5

10

Изобретение относится к вычислительной технике и может быть использовано в качестве многоканального устройства ввода информации в системы обработки.

Целью изобретения является повышение надежности устройства.

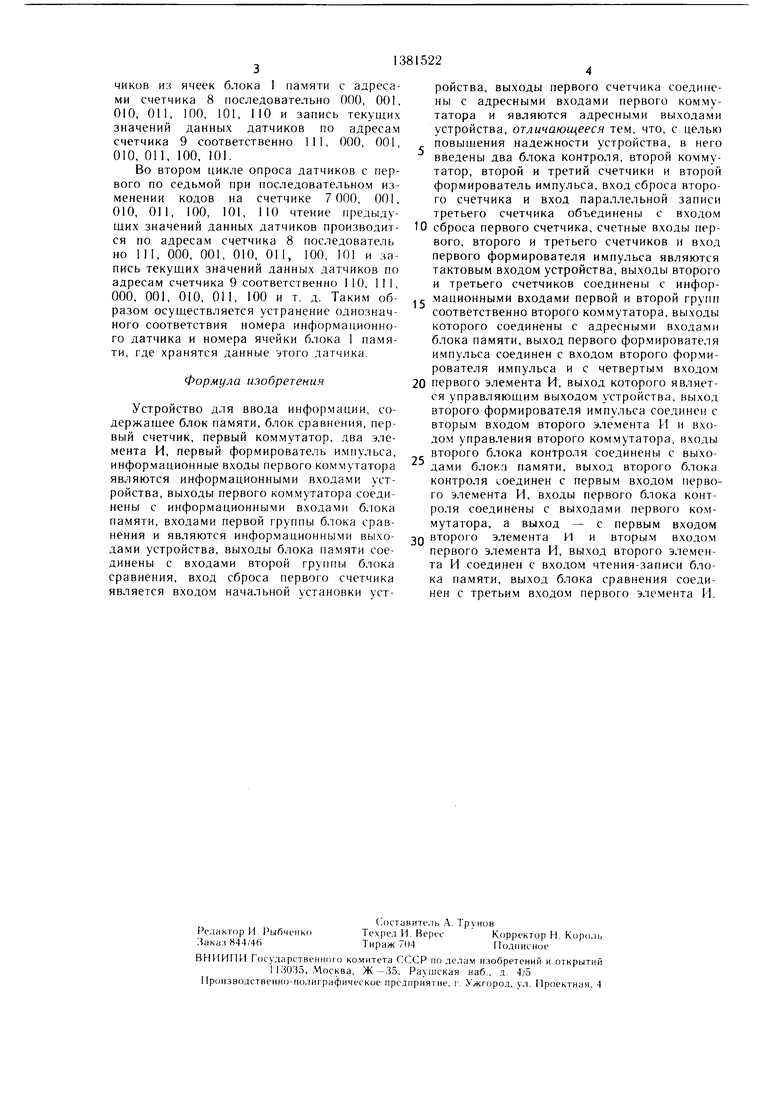

На чертеже приведена функциональная схема устройства.

Устройство содержит блок 1 памяти, блок 2 сравнения, первый 3 и второй 4 блоки контроля, первый 5 и второй 6 коммутаторы, первый 7, второй 8 и третий 9 счетчики, первый 10 и второй 11 элементы И, первый 12 и второй 13 фор.мирователи импу. 1ь- са, входы 14-16 и выходы 17 - 19 устройства.

В качестве блоков 3, 4 контроля могут быть использованы сумматоры но .модулю два.

Счетчик 7 является счетчиком по модулю М. где Л - количество инфор. ных входов коммутатора 5. Счетчики 8 и 9 являются счетчиками по модулю Р, где Р - информационная емкость блока 1 па.мяти в словах. Причем .

Устройство работает следующим образом.

Перед началом работы сигналом по входу 25 16 установки счетчики 7 и 8 устанавливаются в нулевое состояние, а счетчик 9 устанавливается (в счетчик заносится код) в состояние М. Во время начальной установки сигналы на входе 15 управления должны отсутствовать.

После начальной установки устройство готово к опросу информационных датчиков с входов 14 устройства, который начинается с приходом синхронизирующего сигнала по входу 15 управления. До момента приновременно информация с выходов коммутатора 5 и блока 1 памяти подается на соответствующие блоки 3 и 4 контроля, которые формируют на своих выходах высо- 5 кие уровни сигналов при наличии достоверных данных.

По переднему фронту синхросигнала на входе 15 устройства формирователь 12 импульса формирует сигнал опроса элемента И 10, на выходе которого появляется сигнал в случае изменения информации от анализируемого датчика и при отсутствии зафиксированных ощибок в данных. Сигнал на выходе 19 устройства является сигналом сопровождения данных, присутствующих на

15 выходах 17, и адресного признака, присутствующего на выходах 18 анализируемого датчика.

По заднему фронту сигнала на выходе формирователя 12 импульса формирователем 13 формируется сигнал, по которому к

20 адресным входам блока 1 па.мяти через ком.мутатор 6 подключаются выходы счетчика 9. Выходной сигнал формирователя 13 импульса опрашивает элемент И 11, выходной сигнал которого производит запись в блок 1 памяти новых данных анализируемого датчика при отсутствии в них 01пиб- ки, зарегистрированной блоко.м 3 контроля. Следует отметить, что для нормальной работы устройства сумма длительностей сигналов формирователей 12 и 13 импуль30 должна быть меныпе длительности синхросигнала по входу 15 устройства.

Задним фронтом сигнала по входу 15 производится модификация содержимого счетчиков 7, 8, 9, т. е. к их содержимому добавляется единица. С приходом

хода первого синхросигнала по входу 15 35 следующего синхросигнала по входу 15

счетчик / находится в нулевом состоянии, соответствующем адресу первого датчика. Через коммутатор 5 информация этого датчика поступает на входы первой группы блока 2 сравнения, на входы второй группы которого поступает информация о предыдущем состоянии первого датчика, считываемая из блока 1 памяти по адресу, сформированно.му на выходах счетчика 8 и подавае.мому на адресные входы блока 1 па40

производится анализ и при необходимости вывод данных очередного датчика приемнику информации.

В первом цикле опроса датчиков при опросе первого датчика при коде 000 счетчика 7 производится чтение предыдущего значения данных первого датчика из ячейки с адресом 000 на счетчике 8 и последующая запись текущего значения данных первого датчика в ячейку с адресом 111 на

мяти через открытый для них коммутатор АС счетчике 9. После этого содержимое счет6. В этом случае низкий уровень сигнала на выходе формирователя 13 импульса обеспечивает режим чтения для блока 1 памяти и подключает к его адресным входам через коммутатор 6 сигналы с выходов счетчика 8.

Блок 2 сравнения сравнивает предыдущее и текуц ее состояния датчика, и если информация от датчика не изменилась по сравнению с его предыдущим состоянием, на выходе блока 2 присутствует низкий

чиков 7, 8, 9 модифицируется. В следующем такте опрос второго датчика производится при коде 001 счетчика 7, чтение предыдущего состояния из ячейки с адресо.м 001 на счетчике 8, запись текуп его состоя- 50 ния второго датчика по адресу 000 на счетчике 9 и модификация содержимого счетчиков 7, 8, 9. В дальнейшем работа устройства аналогична.

Таким образом, в первом цикле опроса датчиков с первого по седьмой при последоуровень сигнала. Если имеет место изме- 55 вательном изменении кодов на счетчике нение информации, на выходе блока 2 ус-7000,001,010,011, 100, 101, 1 10 производится чтение предыдущих значений данных даттанавливается высокий уровень сигнала. Од0

5

новременно информация с выходов коммутатора 5 и блока 1 памяти подается на соответствующие блоки 3 и 4 контроля, которые формируют на своих выходах высо- 5 кие уровни сигналов при наличии достоверных данных.

По переднему фронту синхросигнала на входе 15 устройства формирователь 12 импульса формирует сигнал опроса элемента И 10, на выходе которого появляется сигнал в случае изменения информации от анализируемого датчика и при отсутствии зафиксированных ощибок в данных. Сигнал на выходе 19 устройства является сигналом сопровождения данных, присутствующих на

5 выходах 17, и адресного признака, присутствующего на выходах 18 анализируемого датчика.

По заднему фронту сигнала на выходе формирователя 12 импульса формирователем 13 формируется сигнал, по которому к

0 адресным входам блока 1 па.мяти через ком.мутатор 6 подключаются выходы счетчика 9. Выходной сигнал формирователя 13 импульса опрашивает элемент И 11, выходной сигнал которого производит запись в блок 1 памяти новых данных анализируемого датчика при отсутствии в них 01пиб- ки, зарегистрированной блоко.м 3 контроля. Следует отметить, что для нормальной работы устройства сумма длительностей сигналов формирователей 12 и 13 импуль0 должна быть меныпе длительности синхросигнала по входу 15 устройства.

Задним фронтом сигнала по входу 15 производится модификация содержимого счетчиков 7, 8, 9, т. е. к их содержимому добавляется единица. С приходом

производится анализ и при необходимости вывод данных очередного датчика приемнику информации.

В первом цикле опроса датчиков при опросе первого датчика при коде 000 счетчика 7 производится чтение предыдущего значения данных первого датчика из ячейки с адресом 000 на счетчике 8 и последующая запись текущего значения данных первого датчика в ячейку с адресом 111 на

счетчике 9. После этого содержимое счетчиков 7, 8, 9 модифицируется. В следующем такте опрос второго датчика производится при коде 001 счетчика 7, чтение предыдущего состояния из ячейки с адресо.м 001 на счетчике 8, запись текуп его состоя- 50 ния второго датчика по адресу 000 на счетчике 9 и модификация содержимого счетчиков 7, 8, 9. В дальнейшем работа устройства аналогична.

Таким образом, в первом цикле опроса датчиков с первого по седьмой при последо55 вательном изменении кодов на счетчике 7000,001,010,011, 100, 101, 1 10 производитчиков из ячеек блока 1 памяти с адресами счетчика 8 последовательно 000, 001, 010, 011, 100, 101, 110 и запись текущих значений данных датчиков по адресам счетчика 9 соответственно 111, 000, 001, 010, 011, 100, 101.

Во втором цикле опроса датчиков с первого по седьмой при последовательном изменении кодов на счетчике 7000, 001, 010, 011, 100, 101, 110 чтение предыдущих значений данных датчиков производится но адресам счетчика 8 последователь но 111, 000, 001, 010, 011, 100, 101 и запись текущих значений данных датчиков по адресам счетчика 9 соответственно 110, 111, 000, 001, 010, Oil, 100 и т. д. Таким образом осуществляется устранение однозначного соответствия номера информационного датчика и номера ячейки блока 1 памяти, где хранятся данные этого датчика.

Формула изобретения

Устройство для ввода информации, содержащее блок памяти, блок сравнения, первый счетчик, первый коммутатор, два элемента И, первый формирователь импульса, инфор.мационные входы первого коммутатора являются информационными входами устройства, выходы первого коммутатора соединены с информационными входами блока памяти, входами первой группы блока сравнения и являются информационными выходами устройства, выходы блока памяти соединены с входа.ми второй группы блока сравнения, вход сброса первого счетчика является входом начальной установки устройства, выходы первого счетчика соединены с адресными входами первого коммутатора и являются адресны.ми выходами устройства, отличающееся тем, что, с целью повыщения надежности устройства, в него введены два блока контроля, второй коммутатор, второй и третий счетчики и второй формирователь импульса, вход сброса второго счетчика и вход параллельной записи третьего счетчика объединены с входом

0 сброса первого счетчика, счетные входы первого, второго и третьего счетчиков и вход первого формирователя импульса являются тактовым входом устройства, выходы второго и третьего счетчиков соединены с инфорс- мационными входами первой и второй групп соответственно второго коммутатора, выходы которого соединены с адресными входами блока памяти, выход первого фор.мирователя и.мпульса соединен с входом второго фор.мирователя импульса и с четвертым входом

0 первого элемента И, выход которого является управляющим выходом устройства, выход второго формирователя импульса соединен с вторы.м входом второго элемента И и входом управления второго коммутатора, входы второго блока контроля соединены с выходами блокл памяти, выход второго блока контроля соединен с первым входом первого элемента И, входы первого блока контроля соединены с выходами первого коммутатора, а выход - с первым входом

Q второго элемента И и вторым входом первого элемента И, выход второго элемента И соединен с входом чтения-записи блока памяти, выход блока сравнения соединен с третьим входом первого элемента И.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1987 |

|

SU1442999A2 |

| Устройство для ввода информации | 1987 |

|

SU1472912A1 |

| Устройство управления сортировкой изделий | 1986 |

|

SU1388111A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1423982A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Устройство для сопряжения | 1985 |

|

SU1278861A1 |

| Устройство для записи и анализа циклограмм дискретных блоков | 1985 |

|

SU1313221A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве многоканального устройства ввода информации в системы обработки. Целью изобретения является повышение надежности устройства. Устройство содержит блок 1 памяти, два блока контроля 3 и 4, блок 2 сравнения, два коммутатора 5 и 6, три счетчика 7, 8 и 9, два элемента И 10, 11 и два формирователя импульсов 12 и 13. Цель изобретения достигается за счет уменьшения вероятности потери информации, поскольку устраняется однозначное соответствие между номером информационного датчика и адресом ячейки памяти блока 1, хранящей информацию о его предыдущем состоянии. 1 ил.

| Устройство для ввода информации | 1983 |

|

SU1144101A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1983 |

|

SU1151978A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-07-31—Подача