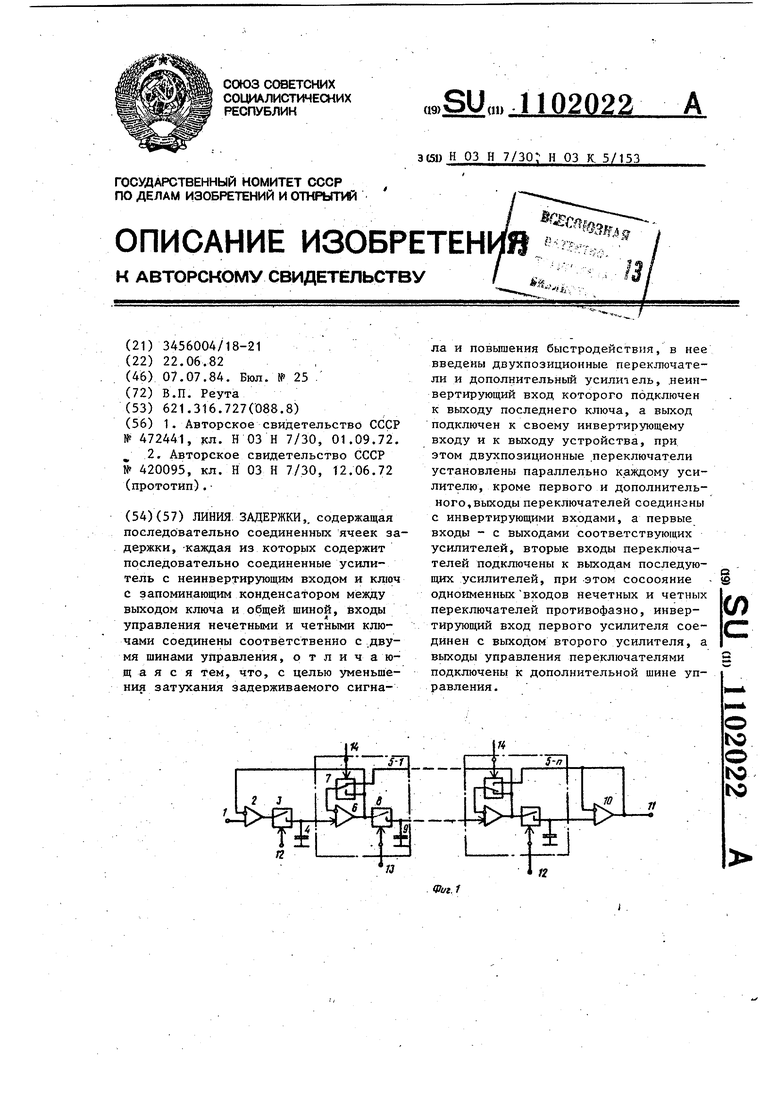

Изобретение относится к устройствам задержки сигнала и может быть использовано в различных областях электроники для управляемой задержки аналоговых сигналов. Известна линия задержки аналоговы сигналов,содержащая последовательно соединенных ячеек задержки, кажда из которых содержит ключ, например, на полевом транзисторе, и кондёнсатор памяти, а также общий для линии задержки выходной повторитель напряжения, а входы управления нечетными и четными ключами подключены соответственно к двум шинам управленияС1 Недостатками известной линии задержки являются низкое быстродействи и значительное затухание сигнала при большом числе ячеек задержки. Обусло лено это тем, что передача сигнала из одной ячейки в другую производится через ключи, обладающие конечньм внутренним сопротивлением, которое, с одной стороны, не позволяет произвести, стопроцентную передачу сигна из одной ячейки в другую, а с другой ограничивает минимальное время передачи этого сигнала. В результате, .чем с большей точностью надо передат задержанньй сигнал,- тем меньше должн быть частота коммутации ключей. Наиболее близкой по технической сущности к предлагаемой является линия задержки, содержащая последовательно соединенных ячеек задержки, каждая из которых содержит последова тельно соединенные неинвертирующий усилитель и ключ с запоминающим конденсатором между выходом ключа и общей шиной, входы управления нечетн ми и четнь ми ключами соединены, соот ветственно с двумя шинами управления а на выходе линии задержки установ- лен повторитель напряжения 2. Недостатками данной линии также являются невысокое быстродействие и значительное затухание сигнала при большом числе ячеек задержки из-за конечного внутреннего сопротивления ключей, что не обеспечивает стопроцентную передачу сигнала из одной ячейки в другую и ограничивает минимальное время передачи этого сигнала Цель изобретения - уменьшение затухания задерживаемого сигнала и повышение быстродействия. Цель достигается тем, что в линию задержки, содержащую последователь но соединенных ячеек задержки, качщая из которых содержит последовательно соединенные усилитель с неинвертирующим входом и ключ с запоминающим конденсатором меткду выходом ключа и общей шиной, входы управления нечетными и четными ключами соединены соответственно с двумя шинами управления, введены двухпозиционные переключатели и дополнительный усилитель, неинвертирующий вход которого подключен к выходу последнего ключа, а выход подключен к своему инвертирующему входу и к выходу устройства, при этом двухпозиционные переключатели установлены параллельно каждому усилителю, кроме первого и дополнительного, выходы переключателей соединены с инвертирующими входами, а первые входы - с выходами соответствующих усилителей, вторые входы переключателей подключены к выходам последующих усилителей, при этом состояние одноименных входов нечетных и четных переключателей противофазно, инвертирующий вход первого усилителя соединен с выходом второго усилителя, а входы управления переключателями подключены к дополнительной шине управления. На фиг. 1 приведена схема линии задержки; на фиг. 2 - условная форма и временное расположение импульсов управления ключами и переключателями. Вход 1 линии задержки соединен с неинвертирующим входом первого усилителя 2, нагруженного через ключ 3 на,запоминающий конденсатор 4. Далее следуют одинаковые по построению ячейки 5-1 - 5-п, конденсатор 4 соединен также с входом первой 5-1 ячейки, содержащей усилитель 6, неинвертирующий вход которого является входом ячейки, а инвертирующий подключен к выходу двухпозиционного переключателя 7 первый вход которого соединен с выходом усилителя бис вторым выходом ячейки 5-1, подключенным к инвертирующему входу усилителя 2, а второй его вход является вторым входом ячейки. Выход усилителя 6 в каждой ячейке подключен через ключ 8 к конденсатору 9 и к первому выходу ячейки. Первый выход и второй вход каждой предыдущей ячейки 5-1 - 5-п соединены соответственно с первым входом вторым выходом последующей ячейки.

Первый выход и второй вход последней ячейки 5-п соединены соответственно с неинвертирующим входом дополнительного усилителя 10 и. с его выходом, объединенным с его инвертирующим входом и с выходом 11 устройства Входы управления нечетными ключами подключены к шине управления 12, входы управления четными ключами подключены к шине управления 13, входы управления переключателями подключены к шине управления 1А.

При работе линии задержки входной (задерживаемый) сигнал подается на вход 1 линии задержки, а задержанный 4 (выходной) сигнал снимается с выхода 11, к которому обычно подключается фильтр (не показан) для восстановления огибающей входного сигнала. Фильтр в общем случае может отсутствовать, например в случае, когда на выходе линии задержки устанавливается аналого-цифровой преобразователь .

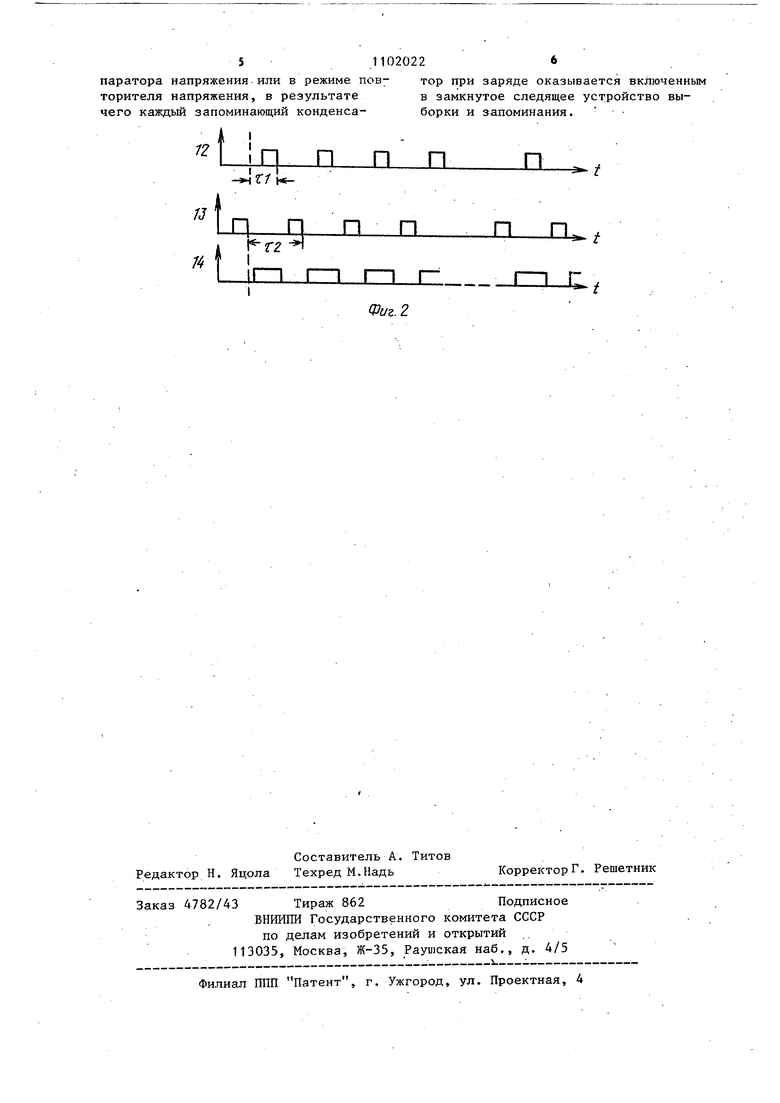

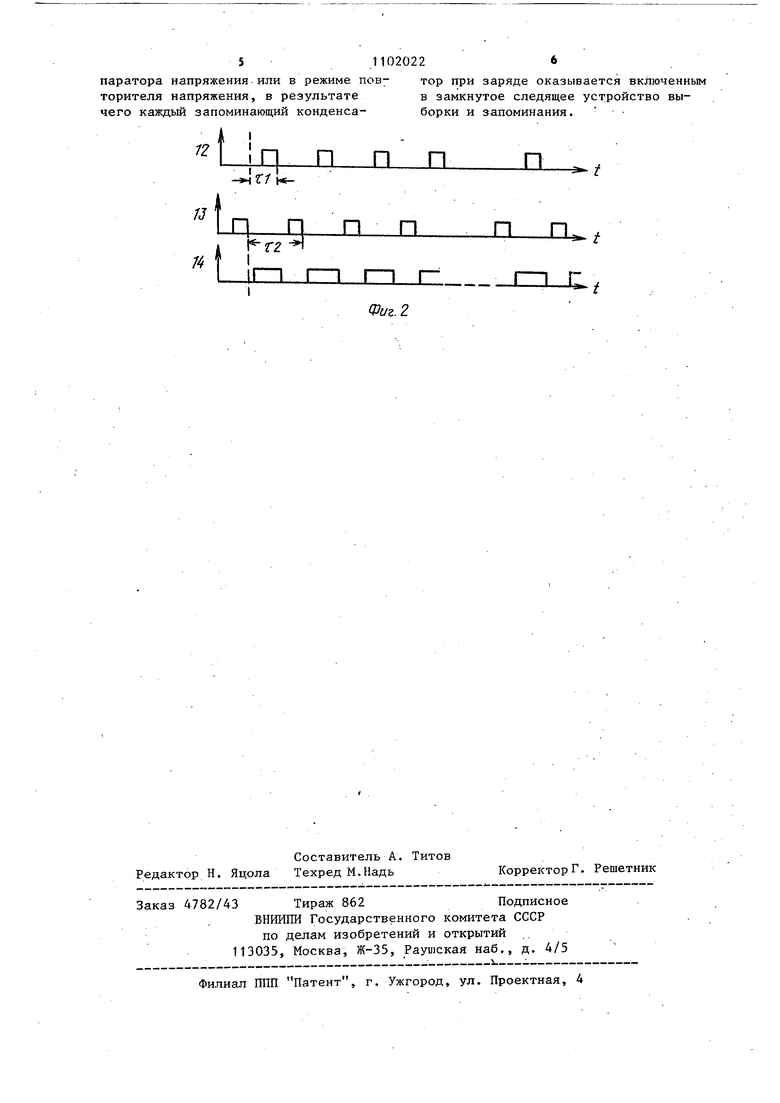

Для работы линии задержки на шины управления 12, 13 и 14 подают от внешнего блока управления (не показан) тактовые импульсы (фиг. 2) где частота следования тактовых импульсов равна

г 1

(О

Га

Входной сигнал с входа 1 через усилитель 2 поступает на разомкнутый ключ 3. При замыкании ключа 3 сигналом с шины 12 к выходу усилителя 2 подключается запоминающий конденсатор 4, который быстро заряжается до амплитуды входного сигнала за счет наличия замкнутой обратной связи через усилитель 6 первой ячейки 5-1, которьш в режиме заряда запоминающего конденсатора 4 работает как повторитель напряжения. Как только напряжение на запоминающем конденсаторе 4 станет равным входному, т.е. на обоих входах усилителя 2 напряжение станет равным друг другу, усилитель 2 прекратит заряд запоминающего конденсатора 4. Затем ключ 3 сигналом с шины 12 будет разомкнут, после чего сигналом с шины 14 переключатель 7 будет переведен в противоположное состояние, в результате чего усилитель 6 из режима повторителя будет переведен в режим компаратора, а его инвертирующий вход будет подключен через переключатель к выходу

усилителя 6 последующей ячейки, у которого в это же время- за счет переключения -переключателя 7 последующей ячейки сигналом с шины 14 выход окажется соединенным с инверТ4 рУ1ощим входом, т.е. усилитель 6 последующей ячейки будет переведен своим переключателем 7 в режим повторителя напряжения . После этого сигналом с шины 13 будет замкнут ключ 8, которьш подключит запоминающий конденсатор 9 к выходу усилителя 6, который быстро зарядит запоминающий конденсатор до напряжения на запоминающем конденсаторе 4 за.счет наличия обратной связи через усилитель 6 последующей ячейки. После этого сначала сигналом с шины 13 разомкнется ключ 8 через время t (фиг. 2), затем сигналом с шины 14 будут возвращены переключатели 7. Через время, равное i; после прихода первого импульса управления по -шине 12, цикл повторится . Все ключи и переключатели работают синхронно (фиг. 1 и фиг.- 2). В итоге время задержки линии задержки составит интервал

т . -Vi-,

(2)

30

при нечетном числе запоминаюп1;их конденсаторов, где п число запоминаюш;их конденсаторов. Если число запоминающих конденсаторов четное,то

35 .

Т (| - П-.р + Сп . (3)

Изменением частоты следовг.ИЯ импуль40 сов управления по шинам 12-14 можно менять общее время задержки при постоянном числе ячеек линии задержки

Пр1,имуществами линии задержки по сравнению с известной являются 45 малое затухание, так как каждый запоминающий конденсатор заряжается до полной амплитуды напряжения на предыдущем конденсаторе или входе линии задержки и высокое быстродействие.

т.е. большая максимальная частота

50 тактовых импульсов, обусловленная мгшым временем заряда запоминающих конденсаторов.

55 Эти преимущества объясняются наличием переключателей, которые позволяют каждый усилитель, кроме первого и последнего, использовать в двух режимах работы - в режиме ком511020226

паратора напряжения.или в режиме пов- тор при заряде оказывается включенным торителя напряжения, в результате в замкнутое следящее устройство вычего каждый запоминающий конденса- борки и запоминания.

12 I

п пп п. .

l I-I г ,

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Дискретно-аналоговая линия задержки | 1980 |

|

SU930583A1 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ДВУХПОЛЮСНИКОВ | 2013 |

|

RU2548594C1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU924755A1 |

| СУММИРУЮЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1972 |

|

SU420095A1 |

| ПОЛОСОВОЙ ФИЛЬТР С УПРАВЛЯЕМОЙ ПОЛОСОЙ ПРОПУСКАНИЯ | 2021 |

|

RU2758448C1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1420537A1 |

| Устройство для спектрального анализа | 1979 |

|

SU1083124A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU888208A1 |

| Дискретно-аналоговая линия задержки | 1976 |

|

SU665393A1 |

ЛИНИЯ. ЗАДЕРЖКИ,, содержащая последовательно соединенных ячеек задержки , -каждая из которых содержит последовательно соединенные усилитель с неинвертирующим входом и ключ с запоминающим конденсатором между выходом ключа и общей шиной, входы управления нечетными и четными ключами соединены соответственно с .двумя шинами управления, о т л и ч а ющ а я с я тем, что, с целью уменьшения затухания задерживаемого сигна -.,чч. ла и повышения быстродействия, в нее введены двухпозиционные переключатели и дополнительный усилит ель, .неинвертирующий вход которого подключен к выходу последнего ключа, а выход подключен к своему инвертирующему входу и к выходу устройства, при этом двухпозиционные .переключатели установлены параллельно каждому усилителю, кроме первого и дополнительного, выходы переключателей соединены с инвертирующими входами, а первые входы - с выходами соответствующих усилителей, вторые входы переключателей подключены к выходам последующих усилителей, при этом сосоояние одноименныхвходов нечетных и четных (Л переключателей противофазно, инвертирующий вход первого усилителя соединен с выходом второго усилителя, а выходы управления переключателями подключены к дополнительной шине управления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Линия задержки аналоговых сигналов | 1972 |

|

SU472441A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| , 2 | |||

| СУММИРУЮЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1972 |

|

SU420095A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-07-07—Публикация

1982-06-22—Подача