(S) ДИСКРЕТНО-АНАЛОГОВАЯ ЛИНИЯ ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Устройство для задержки импульсных сигналов | 1980 |

|

SU921047A1 |

| Дискретно-аналоговая линия задержки | 1976 |

|

SU665393A1 |

| Линия задержки | 1982 |

|

SU1102022A1 |

| Программируемый трансверсальный фильтр | 1980 |

|

SU985938A1 |

| Дискретно-аналоговая линия задержки | 1971 |

|

SU450315A1 |

| БЛОК ПОСТОЯННОГО ЗАПАЗДЫВАНИЯ | 1971 |

|

SU321820A1 |

| Способ регистрации однократных импульсных сигналов наносекундного диапазона | 1974 |

|

SU752401A1 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ДВУХПОЛЮСНИКОВ | 2013 |

|

RU2548594C1 |

| Дифференцирующее устройство | 1982 |

|

SU1051547A1 |

1

Изобретение относится к обработке низкочастотных сигналов и может найти применение для запоминания и задержки сигналов.

Известна дискретно-аналоговая линия задержки, содержащая параллельно включенные запоминающие ячейки, каждая из которых составлена из одного ключа и запоминающего конденсатора, ключи записи и считывания соответственно на входе и выходе дискретно-аналоговой линии задержки и цепи управления, запоминающие ячейки разделены на две группы, одна из которых объединяет все четные, а другая - все нечетные запоминающие ячейки, подсоединенные через соответствующие ключи записи и считывания к входу и выходу устройства, при этом вход управления ключа записи одной группы соединен с входом управления ключа считывания другой группы П1

Однако данная линия задержки имеет недостаточное быстродействие и ограниченные возможности, обусловленные отсутствием отходов линии задержки..

Известна дискретно-аналоговая линия задержки содержащая блок управле ния, ключи записи и считывания и запоминающие ячейки, состоящие из ключа и запоминающего конденсатора,

10 блок преобразования, операционные усилители, подключенные между выходами и входами запоминающих образованных из двух параллельно включенных четных и нечетных запомина 5ющих ячеек, каждая из которых состоит из ключа записи, сигнальный вход которого является входом ячейки, ключа считывания, выход которого является выходом ячейки, и паМраллельно соединенных запоминающего конденсатора и ключа, выход которых подключен к общей шине, а вход - к выходу ключа записи и входу ключа считывания, при этом блок преобразования подключен своим сигнальным входом к источнику сигналов выходом - к входу первого запоминающего звена, дополнительным выходом к йулевому отводу линии задержки и управляющими входами - к дополнительным выходам блока управления, а дополнительные выходы всех операционных усилителей - к соответствующим отводам линии задержки, управляющие входы ключей четных и нечетных запоминающих ячеек подсоединены соответственно к третьему и первому выходам блока управления, управляющие входы ключей записи четных и нечетных запоминающих ячеек - соответственно к четвертому и второму выходам блока управления, управляющие входы ключей считывания четных запоминающих ячее к первому и второму выходам блока уравления, управляющие входы ключей считывания и нечетных запоминающих ячеек - к третьему и четвертому выходам блока управления 2.

Однако эта линия задержки имеет сложную запоминающую ячейку и значительную нестабильность параметров при изменении внешних условий, обусловленную неидеальностью операционных усилителей и ограниченные функциональные возможности.

Целью изобретения является повышение стабильности работы при изменении внешних условий и расширение функциональных возможностей.

Для этой цели в дискретно-аналоговую линию задержки, содержащую устройство управления, соединенное выходами с входами ключа записи и ключей считывания, запоминающие конденсаторы, входы которых подключены к выходам соответствующих им ключей записи и входам ключей считывания, а выходы конденсаторов подключены к общей шине, операционные усилители, выходы которых подключены к- выходны клеммам, входы ключей записи соединены с входной клеммой устройства, введены операционный усилитель, ключи восстановления, конденсаторы хранения, вход введенного операционного усилителя соединен с выходами всех ключей считывания, а его выход с входами всех ключей восстановления, выходы которых соединены с входами соответствущих им конденсатордв хранения и входами операционных

усилителей, выходы конденсаторов содинены с общей шиной, входы управления ключей восстановления соединены с выходами устройства управления, причем входы всех ключей записи соединены между собой.

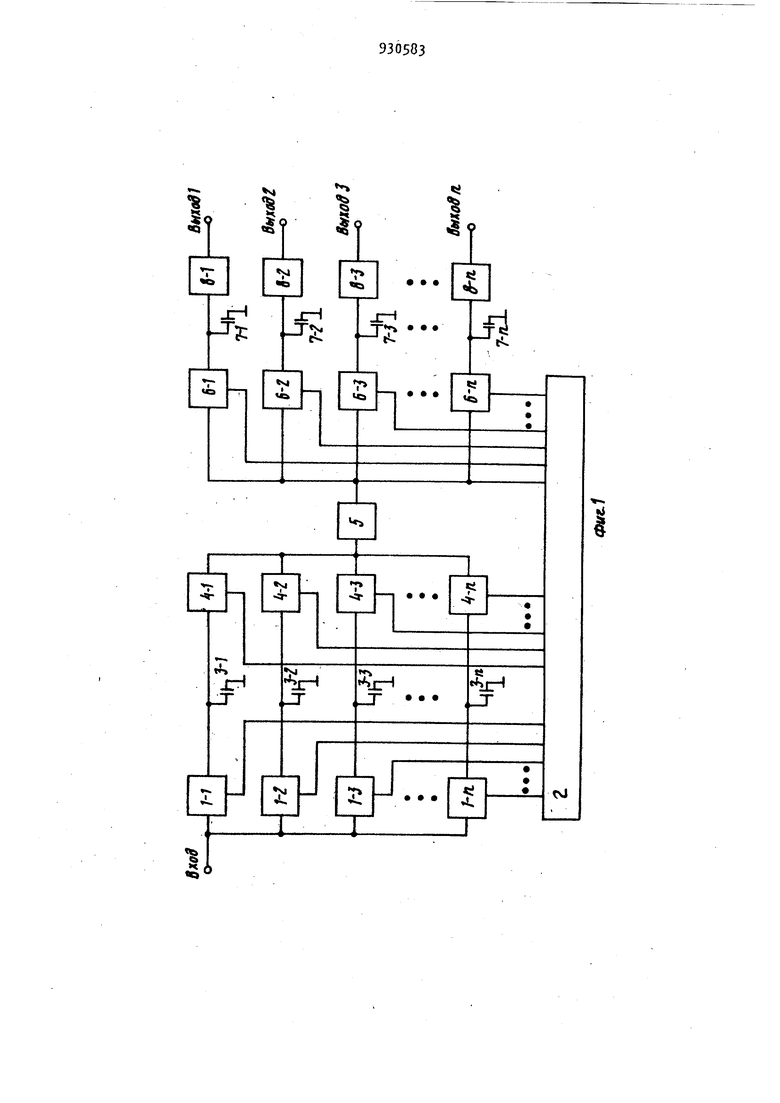

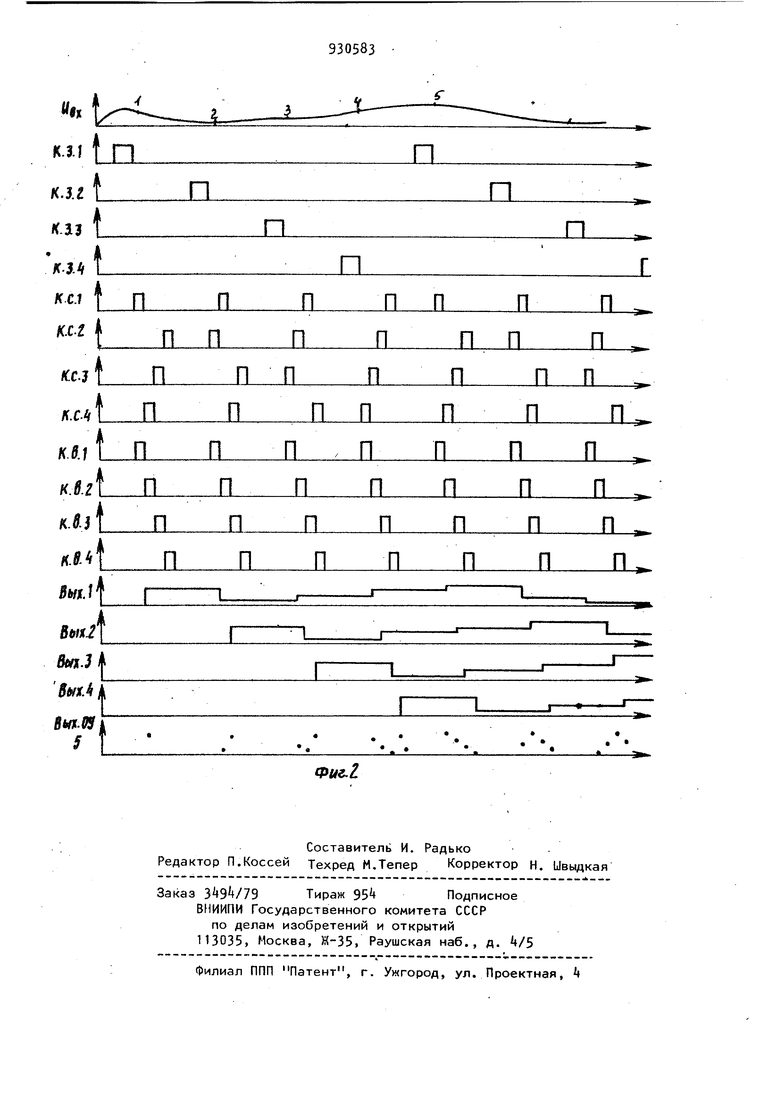

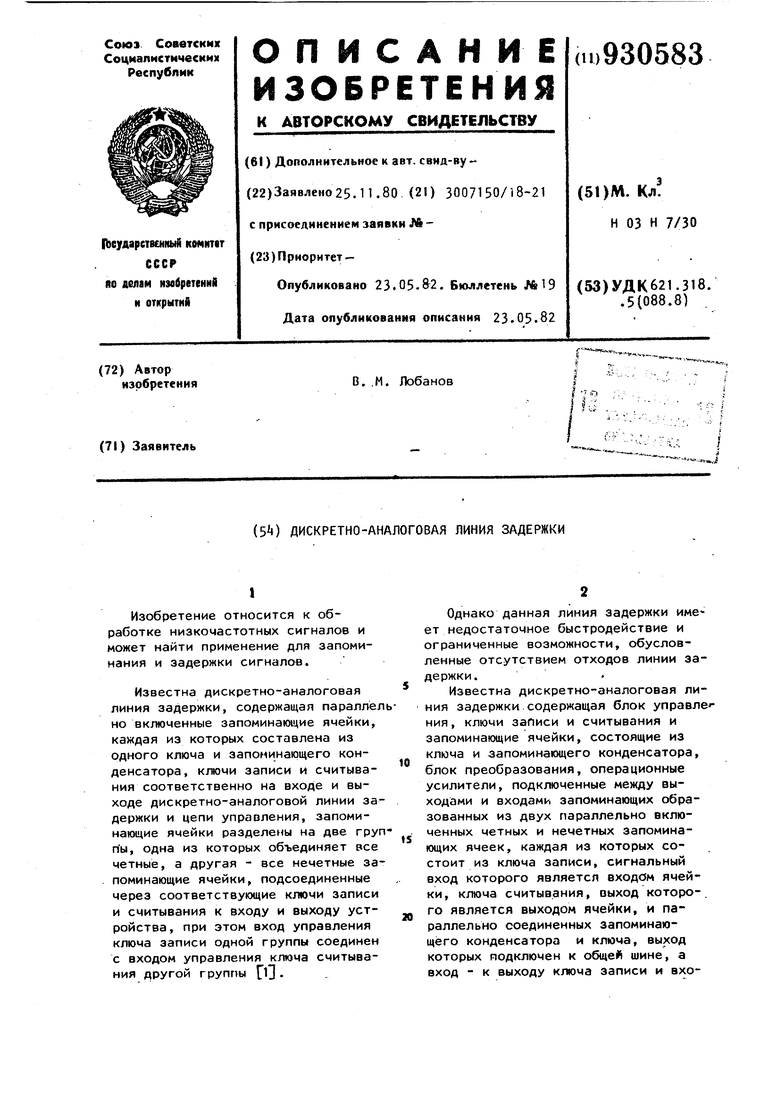

На фиг. 1 приведена функциональная электрическая схема дискретноаналоговой линии задержки с отводами; на фиг. 2 -диаграммы, поясняющие работу устройства.

Линия задержки (фиг.1) содержит ключи записи t-1-l-n, устройство управления 2, запоминающие конденсаторы 3-1-3-п, ключи считывания , операционный усилитель 5, ключи восстановления 6-1-6-п, конденсаторы хранения 7-1-7-п, операционные усилители 8-1-8-п, выходы которых являются выходами линии задержки.

Вход соединен с входами ключей записи 1-1-1-п, выходы которых соединены с -входами конденсаторов хранения 3 1-3-п и входами ключей считывания -1-4-п соответственно. Выходы конденсаторов 3-1-3-п соединены с общей шиной. Выходы ключей стывания k- -lt-n соединены между соб и подключены ко входу операционного усилителя 5,.выход которого подключен ко входам ключей восстановления 6 -6-п, выходы которых подключены к входам ключей восстановления 6-1-6-п, выходы которых подключены к конденсаторам хранения 7-1-7-п и входам операционных усилителей 8-1-8-п, выходы операционных усилителей 8-1-8-п являются выходами отводов линии задержки. Входы управления ключей записи, ключей считыва.ния, ключей восстановления соединены с выходами устройства управления 2..

Линия задержки работает следующим образом.

При поступлении импульса на вход управления ключа записи 1-1 значение сигнала io записывается в запоминающий конденсатор 3-1. По окончании импульса записи открываются ключи считывания и ключи восстановления б-Т-б-. В результате значение сигнала Ugxзапишется в конденсатор хранения 7-1 и будет повторено на выходе в течение периода тактовой частоты операционным усилителем 8-1,,

Во время следующего периода тактовой частоты работы линии задержки открывается ключ записи 1-2, значение сигналазаписывается в запоми нающий конденсатор 3-2, а последовательность, импульсов управления кл чамиI считывания и ключами восстанов ления установит следующее состояние выходов линии задержки: в конденсатор хранения 7-1 запишется значение сигнала, а в конденсатор хра7-2 - ulw. Во время следуюнениящего периода тактовой частоты откроется ключ записи 1-3 и ключи счи тывания и ключи восстановления согласно временной диаграмме. В резуль тате значение сигнала U будет хра ниться в конденсаторе , U конденсаторе , « конденсаторе 7-2, U,.- в конденсаторе 7-3. Во время следующего перио тактовой частоты в конденсатор хранения 7-1 запишется значение сигнала Ugx, в конденсатор хранения 7-2 Uax, в конденсатор хранения 7-3 и|, в конденсатор хранения 7-3 в конденсатор хранения 7- Далее линия задержки работает аналогично. Как видно из работы линии задерж ки, независимо от ее длины цепь про хождения электрических сигналов содержит 2 операционных усилителя, поэтому нестабильность выходного на пряжения п-го отвода & п-2 раза мень ше, чем в известном устройстве. Операционные усилители 5, 8-1-8-п являются повторителями напряжения с большим входным сопротивлением. Следует отметить, что на выходе операционного усилителя 5 входной сигнал уплотнен во времени, что поз воляет использовать данную линию за 3 держки в устройствах обработки сигналов с временным уплотнением. Формула изобретения Дискретно-аналоговая линия задермки, содержащая устройство управ ления, соединенное выходами с входами управлякядих ключей записи и ключей считывания,запоминающие конденсаторы, входы которых подк чены к выходам соответствуюцих им ключей записи и входам ключей считывания, а выходы конденсаторов подсоединены к общей шине,oneрационные усилители, выходы которых подключены к выходным клеммам, входы ключей записи соединены с входной клеммой устройства, отличаю 81 аяс я тем, что, с целью повышения стабильности и расширения функциональных возможностей , в нее введены операционный усилитель, ключи восстановления, кой денсаторы хра|нения, примем вход введенного операционйого усиления соединен с выходами всех ключей считывания, а его выход - с входами всех ключей восстановления, выходы которых соединены с входами соответствующих .им конденсаторов хранения и входами операционных усилителей,вы-: ходы конденсаторов соединены с обцей шиной, входы управления к;в6мей восстановления соединены с выходами yetройства управления, а входы всех ключей записи соединены между собой. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 50315, кл. Н 03,Н 7/30, 05.0.7. 2.Авторское свидетельство СССР N 665393, кл. Н 03 Н 7/30, 06.12.76 (прототип).

n

n

n

Д

я

я

я

п п

я

л

K.C.fi

n

n

IIо.

я

я

ла

я

я

лп

я

Авторы

Даты

1982-05-23—Публикация

1980-11-25—Подача