запоминающих ячеек - к первому и второму выходам блока управления, управляющие входы ключей считывания нечетных запоминающих ячеек - к третьему и четвертому выходам блока управления.

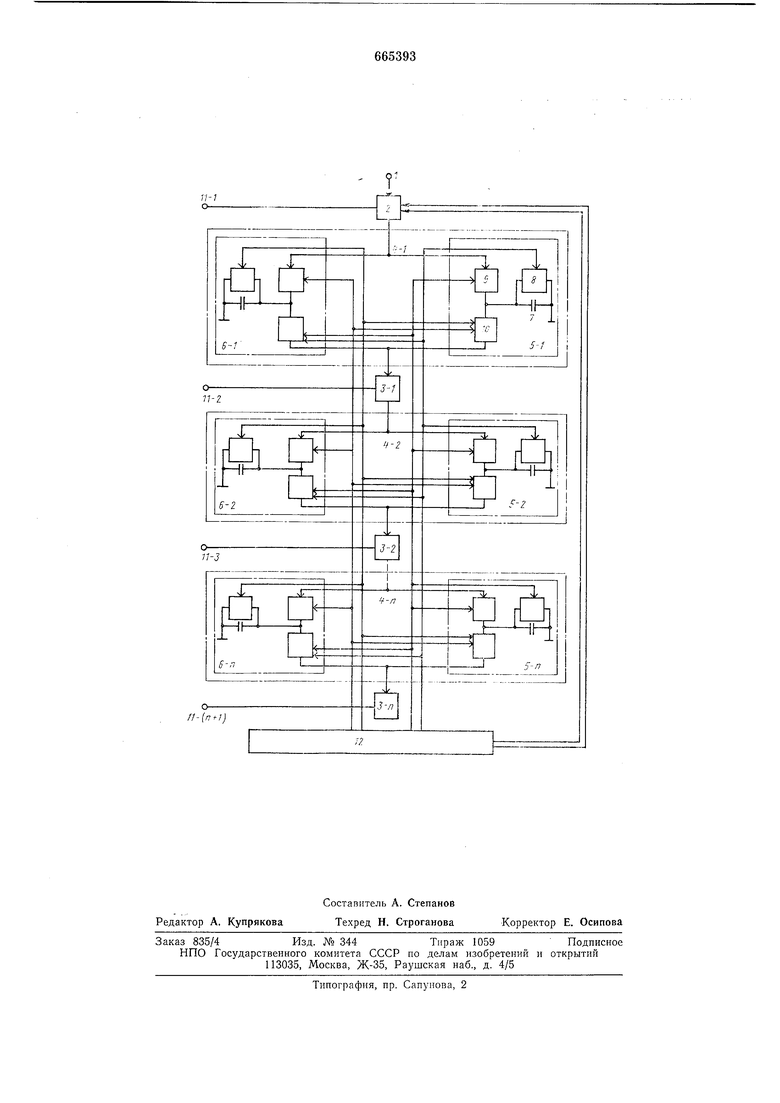

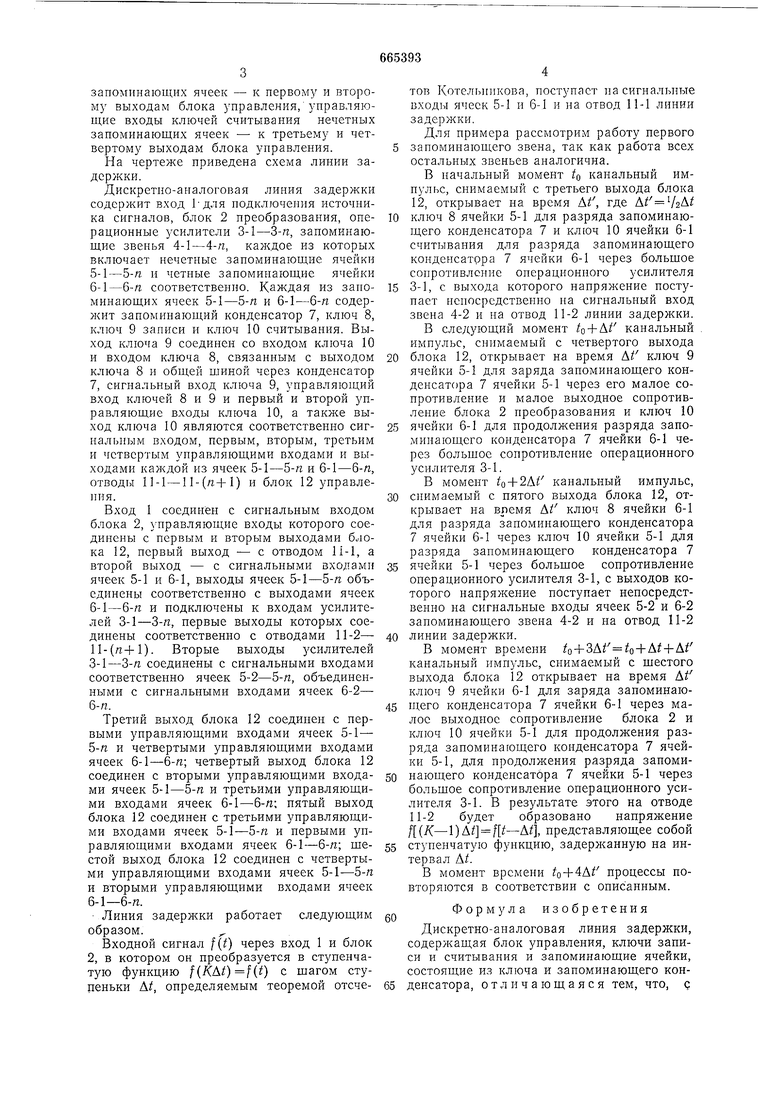

На чертеже приведена схема линии задержки.

Дискретно-аналоговая линия задержки содержит вход 1-для подключения источника сигналов, блок 2 преобразования, операционные зсилители 3-1-3-п, запоминающие звенья 4-1-4-л, каждое из которых включает нечетные запоминающие ячейки 5-1-5-л и четные запомипающие ячейки 6-1-6-/г соответственно. Каждая из запоминающих ячеек 5-1-5-л и 6-1-6-л содержит запоминающий конденсатор 7, ключ 8, ключ 9 записи и ключ 10 считывания. Выход ключа 9 соединен со входом ключа 10 и входом ключа 8, связанным с выходом ключа 8 и общей щиной через конденсатор 7, сигнальный вход ключа 9, управляющий вход ключей 8 и 9 и первый и второй управляющие входы ключа 10, а также выход ключа 10 являются соответственно сигнальным входом, первым, вторым, третьим и четвертым управляющими входами и выходами каждой из ячеек 5-1-5-л и 6-1-6-л, отводы 11-1-11-(л+1) и блок 12 управления.

Вход 1 соединен с сигнальным входом блока 2, управляющие входы которого соединены с первым и вторым выходами блока 12, первый выход - с отводом li-1, а второй выход - с сигнальными входами ячеек 5-1 и 6-1, выходы ячеек 5-1-5-л объединены соответственно с выходами ячеек 6-1-6-л и подключены к входам усилителей 3-1-3-л, первые выходы которых соединены соответственно с отводами 11-2- 11-(л+1). Вторые выходы зсилителей 3-1-3-л соединены с сигнальными входами соответственно ячеек 5-2-5-л, объединенными с сигнальными входами ячеек 6-2- 6-л.

Третий выход блока 12 соединен с первыми управляющими входами ячеек 5-1-- 5-л и четвертыми управляющими входами ячеек 6-1-6-«; четвертый выход блока 12 соединен с вторыми управляющими входами ячеек 5-1-5-л и третьими управляющими входами ячеек 6-1-6-л; пятый выход блока 12 соединен с третьими управляющими входами ячеек 5-1-5-л и первыми управляющими входами ячеек 6-1-6-л; щестой выход блока 12 соединен с четвертыми управляющими входами ячеек 5-1-5-л и вторыми управляющими входами ячеек 6-1-6-л.

- Линия задержки работает следующим образом.

Входной сигнал f(t} через вход 1 и блок 2, в котором он преобразуется в ступенчатую функцию f(K&.t)f(t) с щагом ступеньки Аг, определяемым теоремой отсчетов Котельникова, поступает на сигнальные входы ячеек 5-1 и 6-1 и на отвод 11-1 линии задержки.

Для примера рассмотрим работу первого 5 запоминающего звена, так как работа всех остальных звеньев аналогична.

В начальный момент to канальный имнульс, снимаемый с третьего выхода блока 12, открывает иа время , где M -

10 ключ 8 ячейки 5-1 для разряда запоминающего конденсатора 7 и ключ 10 ячейки 6-1 считывания для разряда запоминающего конденсатора 7 ячейки 6-1 через больщое соиротивлсние операционного усилителя

5 3-1, с выхода которого напряжение поступает непосредственно на сигнальный вход звена 4-2 и на отвод 11-2 линии задержки. В следующий момент /о + А/ канальный импульс, снимаемый с четвертого выхода

0 блока 12, открывает на время Af ключ 9 ячейки 5-1 для заряда запоминающего конденсатора 7 ячейки 5-1 через его малое сопротивление и малое выходное сопротивление блока 2 преобразования и ключ 10

5 ячейки 6-1 для продолжения разряда запоминающего конденсатора 7 ячейки 6-1 через больщое сопротивление операционного усилителя 3-1. В момент /о + канальный импульс,

0 снимаемый с пятого выхода блока 12, открывает на впемя ключ 8 ячейки 6-1 для разряда запоминающего конденсатора 7 ячейки 6-1 через ключ 10 ячейки 5-1 для разряда запоминающего конденсатора 7

5 ячейки 5-1 через больщое сопротивление операционного усилителя 3-1, с выходов которого напряжение поступает непосредственно на сигнальные входы ячеек 5-2 и 6-2 запоминающего звена 4-2 и иа отвод 11-2

0 линии задержки.

В момент времени o-f канальный импульс, снимаемый с щестого выхода блока 12 открывает иа время Ai ключ 9 ячейки 6-1 для заряда запоминающего конденсатора 7 ячейки 6-1 через малое выходное сопротивление блока 2 и ключ 10 ячейки 5-1 для продолжения разряда запоминающего конденсатора 7 ячейки 5-1, для продолжения разряда запоминающего конденсатбра 7 ячейки 5-1 через больщое сопротивление операционного усилителя 3-1. В результате этого на отводе 11-2 будет образовано напряжение Ж/С-l)A/ , представляющее собой

5 стуиенчатую функцию, задержанную на интервал .

В момент времени /о + 4А/ процессы повторяются в соответствии с описанным.

Формула изобретения

Дискретно-аналоговая линия задержки, содержащая блок управления, ключи записи и считывания и запоминающие ячейки, состоящие из ключа и запоминающего конденсатора, отличающаяся тем, что, с

целью повышения быстродействия и расширения функциональных возможностей, в нее введены блок преобразования, операционные усилители, подключенные между выходами и входами запоминаюших звеньев, образованных из двух параллельно включенных четных и нечетных запоминаюш;их ячеек, каждая из которых состоит из ключа записи, сигнальный вход которого является входом ячейки, ключа считывания, выход которого является выходом ячейки, и параллельно соединенных запоминающего конденсатора и ключа, выход которых подключен к общей шине, а вход - к выходу ключа записи и входу ключа считывания, при этом блок преобразования подключен своим сигналом входом к источнику сигналов, выходом - к входу первого запоминающего звена, дополнительным выходом - к нулевому отводу линии задержки и управляющими входами - к дополнительным выходам блока управления, а

дополнительные выходы всех операционных усилителей - к соответствующим отводам линии задержки, управляющие входы ключей четных и нечетных запоминающих ячеек подсоединены соответственно к третьему и первому выходам блока управления, управляющие входы ключей записи четных и нечетных запоминающих ячеек - соответственно к четвертому и второму выходам

блока управления, управляющие входы ключей считывания четных запоминающих ячеек - к первому и второму выходам блока управления, управляющие входы ключей считывания нечетных запоминающих ячеек - к третьему и четвертому выходам блока управления.

Источники информации, принятые во внимание при экспертизе 1 Авторское свидетельство СССР

№ 369693, кл. Н ОЗН 17/28, 1971.

2. Авторское свидетельство СССР № 450315, кл. Н ОЗН 7/30, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Дискретно-аналоговая линия задержки | 1980 |

|

SU930583A1 |

| Устройство для задержки импульсных сигналов | 1980 |

|

SU921047A1 |

| ВЫСОКОПАРАЛЛЕЛЬНЫЙ СПЕЦПРОЦЕССОР ДЛЯ РЕШЕНИЯ ЗАДАЧ О ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 1993 |

|

RU2074415C1 |

| Нерекурсивный фильтр | 1988 |

|

SU1580530A1 |

| Нерекурсивный фильтр | 1982 |

|

SU1107290A1 |

| Устройство для регулирования передачи данных | 1975 |

|

SU595872A1 |

| Линия задержки | 1982 |

|

SU1102022A1 |

| Система связи | 1989 |

|

SU1815802A1 |

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

Авторы

Даты

1979-05-30—Публикация

1976-12-06—Подача